文章目录

- 4.3.1 编码器

- 4.3.2 译码器

- 4.3.3 数据选择器

- 4.3.4 加法器

- 4.3.5 数值比较器

- 4.4 组合逻辑电路中的竞争-冒险现象

- 4.4.1 竞争-冒险现象及成因

- 4.4.3 消除竞争-冒险现象的方法

4.3.1 编码器

编码:为了区分一系列不同的事物,将其中的每个事物用一个二值代码表示。

编码器:将输入的每个高/低电平信号变成一个对应的二进制代码

普通编码器:

特点:任何时刻只允许输入一个编码信号。

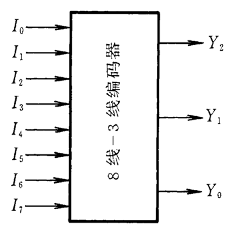

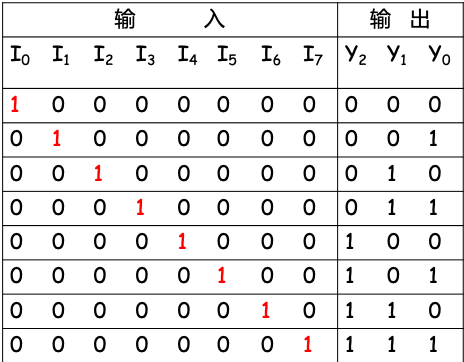

例:3位二进制普通编码器

优先编码器:

特点:允许同时输入两个以上的编码信号,但只对其中优先权最高的一个进行编码。

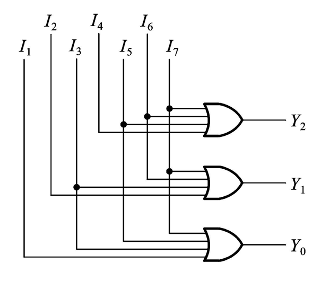

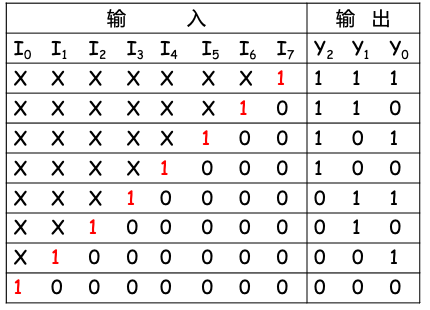

例:8线-3线优先编码器

设 I 7 I_7 I7 优先权最高, I 0 I_0 I0 优先权最低

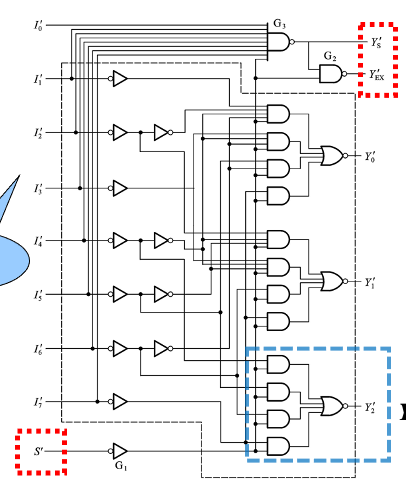

实例:74HC148

这里的 S ′ S' S′代表是低电平输出,并且为选通信号。如果S为0,那就表示可通,为1表示不通。

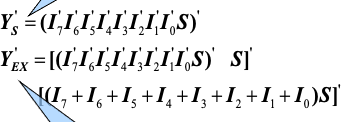

Y S ′ Y_S' YS′和 Y E X ′ Y_EX' YEX′为附加输出信号,当 Y S ′ Y_S' YS′为0时,电路工作无编码输入, Y E X ′ Y_EX' YEX′为0时,电路工作有编码输入。

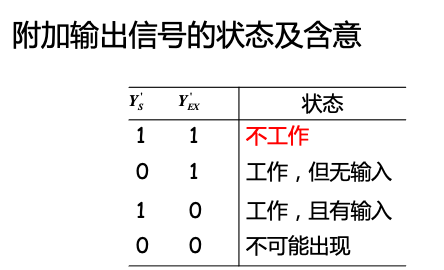

使用控制端可以扩展功能:

使用两片8线-3线优先编码器

可以变成16线-4线优先编码器

此时 A 15 ′ A_{15}' A15′的优先权最高

1.框图内部只标注输入、输出原变量.

2.低有效时,框图外部相应输入、输出端加画小圆圈,并在外部标注的信号名称加非号“ ’ ”

3.第一片为高优先权,只有(1)无编码输入时,(2)才允许工作

4.第(1)片 Y E X ′ = 0 Y_{EX}'=0 YEX′=0时表示对 A 15 ′ A_{15}' A15′~ A 8 ′ A_{8}' A8′的编码

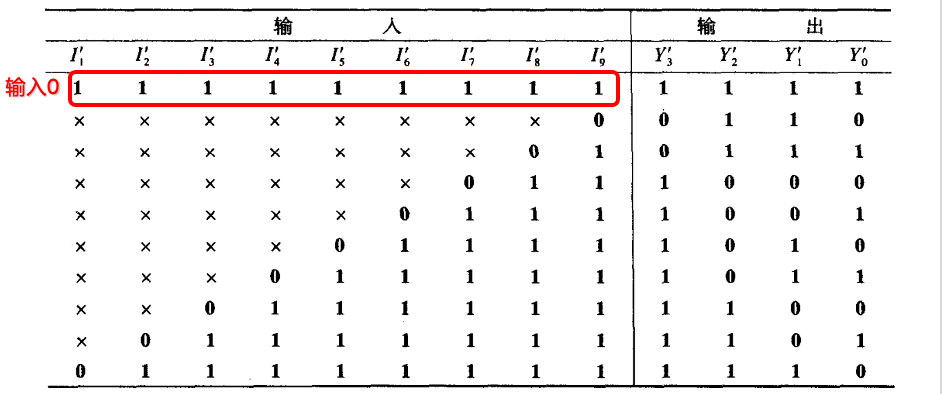

二-十进制优先编码器(74LS147)

将 I 0 ′ I_0' I0′~ I 9 ′ I_9' I9′编成10个BCD码

I 9 ′ I_9' I9′的优先权最高, I 0 ′ I_0' I0′最低

输入的低电平信号变成一个对应的十进制的编码

注意输入全1时代表输入为0

4.3.2 译码器

译码:将每个输入的二进制代码译成对应的输出高、低电平信号。

常用的有:二进制译码器、二-十进制译码器,显示译码器等。

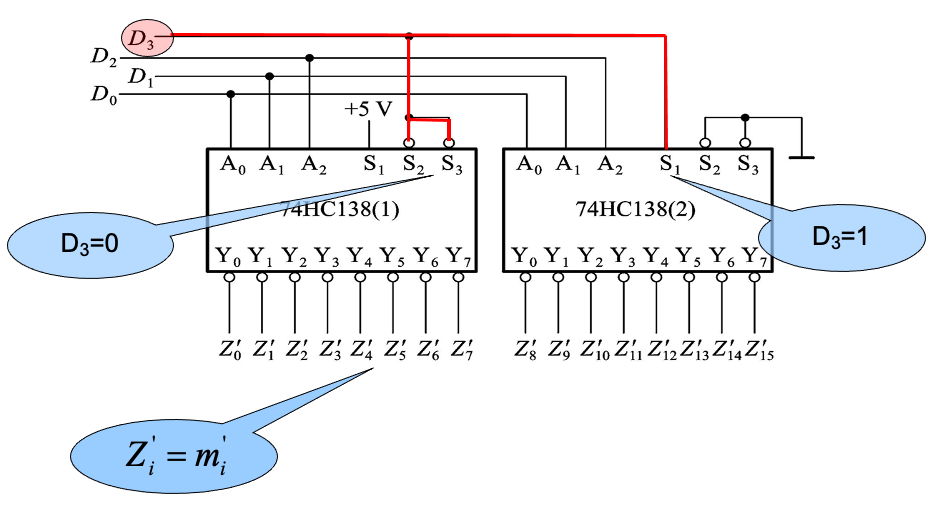

例:利用附加控制端进行扩展

74HC138

若D3=0 则(1)启动,D3=1,则(2)启动

用译码器设计组合逻辑电路

基本原理:

n位二进制译码器给出n变量的全部最小项,因此可以获得任何形式的输入变量不大于n的组合函数。

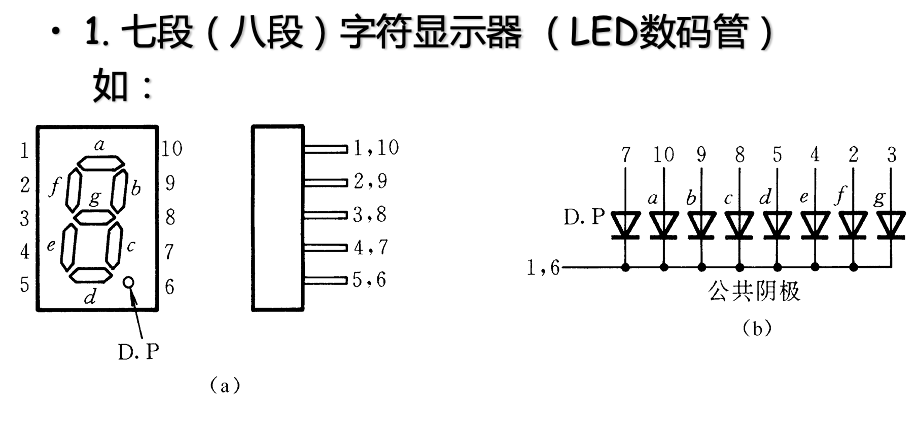

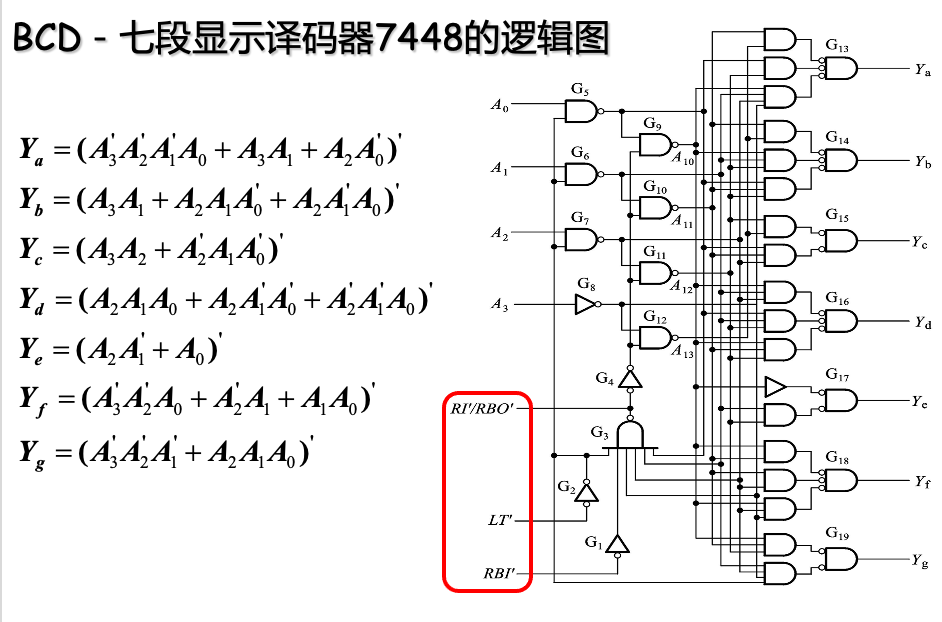

显示译码器

1.七段(八段)字符显示器(LED数码管)

灯测试输入 L T ′ LT' LT′

当 L T ′ = 0 LT'=0 LT′=0时, Y a Y_a Ya- Y g Y_g Yg全部置为1

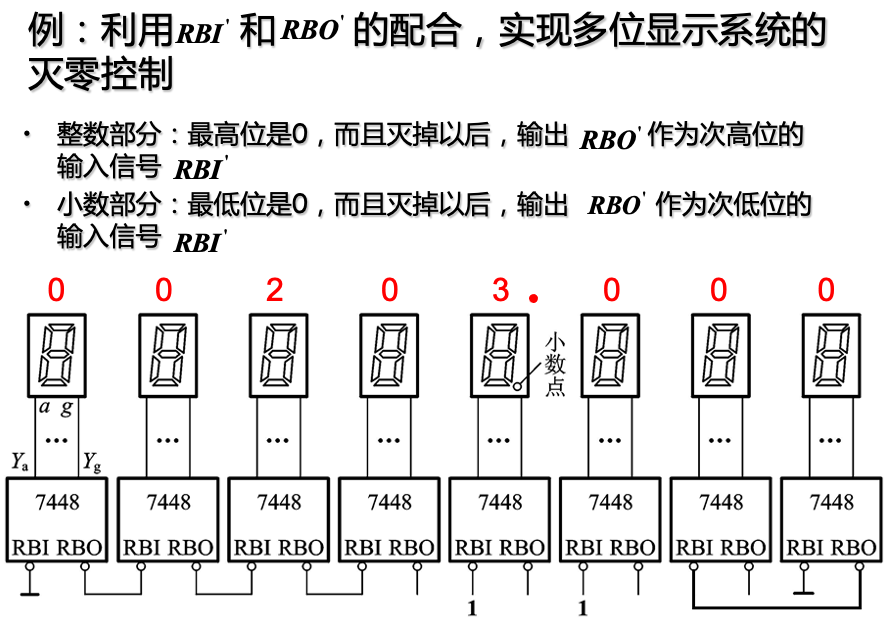

灭零输入 R B I ′ RBI' RBI′

当 A 3 A 2 A 1 A 0 = 0000 A_3A_2A_1A_0=0000 A3A2A1A0=0000时, R B I ′ = 0 RBI'=0 RBI′=0时,则灭灯

灭灯输入/灭零输出 B I ′ / R B O ′ BI'/RBO' BI′/RBO′

输入信号,称灭灯输入控制端:

B I ′ = 0 BI'=0 BI′=0 无论输入状态是什么,数码管熄灭

输出信号,称灭零输出端:

只有当输入 A 3 A 2 A 1 A 0 = 0000 A_3A_2A_1A_0=0000 A3A2A1A0=0000 且灭零输入信号 R B I ′ = 0 RBI'=0 RBI′=0时, R B O ′ RBO' RBO′才给出低电平

因此 R B O ′ = 0 RBO'=0 RBO′=0表示译码器将本来应该显示的零熄灭了

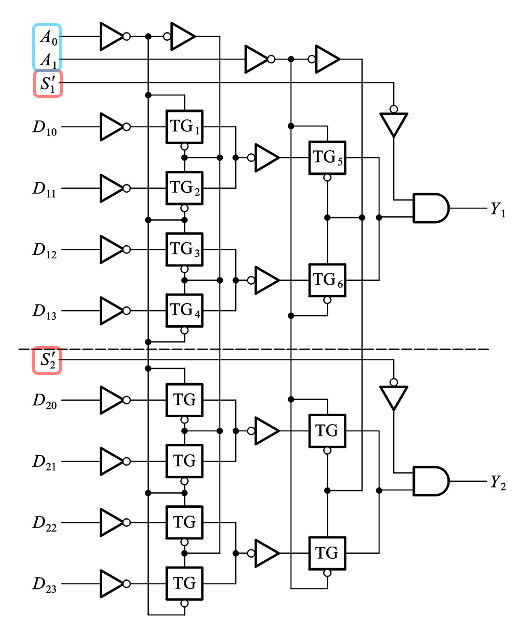

4.3.3 数据选择器

只取其中的一位输出

4.3.4 加法器

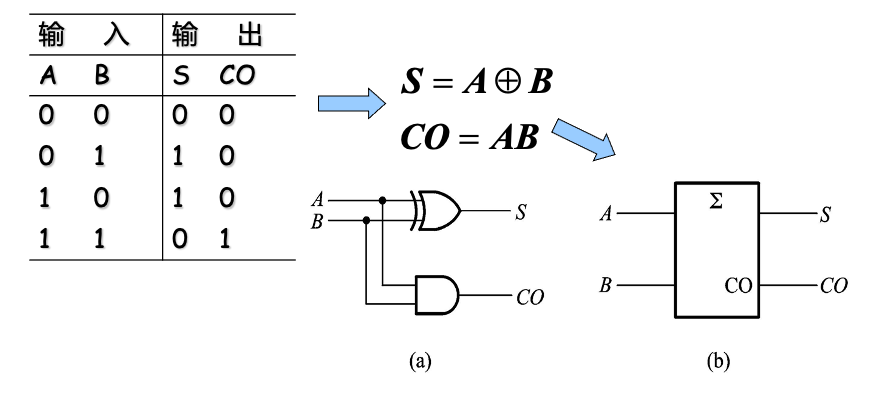

一、1位加法器

1.半加器,不考虑来自低位的进位,将两个1位的二进制数相加。

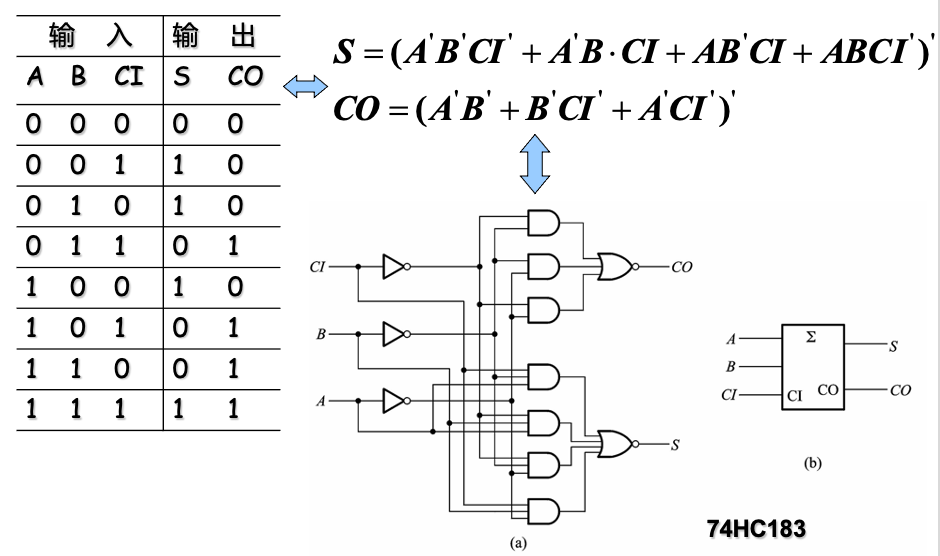

2.全加器:将两个1位的二进制数及来自低位的进位相加

二、多位加法器

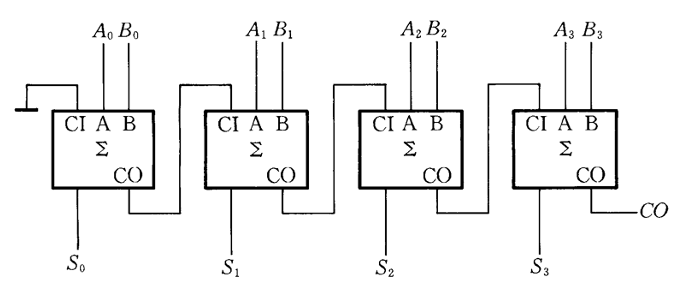

1.串行进位加法器

优点:简单

缺点:慢

2.超前进位加法器

加到第i位的进位输入信号是两个加数第i位以前各位(0~i-1)的函数,可在相加前由A,B两数确定。

优点:快,每1位的和及最后的进位基本同时产生

缺点:电路复杂

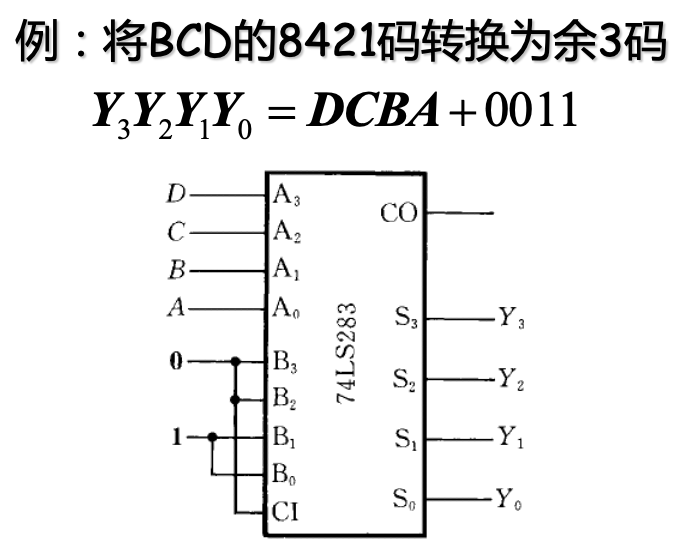

三、用加法器设计组合电路

基本原理:若能生成函数可变换成输入变量与输入变量相加,或输入变量与常量相加

4.3.5 数值比较器

用来比较两个二进制数的数值大小

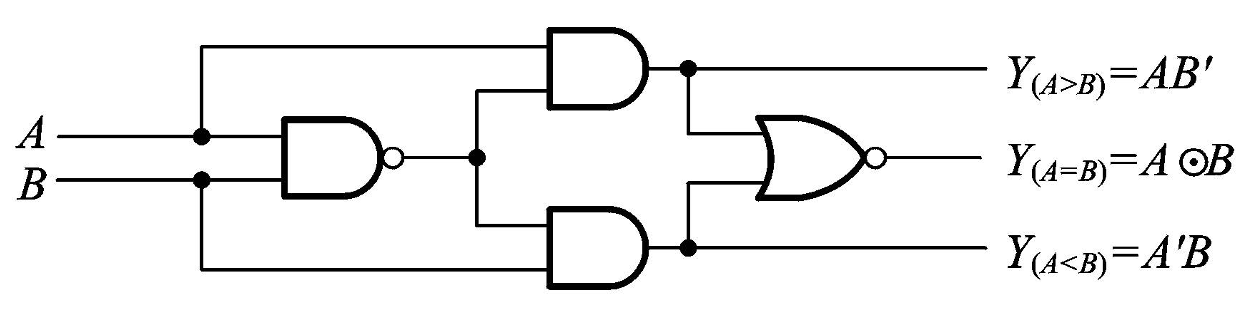

一、1位数值比较器

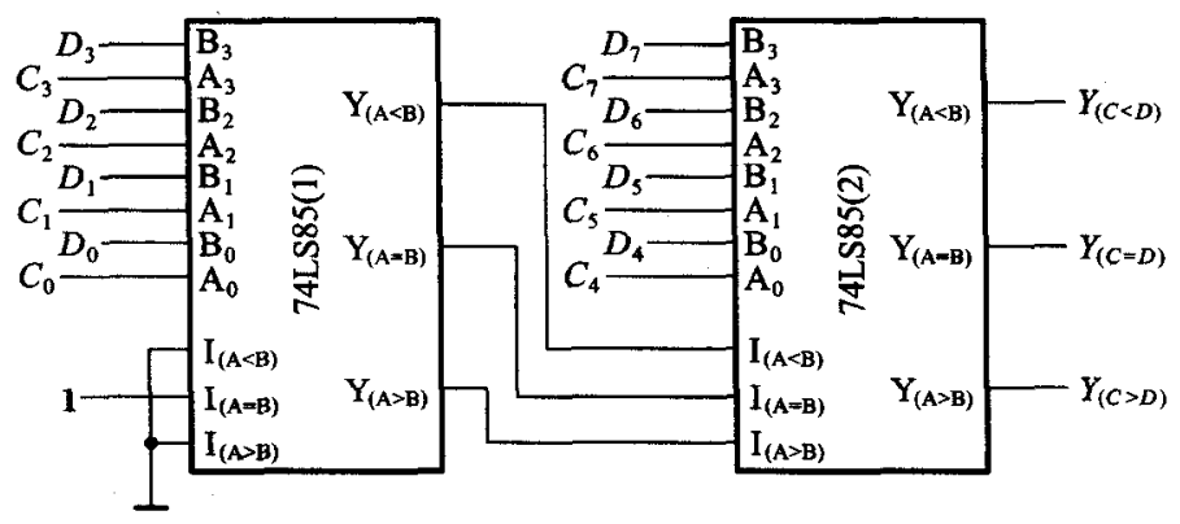

二、多位数值比较器

原理:从高位比起,只有高位相等,才比较下一位。

例:比较两个8位二进制数的大小

其中,(2)中的来自(1)结果的3个I,代表着来自低位的比较结果。

4.4 组合逻辑电路中的竞争-冒险现象

4.4.1 竞争-冒险现象及成因

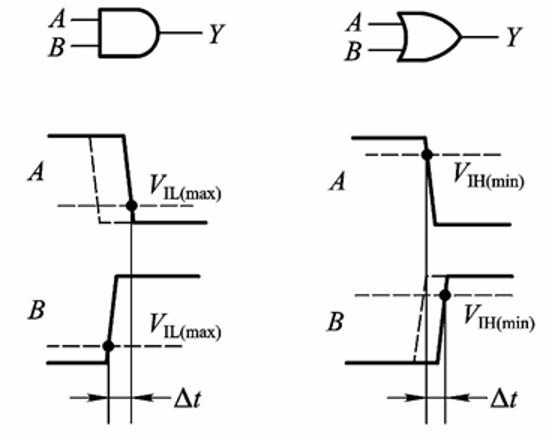

什么是竞争:两个输入同时向相反的逻辑电平变化,称存在竞争。

因竞争而可能在输出产生尖峰脉冲的现象,称为竞争-冒险。

4.4.3 消除竞争-冒险现象的方法

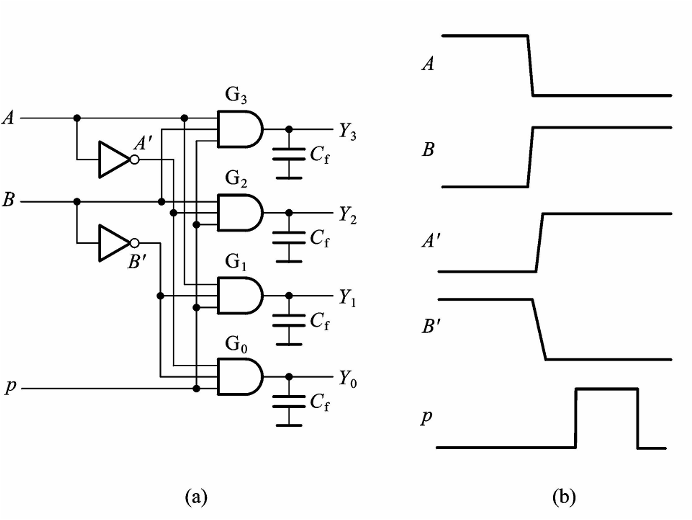

一、接入滤波电容:如果尖峰脉冲很窄,可以用很小的电容把尖峰削弱到 V T H V_{TH} VTH以下

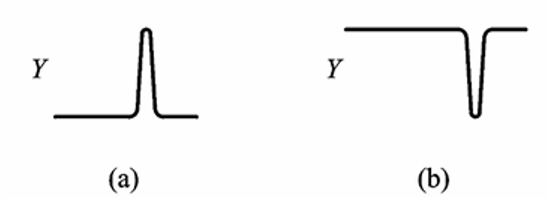

二、引入选通脉冲P:取选通脉冲作用时间,在电路达到稳定之后,P的高电平期的输出信号不会出现尖峰。

不稳定的时候,P直接好家伙取0,强制让输出端稳定,知道稳定了后再取1,输出端也就稳定了

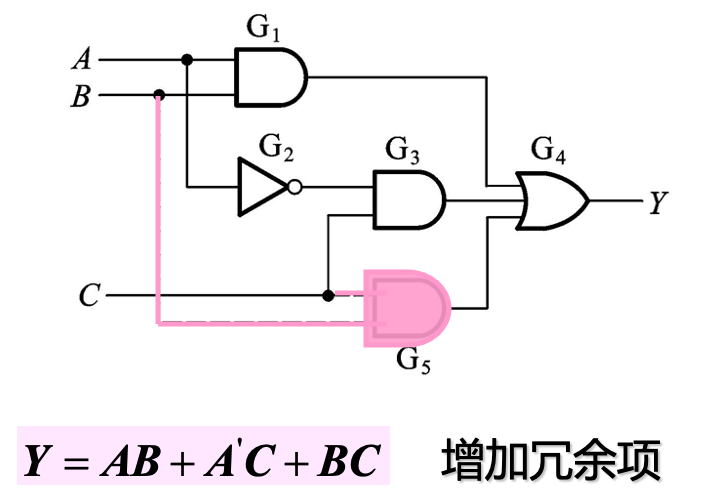

三、修改逻辑设计

最后

以上就是清秀羊最近收集整理的关于数字电路 常用组合逻辑电路的全部内容,更多相关数字电路内容请搜索靠谱客的其他文章。

发表评论 取消回复