目录

实验目的

实验预习

实验原理

设计要求

实验任务一

语法知识点1:不同抽象级别的Verilog HDL模型

1 、Verilog HDL具有行为描述和结构描述功能

2 、数字电路系统设计(以正弦信号发生器为例说明)

语法知识点2:assign连续赋值语句(数据流描述方式)

实验任务二

实验任务三:硬件验证频率计的功能。

实验总结与分析

实验目的

设计8位16进制频率计,学习较复杂的数字系统设计方法。

实验预习

复习计数器和寄存器的设计。

实验原理

(1)频率计的功能是什么?(测量频率的仪器)

(2)频率计前面的定语“8位16进制”限定了什么?(频率计的测频范围)

根据频率的定义和频率测量的基本原理,测定信号的频率必须有一个脉宽为1秒的输入信号作为脉冲计数允许的信号。1秒计数结束后,计数值将被锁入锁存器,计数器清零,为下一次测频计数周期作好准备。

设计要求

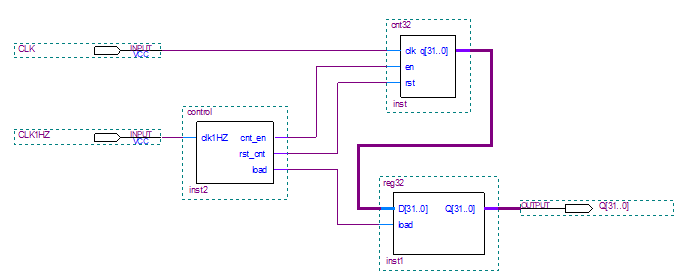

如图1所示为8位16进制频率计原理图。

其中控制器control的计数使能信号cnt_en产生一个1秒脉宽的周期信号,并对频率计中的32位二进制计数器cnt32的en使能端进行同步控制。当en为高电平时允许计数;低电平时停止计数,并保持所计的脉冲数。在停止计数期间,首先需要一个锁存信号load的上跳沿将计数器在前1秒钟的计数值锁存进锁存器reg32中,并由外部的十六进制七段译码器译出,显示计数值。设置锁存器的好处是数据显示稳定,不会由于周期性的清0信号而不断闪烁。锁存信号后,必须有一清0信号rst_cnt对计数器进行清零,为下一秒的计数操作作准备。

本设计需要一个32位的计数器,该计数器有一个1秒的计数使能信号,还有一个清零信号,该清零信号在两个计数使能信号中间的某一时间段产生。需要一个32位的锁存器,在计数结束之后,将计数值立即进行锁存。需要一个控制电路,用来产生计数器的计数使能信号、清零信号和锁存器的锁存信号。三个模块之间的连接关系如图1所示。

实验任务一

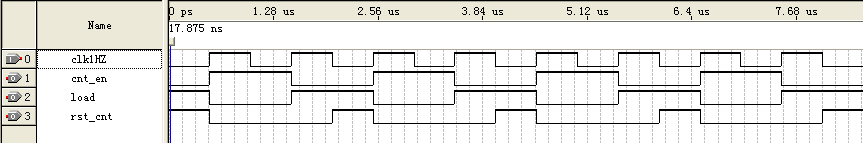

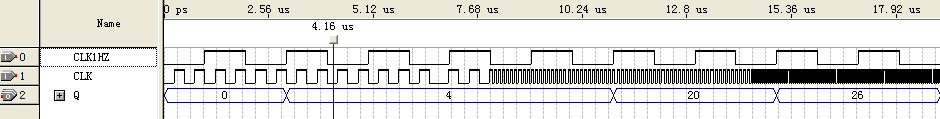

根据图2所示的波形,设计频率计的控制模块,并对设计中的各语句功能、设计原理及逻辑功能进行详细的描述。

控制器的参考代码:

module control(clk1HZ,cnt_en,rst_cnt,load);

input clk1HZ;

output cnt_en,rst_cnt,load;

reg divclk;

always@(posedge clk1HZ)

divclk<=~divclk;

assign cnt_en=divclk;

assign load=~divclk;

assign rst_cnt=~clk1HZ & ~divclk;

endmodule语法知识点1:不同抽象级别的Verilog HDL模型

1 、Verilog HDL具有行为描述和结构描述功能

行为描述是对设计电路的逻辑功能的描述,并不关心设计电路使用那些元件以及这些元件之间的连接关系。行为描述属于高层次的描述方法,在Verilog HDL中,行为描述包括系统级(System Level)、算法级(Algorithm Level)和寄存器传输级(RTL:Register Transfer Level)等3种抽象级别。应重点掌握行为描述方法。

结构描述是对设计电路的结构进行描述,即描述设计电路使用的元件及这些元件之间的连接关系。结构描述属于低层次的描述方法,在Verilog HDL,结构描述包括门级(Gate Level)和开关级(Switch Level)2种抽象级别。

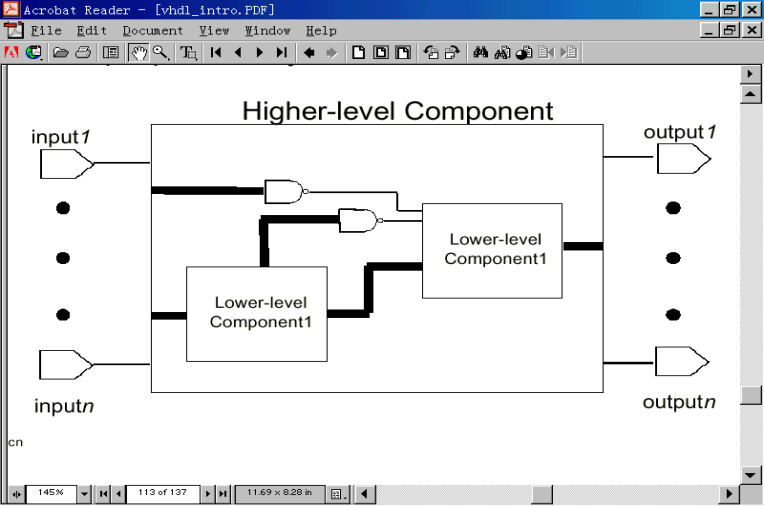

对于一个实际的数字系统电路,一般先用行为描述方法设计底层模块电路,最后用结构描述方法将各模块连接起来,构成顶层文件完成系统电路的设计。

2 、数字电路系统设计(以正弦信号发生器为例说明)

方法一:用原理图的方法实现数字电路系统设计,如图所示。

举例:如图所示为正弦信号发生器的数字系统设计。

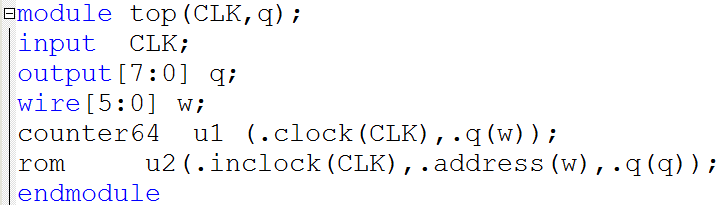

方法二:用模块例化语句实现数字电路系统设计。

模块例化语句格式:

设计模块名 <例化电路名>(端口列表);

例化电路名:用户为系统设计定义的标识符,相当系统电路板上插入设计模块元件的插座

端口列表:相当插座上引脚名表,应与设计模块的I/O端口一一对应。

下面源代码是正弦信号发生器的数字系统设计。

语法知识点2:assign连续赋值语句(数据流描述方式)

assign连续赋值语句描述输入、输出之间的逻辑关系,其格式为:

assign 目标变量名=驱动表达式

目标变量名必须为wire型变量;综合器默认输入输出端口为wire型变量。如果目标变量名需要有端口以外的变量,必须用网线型变量定义语句事先作出定义。网线型变量定义语句格式为:

wire [width-1:0] 变量1,变量2……;

assign连续赋值语句为并行语句,可以和always@语句相互转化表达。其执行过程为:等式右侧的驱动表达式中的任一信号发生变化,此表达式即被计算一遍,并将获得的数据立即赋给等式左侧的目标变量。

同一目标变量不允许有多个不同赋值表达式,或者说wire型变量不允许有多个驱动源。例如:

assign dout=a&b|c;

assign dout=e&f|d;

上述表达方式是不对的。

assign语句主要用于描述组合电路,但如果信号有反馈,也会构成时序电路。

实验任务二

完成频率计的完整设计,并给出其测频时序波形及其分析。

32位二进制计数器的参考代码:

module cnt32(clk,en,rst,q);

input clk,en,rst;

output reg[31:0] q;

always@(posedge clk or posedge rst)

begin

if(rst) q<=0;

else if(en) q<=q+1;

end

endmodule32位锁存器的参考代码:

module reg32(D,Q,load);

input[31:0] D;

input load;

output reg[31:0] Q;

always@(posedge load)

Q<=D;

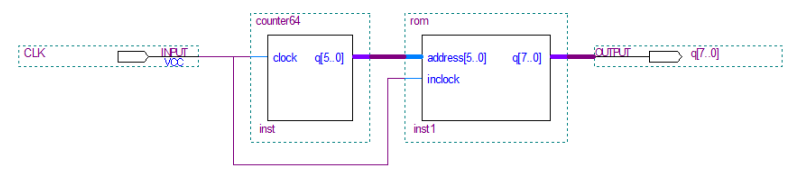

endmodule8位16进制频率计整体设计如图所示,其仿真波形如图5所示:

注意:该设计中包括4个文件,分别为底层设计控制器control.v、计数器cnt32.v、锁存器reg32.v和顶层设计frequency.bdf,一定要确保这四个文件在同一个文件夹中,且文件夹不嵌套。

实验任务三:硬件验证频率计的功能。

建议选实验电路模式5验证频率计的功能,其中8个数码管以十六进制形式显示测频输出;待测频率输入FIN由clock0输入,频率可选4Hz、 256Hz、 3MHz‥‥‥50MHz等;1Hz测频控制信号CLK1Hz可由clock2输入(用跳线选1Hz)。编译下载后进行硬件测试。

实验总结与分析

最后

以上就是谦让羊最近收集整理的关于EDA(Quartus II)——8位16进制频率计设计实验目的实验预习实验原理设计要求实验任务一实验任务二实验任务三:硬件验证频率计的功能。实验总结与分析的全部内容,更多相关EDA(Quartus内容请搜索靠谱客的其他文章。

发表评论 取消回复