目录

一、SR 锁存器(保持电路状态,具备记忆功能)

1、SR 锁存器工作原理

2、SR锁存器的真值表

3、SR 触发器的特性方程

二、触发器

1、电平触发的触发器

2、 电平触发的D触发器——D型锁存器

3、边沿触发的触发器

3.1 电路结构和工作原理

3.2 边沿触发器的特性表

3.3 边沿触发方式的动作特点

4、脉冲触发的触发器

4.1 电路结构和工作原理

-

电平敏感的存储器件称为锁存器。可分为高电平锁存器和低电平锁存器,用于不同时钟之间的信号同步。

- 有交叉耦合的门构成的双稳态的存储原件称为触发器。分为上升沿触发和下降沿触发,可以认为是两个不同电平敏感的锁存器串连而成。前一个锁存器决定了触发器的建立时间,后一个锁存器则决定了保持时间。

一、SR 锁存器(保持电路状态,具备记忆功能)

SR 锁存器是各种触发器电路的基本构成部分。与触发器的区别之一是输出是由输入的置1或置0信号直接完成的,而不需要触发信号的触发。

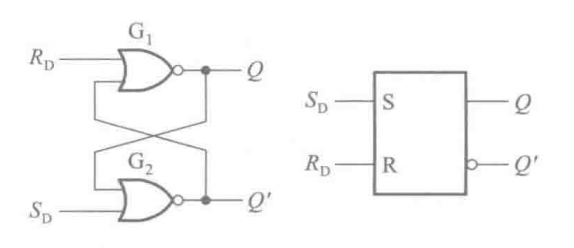

1、SR 锁存器工作原理

- 当

=1、

=0时,Q=1、Q'=0。在

=1信号消失以后(即

回到0),由于有Q端的高电平接回到 G2 的另一个输入端,因而电路的1状态得以保持。

- 当

=0、

=1时,Q=0、Q'=1。在

=1信号消失以后,电路保持0状态不变。

- 当

=

=0时,电路维持原来的状态不变。

- 当

=

=1时,Q=Q'=0,这既不是定义的 1状态,也不是定义的0状态。而且,在

和

同时回到0 以后无法断定锁存器将回到1状态还是0状态。

- 因此,在正常工作时输入信号应遵守

的约束条件,亦即不允许输入

的信号。

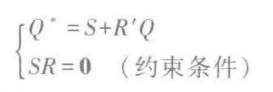

SR 锁存器也可以用与非门构成,如下图所示。这个电路是以低电平作为输入信号的,所以用和

,分别表示置1输入端和置0输入端。在右下图所示的图形符号上,用输入端的小圆圈表示用低电平作输入信号,或者称低电平有效。

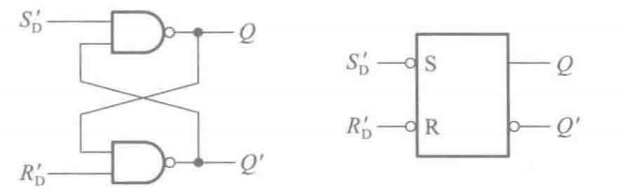

2、SR锁存器的真值表

表示输入变化之前的输出,

表示输入变化之后的输出

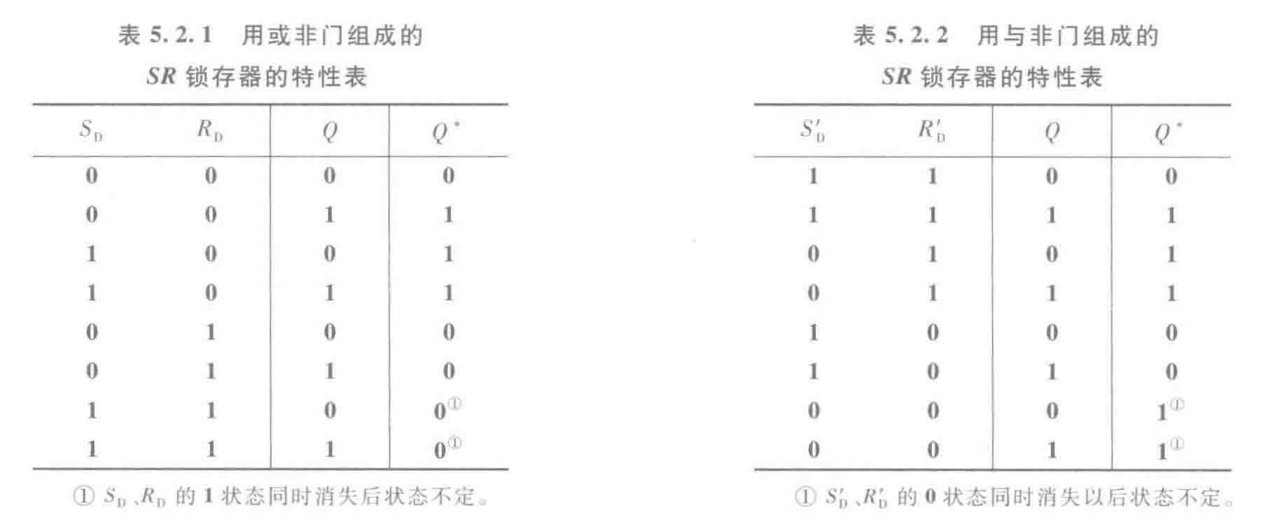

3、SR 触发器的特性方程

二、触发器

- 触发器与锁存器的不同在于,它除了置 1、置0输入端以外,又增加了一个触发信号输人端。只有当触发信号到来时,触发器才能按照输入的置 1、置0信号置成相应的状态,并保持下去。我们将这个触发信号称为时钟信号(CLOCK),记作 CLK。当系统中有多个触发器需要同时动作时,就可以用同一个时钟信号作为同步控制信号了。

- 触发信号的工作方式可以分为电平触发、边沿触发和脉冲触发三种。下面将会看到,在不同的触发方式下,触发器的动作过程各具有不同的动作特点。掌握这些动作特点,对于正确使用触发器是十分必要的。

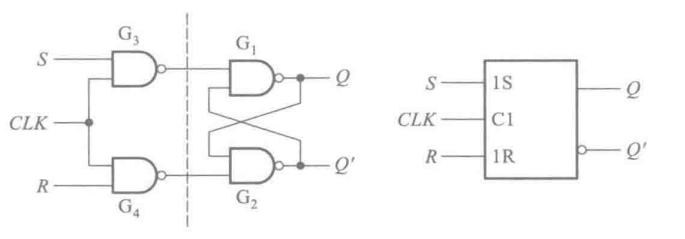

1、电平触发的触发器

电路结构:

由两部分组成:SR 锁存器(与非门G1、G2构成)+ 输入控制电路(两个与非门G3、G4构成)

工作原理:

- 由图可知,当 CLK=0时,门 G3、G4的输出始终停留在1状态,S、R 端的信号无法通过 G3、G4而影响输出状态,故输出保持原来的状态不变。

- 只有当触发信号 CLK 变成高电平以后,S、R 信号才能通过门G3、G4加到由门G1、G2组成的锁存器上,"触发"电路发生变化,使 Q 和 Q'根据 S、 R 信号而改变状态。因此,将 CLK 的这种控制方式称为电平触发方式。

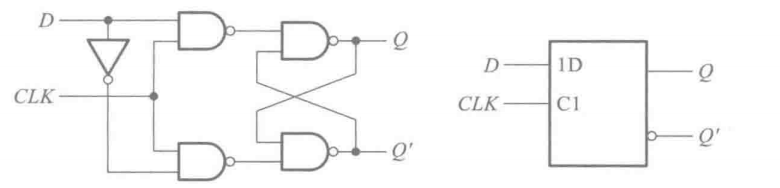

2、 电平触发的D触发器——D型锁存器

将上左图改接成下左图的形式,得到电平触发的D触发器(D型锁存器)

- 由图可见,若 D=1,则 CLK变为高电平以后触发器被置成 Q=1,CLK 回到低电平以后触发器保持1状态不变。

- 若 D=0,则 CLK 变为高电平以后触发器被置成 Q=0,CLK 回到低电平以后触发器保持0状态不变。因为它仍然工作在电平触发方式下,所以同样具有电平触发的动作特点。

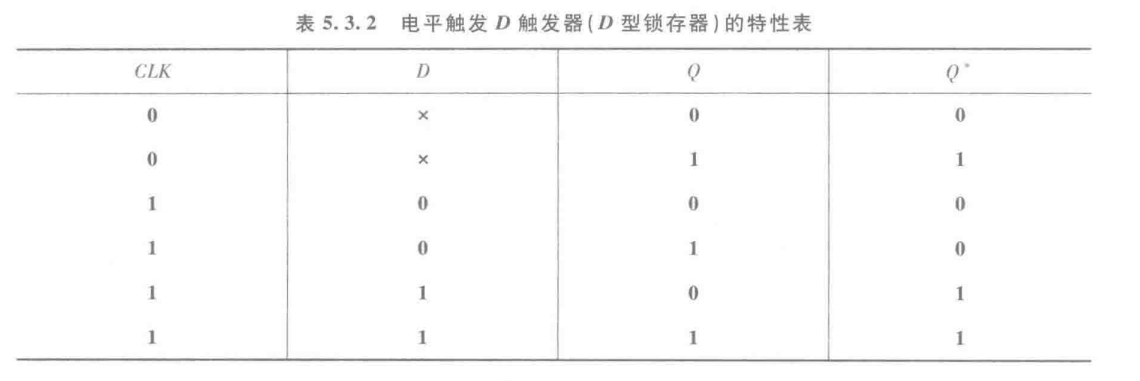

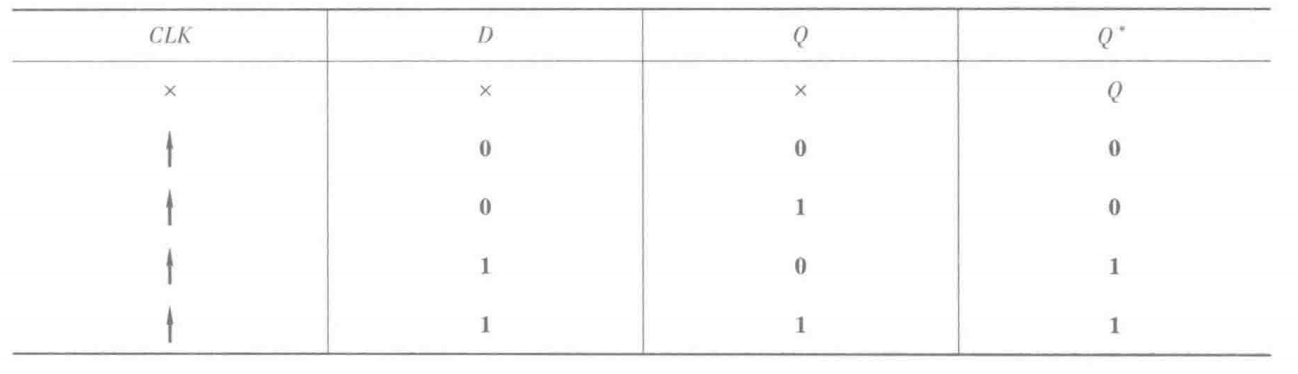

它的特性表如下表所示。

因为在 CLK 的有效电平期间输出状态始终跟随输入状态变化,输出与输入的状态保持相同,所以又将这个电路称为"透明的 D 型锁存器"(Transparent D-Latch)。

3、边沿触发的触发器

3.1 电路结构和工作原理

- 为了提高触发器的可靠性,增强抗干扰能力,希望触发器的次态仅仅取决于 CLK 信号下降沿(或上升沿)到达时刻输入信号的状态。而在此之前和之后输入状态的变化对触发器的次态没有影响。

- 为实现这一设想,人们相继研制成了各种边沿触发(edge-triggered)的触发器电路。目前已用于数字集成电路产品中的边沿触发器电路有:

- 用两个电平触发 D 触发器构成的边沿触发器、维持阻塞触发器、利用门电路传输延迟时间的边沿触发器等几种较为常见的电路结构形式。

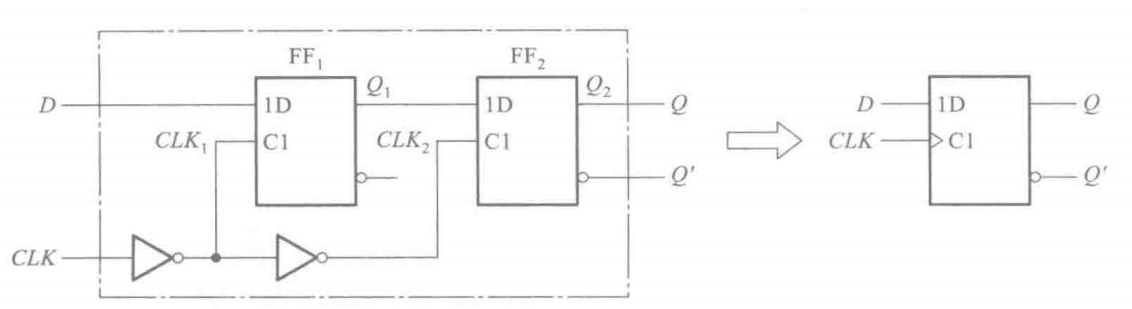

下图是用两个电平触发 D 触发器组成边沿触发 D 触发器的原理性框图,图中的 FF1和 FF2是两个电平触发的 D触发器(也称为D型锁存器)。

- 由图可见,当 CLK 处于低电平时:

- CLK1为高电平,因而 FF1的输出 Q1跟随输入端 D的状态变化,始终保持 Q1=D。

- 与此同时, CLK2为低电平,FF2的输出 Q2(也就是整个电路最后的输出 Q)保持原来的状态不变。

- 当 CLK由低电平跳变至高电平:

- CLK1随之变成了低电平,于是 Q1保持为 CLK 上升沿到达前瞬间输入端 D的状态,此后不再跟随 D的状态而改变。

- 与此同时,CLK2跳变为高电平,使 Q2与它的输入状态相同。由于 FF2的输入就是FF1的输出 Q1,所以输出端 Q便被置成了与CLK 上升沿到达前瞬时 D 端相同的状态,而与以前和以后 D 端的状态无关。

3.2 边沿触发器的特性表

在图形符号中,用 CLK输入端处框内的">"表示触发器为边沿触发方式。在特性表中,则用 CLK 一栏里的"↑"表示边沿触发方式,而且是上升沿触发,如下表所示。

3.3 边沿触发方式的动作特点

通过对上述边沿触发器工作过程的分析可以看出,边沿触发方式的动作特点,这就是触发器的次态仅取决于时钟信号的上升沿(也称为正边沿)或下降沿(也称为负边沿)到达时输入的逻辑状态,而在这以前或以后,输入信号的变化对触发器输出的状态没有影响。

4、脉冲触发的触发器

4.1 电路结构和工作原理

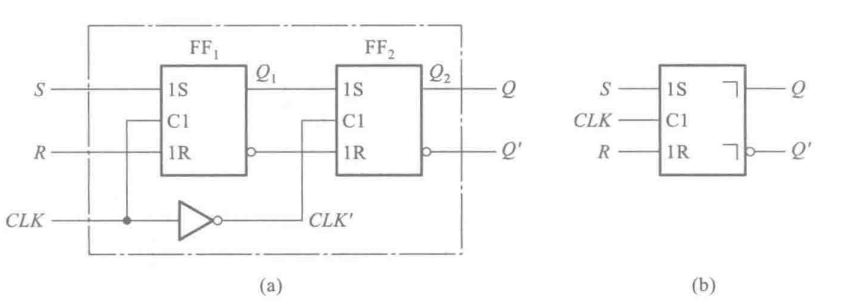

将边沿触发器里的两个电平触发D触发器(D型锁存器)换成电平触发的SR触发器,如下图所示,来讨论一下它的触发过程。

图(a)的电路是脉冲触发 SR 触发器的典型电路(以前也把这个电路称作主从 SR触发器)。FF1和 FF2分别称为主触发器和从触发器。

- 当 CLK=0 时,FF1保持原状态不变。

- 在 CLK变为高电平后,CLK=1、CLK'=0,主触发器的输出 Q1将按照 S 和 R 输入端信号被置成相应的状态,而从触发器保持原来的状态不变。

- 当 CLK 回到低电平,亦即下降沿到来时,从触发器的输出 Q2被置成与此刻 Q1相同的状态,而主触发器开始保持状态不变。

由此可见,在一个时钟周期里,输出端的状态只可能改变一次,而且发生在 CLK的下降沿。这—点和边沿触发器类似。

但需要注意的是,现在输入端的主触发器 FF1是一个电平触发的 SR 触发器,而不是电平触发的 D 触发器了。

- 由于在 CLK 高电平期间主触发器输出的状态可能随 S和 R 状态的变化而发生多次翻转,输出端的状态不可能始终与输入状态保持一致。

- 因此,在脉冲触发 SR 触发器中,不能像边沿触发器那样,仅仅根据 CLK 下降沿到来时刻输入端 S 和 R 状态确定输出端 Q 的状态,而必须考察全部 CLK=1期间主触发器状态的变化情况。这一点就是脉冲触发方式和边沿触发方式的区别所在。(主触发器的输出≠最后的输出)

- 例如,在图(a)的电路中,当 CLK=1期间输入信号先是 S=0、R=1,主触发器被置成 Q1=0;随后又变为 S=1、R=0,于是主触发器被置成了 Q1=1。而在 CLK 下降沿到来之前输入又变成了S=0、R=0,这时主触发器将保持 Q1=1不变。这样在 CLK下降沿到来时,输出便被置成 Q=Q1=1。

- 显然,如果只根据 CLK下降沿到来时的输入状态,是无法正确地确定输出状态的。

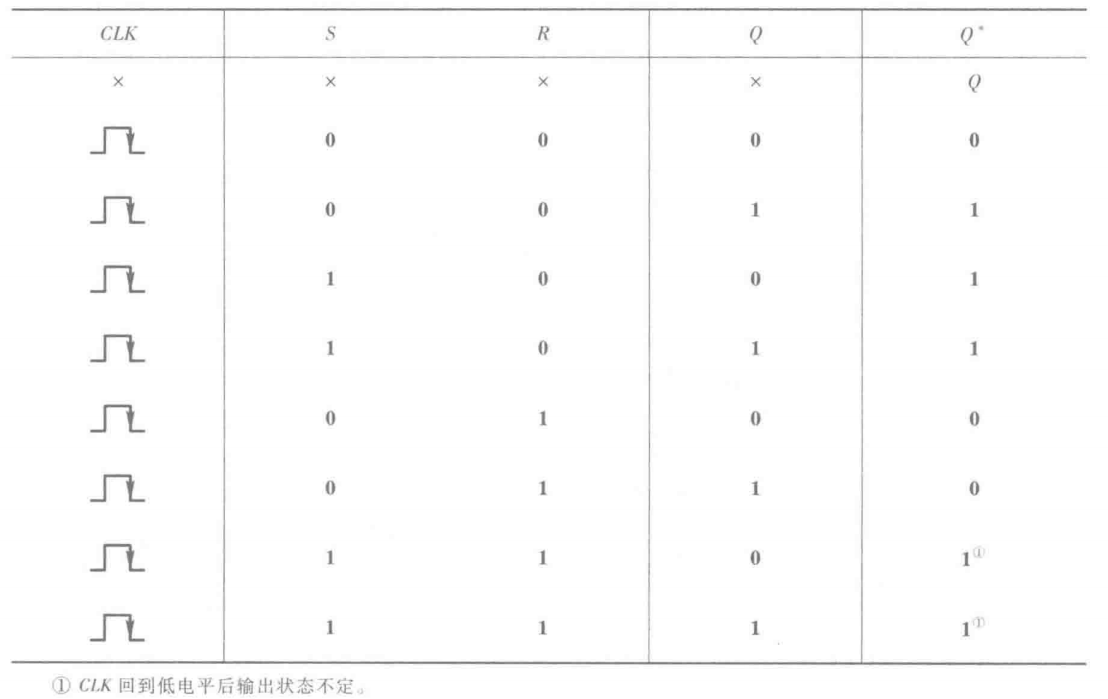

- 在 CLK高电平期间输入 S、R 不变的情况下,可以列出脉冲触发 SR 触发器的特性表,如表所示。表中用 CLK一行里的"

"符号表示脉冲触发方式,而且 CLK 以高电平为有效电平(即 CLK 高电平时接受输入信号),输出端状态的变化则发生在 CLK下降沿。这种情况也称为正脉冲触发。

"符号表示脉冲触发方式,而且 CLK 以高电平为有效电平(即 CLK 高电平时接受输入信号),输出端状态的变化则发生在 CLK下降沿。这种情况也称为正脉冲触发。

因为需要等到CLK的有效电平消失后(即回到低电平),输出状态才改变,故也把这种触发方式称为延迟触发。

最后

以上就是从容画板最近收集整理的关于数字电路中的锁存器(latch)和各种触发器(flip-flop)一、SR 锁存器(保持电路状态,具备记忆功能)二、触发器的全部内容,更多相关数字电路中的锁存器(latch)和各种触发器(flip-flop)一、SR内容请搜索靠谱客的其他文章。

发表评论 取消回复