1.版本及其命名方法

ARMv+[版本号]+[变种的字符]+[字符x+排除某种功能的字符]

1.1 ARM体系的变种

①Thumb指令集(T变种)

与ARM指令集的32位长度对应,Thumb指令集的长度仅为16位。其与ARM指令集相比有如下局限性:完成形同的指令需要更多的指令,也就是说耗时更长;没有 包含进行异常处理的一些指令。

②长乘法指令(M变种)

共两条指令:【32位整数】 * 【32位整数】 = 【64位整数】

【32位整数】 * 【32位整数】 + 【32位整数】 = 【64位整数】

需要注意的是在ARM体系版本4及其以后,M变种成为系统的标准配置。

③增强型DSP指令(E变种)

实现一些典型DSP算法包括:16位数据的乘法和乘加;饱和的带符号的加减法(所谓饱和就是若计算结果溢出则使用最大数或最小负数来表示);双字节数据操作;cache预取指令

④Java极速器Jazelle(J变种)

⑤ARM媒体扩展功能(SIMD变种)

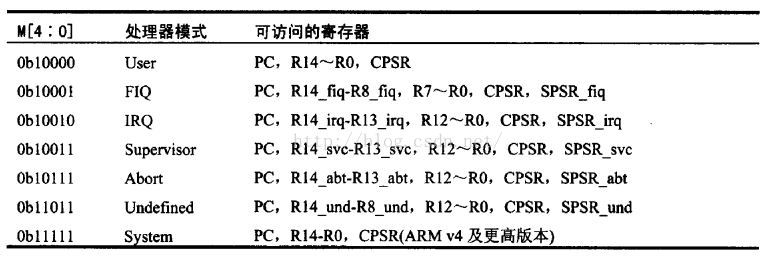

2.【重要】ARM处理器模式

①用户模式(usr)

正常程序执行的模式

②快速中断模式(FIQ)

用于高速数据传输和通道处理

③外部中断模式(IRQ)

用于普通的中断处理

④超级模式(Supervisor,sve)

给操作系统使用的一种模式

⑤数据访问中止模式(Abort,abt)

用于虚拟存储和存储保护

⑥未定义指令中止模式(und)

CPU将要执行的下一条指令码不在指令集范围内

⑦系统模式(sys)

用于运行特权的操作系统任务

其中除①外的其他模式——特权模式(Privileged Modes)。特权模式中除系统模式外叫——异常模式。

2.【重要】ARM寄存器

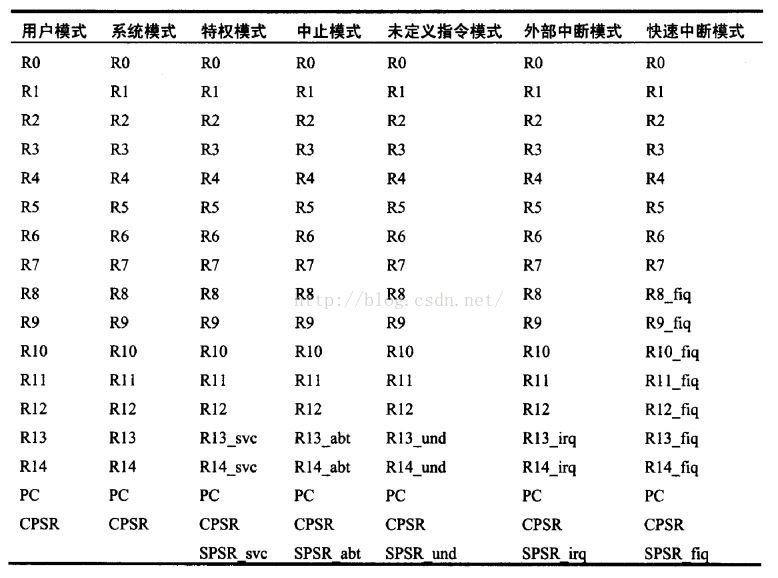

在不同的工作模式下,可见的寄存器有所同,如下表所示为各个模式下可见的寄存器。共计31个寄存器通用寄存器和6个状态寄存器

2.1通用寄存器

分成三类:

①未备份寄存器:R0~R7,其在所有模式下都相同的,物理地址也是相同的。

②备份寄存器:

R8~R12,每个寄存器有两个物理地址,其一为FIQ模式下专用记做rx_fiq,其二为其他模式下通用,记做rx_usr。

R13(SP),一般用作栈指针,在各个模式下拥有各自的专用物理地址(usr和sys共用一个r13)记做r13_[mod]。一般情况下,将r13初始化指向各个异常状态的专用栈地址,当进入某个异常模式时,将需要用的到寄存器压入r13指向的栈地址中,当退出异常模式时,将其弹出。

R14(LR),称为连接寄存器,一般拥有以下两种作用:①在对应模式下存入当前子程序的返回地址;②当发生异常中断时,存入中断返回地址。

③程序计数器R15(PC),存入当前运行指令的下一条指令地址,其偏移量有可能为8字节,也有可能为12字节,其取决与芯片的设计方式。

2.2 程序状态寄存器

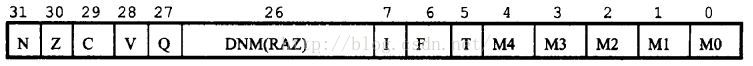

CPSR:当前程序状态寄存器

①条件标志位

N——当两个补码表示有符号运算时,N=1表示结果为负数,N=0表示结果为正数或0。

Z——Z=1表示运算结果为0,=1表示结果不等于0.

C——在加法指令中,C=1表示发生上溢出,C=0表示其他情况;在减法指令中,C=0表示借位或无符号数发生下溢出,C=1表示其他;③移位操作,C表示最后一次溢出的位。

V——加减法操作中,当操作数和运算结果为二进制补码表示的带符号的数时,V=1表示符号位溢出。

Q——DSP指令溢出则Q=1

②控制位

I——禁止IRQ中断,I=1

F——禁止FIQ中断,F=1

T——T=0表示执行ARM指令,T=1表示执行Thumb指令

M控制位——如下表所示

SPSR——程序状态备份

当ARM发生中断时,会将当前的CPSR复制给对应中断模式的SPSR,当中断返回时会将当前中断模式下的SPSR复制回给返回状态的CPSR中。

最后

以上就是悦耳铃铛最近收集整理的关于【arm体系结构与编程】1.概述及其基本编程模型(一)的全部内容,更多相关【arm体系结构与编程】1内容请搜索靠谱客的其他文章。

发表评论 取消回复