本篇文章主要整理ARM针对Cache一致性做的工作和其解决方法,介绍ARM ACE协议和CCI-400 Cache一致性互联结构。

一、ARM ACE协议

ARM推出ACE协议解决cache一致性问题,ACE协议是AXI4协议的扩展,将一致性监听snoop协议和AXI4总线相结合,其主要拥有如下特性:

- 每个cache line使用五中状态定义,每个cache line的状态决定了访问cache line时会产生怎样的响应行为,支持MESI/ESI/MEI/MOESI四种一致性协议。

- AXI4协议扩展,包括新增的信号和新增的通道行为;

- Barrier传输,保证传输的顺序;

- DVM(Distributed Virtual Memory)功能,用于管理虚拟内存。

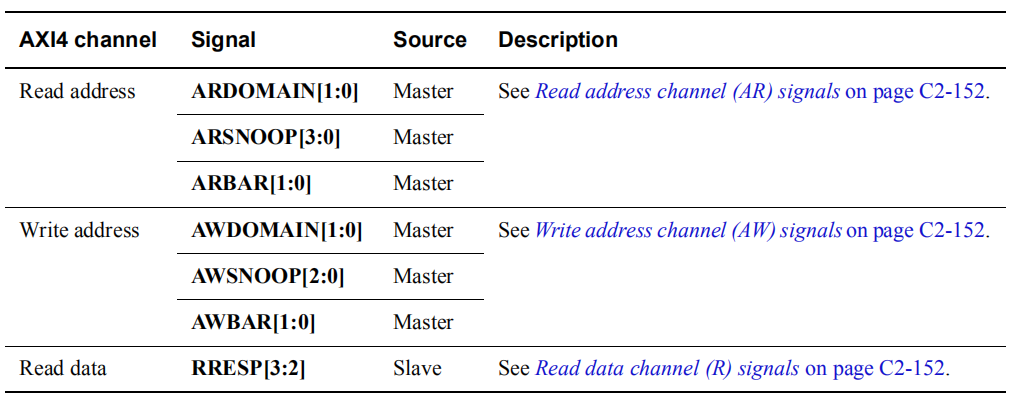

ACE和AXI4的差异主要在以下几个方面,首先是在AXI4读写通道增加如下图所示信号。AxDOMAIN用于指示读写传输的可共享域,AxSNOOP用于指示可共享的读写传输类型,RRESP[3:2]用于可共享读传输的读响应。

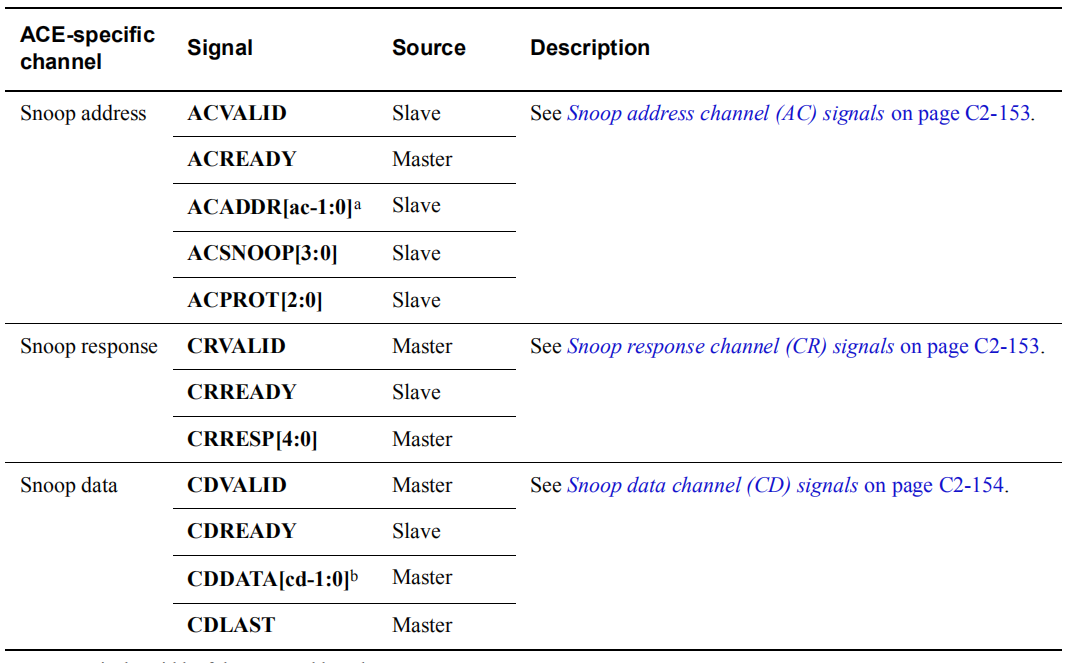

其次是增加了额外的ACE通道:snoop地址通道(AC)、snoop数据通道(CD)和snoop响应通道(CR),这个处理方式和写通道类似。AC通道主要用来提供Cache监听相关地址和相应的控制信息;CD通道是一个可选的输出通道,用于传递监听数据输出给另一个cache;CR用于应答接收到的监听传输,监听应答意味着CD存在相关的数据传输。

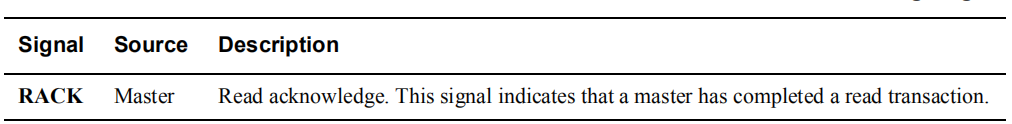

总体上来说,ACE通道仍是基于ready/valid握手的方式来完成,除了没有ID用于区分传输,其他信号时序和AXI较为一致。除了ACE通道外,还增加了一个一些额外的应答信号和复位要求。

ACE协议引入了可共享域(shareability domains)的概念,一个可共享域包含一组master,并且允许其中一个master决定一致性传输的其他masters,类似于Intel的CA和HA的作用。使用AxDOMAIN来指示当前共享域。ACE协议支持四个等级的共享域:单个master(Non-shareable)、内部多master(Inner Shareable)、外部多master(Outer Shareable)和全master(System),范围依次扩大。

ACE支持最小16bytes,最大2048bytes的cache line大小。

除此之外,ACE同样支持ACE-lite版本,ACI-lite没有新增的通道,这是在现有通道基础上增加了新的信号。ACE-lite Master主要用来监听其他ACE Master的信息,其不能被监听。

二、CCI-400互联cache一致性总线

ARM CCI-400完成上述两种ACE接口互联,上图是ARM Cortex-A15互联的例子,CCI-400支持的ARM处理器类型有:Cotex-A7、Cortex-A15、Cortex-A17、Cortex-A53和Cortex-A57。除此以外,CCI-400还支持GPU、IO、DDR等异构的ACE-lite接口。如果对应的master带有MMU,则可以再额外添加一个DVM接口支持MMU。

上图中GPU和IO到MMU之间还增加了一个ADB设备,该设备的作用是异步桥接,将不同时钟域下的设备接到同一互联总线中,添加ADB设备后可以集成多个power domain或clock domain设备。

ACE-lite可直接和NIC总线互联,下面再连接多个Slaves,用于非Cache Salve的访问。ACE-lite也可以和兼容该接口的memory控制器连接,例如DMC-400。

通过上述互联方案,可以将操作系统运行在多个处理器簇之上,但前提是需要使用ARM big.little大小核处理器软件模型,例如Global Task Scheduling, GTS。

三、MOESI协议

ARM和AMD组成了HSA联盟,共同推进了MOESI协议。该协议为MESI协议的扩展,其中MEI的含义和之前相同,S有细微的变化,O为新增状态,具体各个含义如下:

M:Modified,表示当前cache line中的数据被处理器修改,且和memory中的不一致。

E:Exclusive,表示当前cache line中的数据为最新的,且和memory中一致,clean。

O:owned,表示当前cache line数据存在多份副本,且不一定和memoy一致,拥有owned状态的cache line负责写回操作。有多个shared cache line,但只有一个owned cache line。

S:Shared,表示当前cache line中的数据在多个Cache line中存在,当没有owned状态存在cache line时,其数据和memory一致,当有owned状态存在时,其数据不一定和memory一致;

I:Invalid,表示当前cache line中的数据不是最新的,且cache line无效,需要再memory或其他cache line中寻找最新的数据;

关于这么处理的好处,可以参考这篇文章:

MOESI缓存一致性协议相对于MESI有什么好处? - IT屋-程序员软件开发技术分享社区 (it1352.com) https://www.it1352.com/1615023.html3.3.1 Cache一致性的基本概念_sailing_新浪博客 (sina.com.cn)

https://www.it1352.com/1615023.html3.3.1 Cache一致性的基本概念_sailing_新浪博客 (sina.com.cn) http://blog.sina.com.cn/s/blog_6472c4cc0100qxcd.html总结:通过硬件管理一致性可以有效提升系统性能,同时降低片上数据的分享所带来的系统功耗,减少外部memory的访问,减少软件开销。

http://blog.sina.com.cn/s/blog_6472c4cc0100qxcd.html总结:通过硬件管理一致性可以有效提升系统性能,同时降低片上数据的分享所带来的系统功耗,减少外部memory的访问,减少软件开销。

ARM的这种方案采用的是监听的方式,会带来更高的带宽需求,因此在最新的ARM架构中,加入了snoop fliter监听过滤机制,可以有效的减少带宽。snoop filter的实现基于directory,因此总结来看ARM的方案和Intel的解决方案类似,都是snoop为主,directory为辅。

最后

以上就是虚拟溪流最近收集整理的关于异构多核Cache一致性问题和解决方法(二)的全部内容,更多相关异构多核Cache一致性问题和解决方法(二)内容请搜索靠谱客的其他文章。

![[转]什么样的办公方式效率最高?](https://www.shuijiaxian.com/files_image/reation/bcimg21.png)

发表评论 取消回复