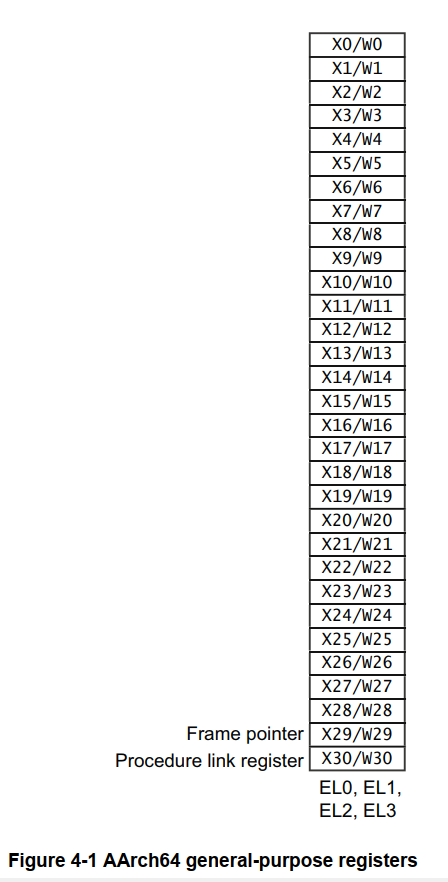

AArch64执行状态提供了31个64位通用寄存器,它们可在任意时刻和所有异常级别被访问。

每个寄存器为64位宽且它们通常被称为寄存器X0~X30。

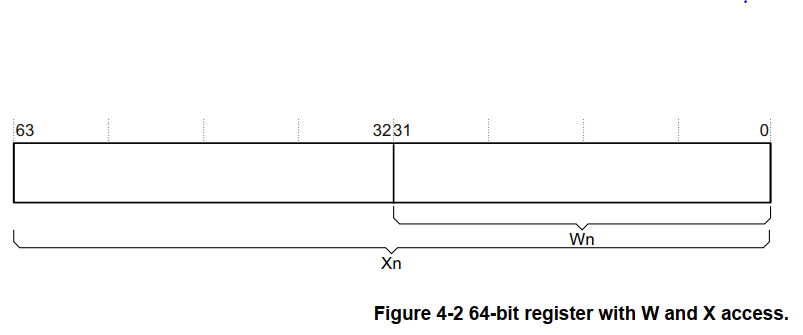

每个AArch64 64bit通用寄存器(X0~X30)也有32bit(W0~W30)形式。

32bit W寄存器位相关64位X寄存器的低一半。即,W0映射到X0的低字,W1映射到X1的低字。

从W寄存器中读取将忽视对应的X寄存器的高32位并不对它们做修改。对W寄存器进行写将X寄存器的高32位设置位0。即,写0xffffffff到W0将X0设置位0x00000000fffffff。

1 AArch64特殊寄存器

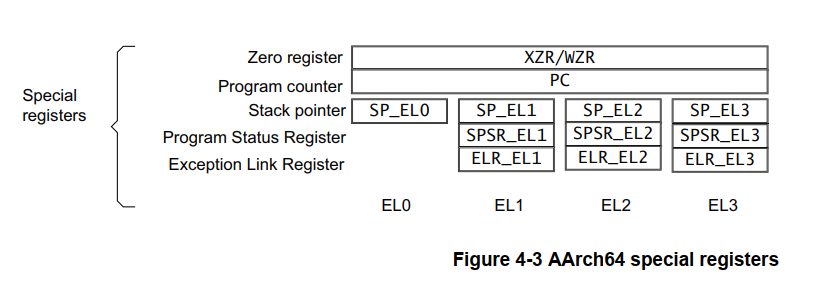

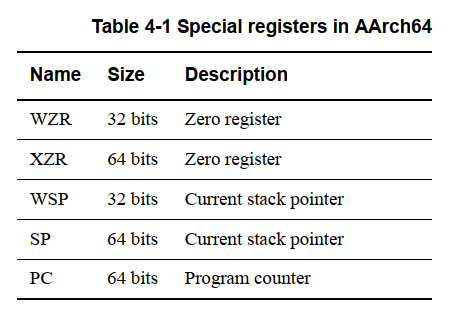

除了上述31个核心寄存器,也存在几个特殊寄存器。

NOTE: 没有X31或W31寄存器。很多指令被编码为31号代表zero register,ZR(WZR/XZR)。也有严格的指令组,一个或多个参数被编码为31号代表stack pointer (SP)。

当访问zero register时,所有写都被忽略且所有读返回0。注意SP寄存器的64bit形式不会用X前缀。

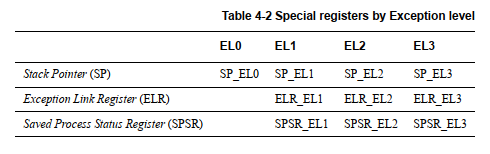

在ARMv8架构中,当执行在AArch64上时,异常返回状态保持在每个异常级别的下述寄存器中:

(1)异常链接寄存器(ELR)

(2)保存进程状态寄存器(SPSR)

对每个异常级别有一个SP寄存器,但不会用来保持返回状态。

1.1 zero register

当作为源寄存器时zero register读为0且当作为目的寄存器时丢弃结果。你可以将zero register用于大多数指令,但不是全部指令。

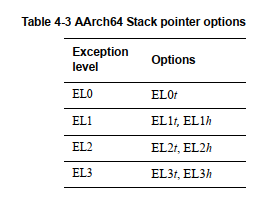

1.2 Stack pointer

在ARMv8架构中,用stack pointer寄存器来分开来自异常级别的范围。默认情况下,使用一个异常来选择目标异常级别的stack pointer,SP_ELn。比如,使用一个EL1的异常来选择SP_EL1。每个异常级别有自己的stack pointer,SP_EL0,SP_EL1,SP_EL2和SP_EL3。

当在AArch64中超过EL0异常级别时,处理器可以其中一种:

(1)与异常级别相关的64位stack pointer(SP_ELn)

(2)EL0相关的stack pointer (SP_EL0)

EL0仅访问SP_EL0。

t后缀表明了SP_EL0 stack pointer被选择。h后缀表明SP_ELn stack pointer被选择。

SP不能被大多数指令所引用。但是,一些形式的算法指令,比如ADD指令,可以读和写当前的stack pointer来调整函数中的stack pointer。

ADD SP, SP, #0x10

1.3 Program Counter

原始的ARMv7指令集的一个特性为将R15(PC)作为通用寄存器。PC使能了一些聪明的编程技巧,但它也引入了编译器和流水线的复杂度。在ARMv8中移除直接访问到PC使更容易预测返回和简化ABI spec。

PC不能作为已命名的寄存器被访问。它的使用在某些指令上是含蓄的,比如PC相关的加载和地址的产生。PC不能作为数据处理指令的目的或加载指令而指明。

1.4 Exception Link Register(ELR)

ELR寄存器保持着异常返回地址。

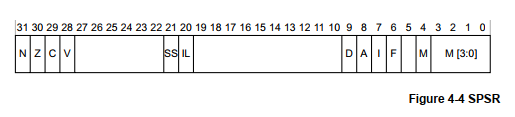

1.5 Saved Process Status Register

当异常产生时,处理器的状态保存在相关的保存进程状态寄存器SPSR,与ARMv7的CPSR相同的方式。在异常产生之前SPSR保持着PSTATE值并在异常返回时恢复PSTATE值。

AArch64的单个位如下值所示:

N 负值(N标志)

Z 零值标志

C 实现标志(C标志)

V 溢出标志(V标志)

SS 软件步骤。当异常产生时表明是否软件步骤是否使能。

IL 非法执行状态位。在异常产生之前立即显示PSTATE.IL值。

D 进程状态调式mask。表明是否从watchpoint,breakpoint和软件单步调式事件是屏蔽或不屏蔽。

A SError屏蔽位

I IRQ屏蔽位

F FIQ屏蔽位

M[4] 异常产生的执行状态。0表示AArch64。

M[3:0] 异常产生的模式或异常级别

在ARMv8中,写SPSR依赖于异常级别。如果异常发生在EL1,SPSR_EL1被使用。如果异常产生在EL2,SPSR_EL2被使用。如果异常发生在EL3,SPSR_EL3被使用。当异常产生时core遍历SPSR。

note: 与一个异常级别相关的寄存器组ELR_ELn和SPSR_ELn在执行在更低的异常级别时保持着它们的状态。

2 处理器状态

AArch64没有直接等于ARMv7 CPSR。在AArch64中,传统CPSR的部件被当作能够独立访问的域。它们被称为PSTATE。

处理器状态,或PSTATE域,对于AArch64有如下定义:

| Name | Description |

| N | 负值条件标志 |

| Z | 零值条件标志 |

| C | 执行条件标志 |

| V | 溢出条件标志 |

| D | 调试mask标志 |

| A | SError mask位 |

| I | IRQ屏蔽位 |

| F | FIQ屏蔽位 |

| SS | 软件单步位 |

| IL | 非法执行状态位 |

| EL | 执行级别 |

| nRW | 执行状态 0 64位 1 32位 |

| SP | 栈指针选择 0 SP_EL0 1 SP_EL1 |

在AArch64中,通过执行ERET指令从异常返回,这会导致SPSR_ELn被拷贝到PSTATE。这将恢复ALU标志,执行状态,异常级别,和处理器分支。你将从ELR_ELn的地址继续执行。

PSATE.{N,Z,C,V}域可被EL0访问。所有其他PSTATE域可以被执行在EL1或更高级别,它们在EL0为未定义。

最后

以上就是靓丽豌豆最近收集整理的关于ARMv8-A编程指导之ARMv8寄存器(1)1 AArch64特殊寄存器2 处理器状态的全部内容,更多相关ARMv8-A编程指导之ARMv8寄存器(1)1内容请搜索靠谱客的其他文章。

发表评论 取消回复