碎碎念:最近更新的周期有点长...

主要最近和朋友一起重新开了一个公众号(FPGA Breaker),这个公众号也和本公众号垂直深度,不会和本公众号内容有太多重叠,主要是本人想推进国内开源IP的使用和发展,这样就可以大大缩短开发周期,不需要独立去写各种简单的IP核,比如IIC、UART、SPI等等,这方面国外的Opencores做的很好,但是Opencores是符合国外编程习惯的,大部分IP核都是VHDL语言写的,而且国内对开源的概念的理解还不是......

因为本人精力有限,所以想请朋友帮忙,会重新开一个公众号,因为新的公众号会以程序讲解和设计为主,所以还在考虑怎么方便和读者沟通的问题。

最后就是开源IP肯定要有验证平台,所以最近也在准备一个开源平台,原理图已画好,正在Layout,这里简单介绍一下设计理念,就是所有的EDA全部采用开源工具链,不会涉及到License的问题,源码和各种文件也会同步到github上。

PS:大家对于上面有什么好的Idea或者其他想法,可以通过公众号->服务->帮我中心,联系我们,欢迎各位朋友提问题和意见,悉听各位大佬尊言。

最后就是本系列文章,大部分文章草稿已经完成,剩下的就是排版和审核了,预计会在六一儿童节之前完成。

切入正题

从硬件上来说,一般PHY芯片为模数混合电路,负责接收电、光这类模拟信号,经过解调和A/D转换后通过MII接口将信号交给MAC芯片进行处理。一般MAC芯片为纯数字电路。

物理层定义了数据传送与接收所需要的电与光信号、线路状态、时钟基准、数据编码和电路等,并向数据链路层设备提供标准接口。物理层的芯片称之为PHY。

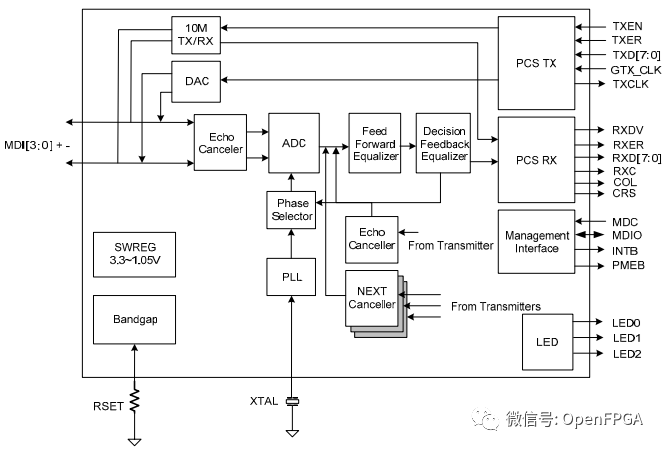

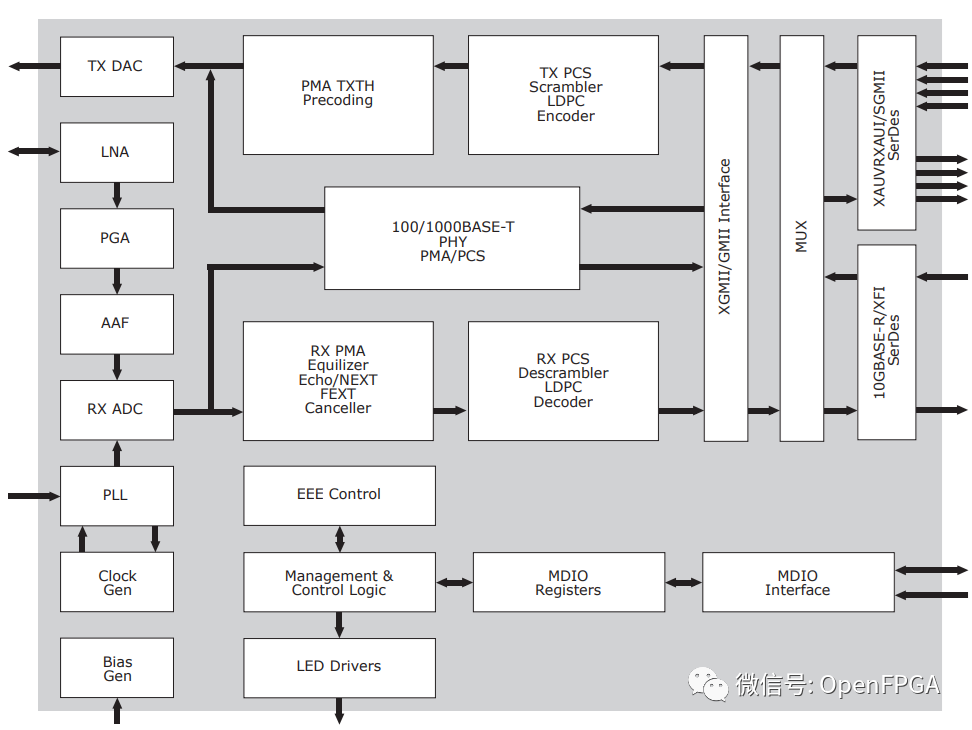

下图为RTL8211的原理框图,详细的数据手册链接如下:

http://download3.dvd-driver.cz/realtek/datasheets/pdf/rtl8211e(g)-vb(vl)-cg_datasheet_1.6.pdf

图8‑7 RTL8211原理框图

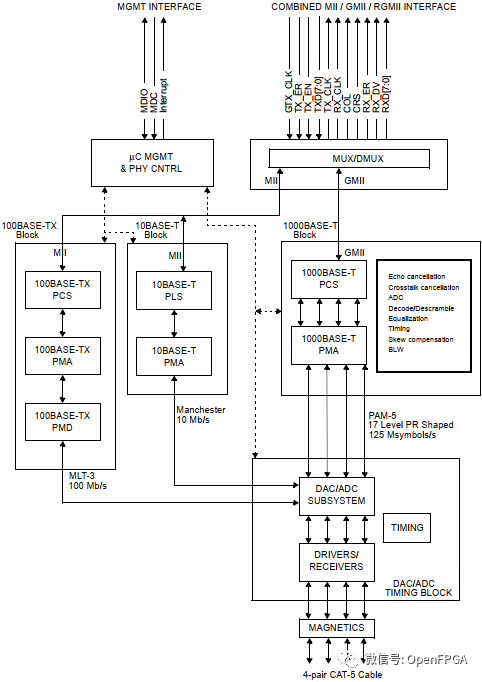

下图是Ti的DP83865原理框图,详细的数据手册链接如下:

http://www.ti.com/product/DP83865/technicaldocuments

图8‑8 DP83865原理框图

下图为88X3140/3120的原理框图,详细的数据手册链接如下:

https://www.marvell.com/products/transceivers/alaska-x-gbe.html

图8‑9 88X3140/3120原理框图

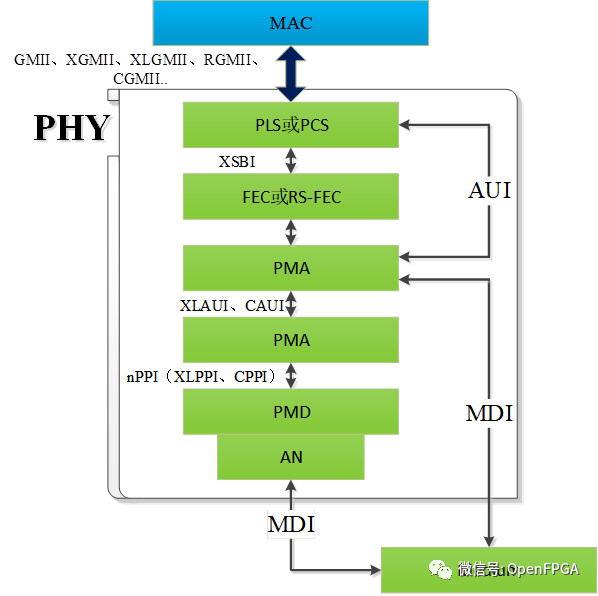

通过几个PHY片的原理框图可以总结出下面的简化PHY片的原理框图。

图8‑10 PHY简化的原理框图

从上图可知,PHY它包含了多个功能模块,功能模块的多少会因需要的不同而有所增减,比如:

只有10GBase-R、40GBase-R、100GBase-R的PCS需要FEC;

40GBase-R的PCS需要2个PMA、100GBase-R的PCS需要3个PMA;

只有≥1Gbps以上的背板应用场景才会用到AN。

接下来详细介绍上图中各个功能模块:

表8‑3各个功能模块的作用

名称 | 作用 | |

PLS | Physical Sublayer Signaling | 对MAC给的信息进行传递,只在1Mb/s、10Mb/s的应用场景才出现; |

PCS | Physical Coding Sublayer | 对MAC给的信息进行编码,应用于≥100 Mb/s的应用场景,比如完成8B/10B、64B/66B、256B/257B编码; |

FEC | Forward Error Correction | 前向纠错,与10GBase-R、40GBase-R的PCS 搭配; |

RS-FEC | Reed-Solomon Forward Error Correction | Reed-Solomon前向纠错,比单纯的FEC纠错能力更强,与100GBase-R的PCS 搭配,采用256B/257B编码; |

PMA | Physical Medium Attachment | 物理介质连接子层。执行并串/串并转换 |

PMD | Physical Medium Dependent | 物理介质相关子层。信号转换到特定介质上或反向转换 |

AN | Auto-Negotiation Function | 自动协商,使背板两侧的Device能够互换信息以发挥出彼此最大的优势; |

图中还有连接各个模块间的接口比较特殊,这里面在单独列出来,如下表所示:

表8‑4各个模块间的接口

名称 | 备注 | |

PLS与PMA间的接口 | AUI | Attachment Unit Interface |

PCS与FEC间的接口 | XSBI | 10-Gigabit Sixteen Bit Interface |

PMA与PMA间的接口-可以是chip to chip,也可以是chip to module | XLAUI | 40 Gigabit Attachment Unit Interface,4条lane,每条lane的数率是10.3125Gbps; |

CAUI | 100 Gigabit Attachment Unit Interface,10条lane,每条lane的数率是10.31250Gbps; | |

PMA与PMD间的接口 | nPPI1 | Parallel Physcial Interface |

1:nPPI特定出现在PMD所接的媒介是光纤的情况下,比如40GBase-SR4、100GBase-SR10、40GBase-LR4协议。也就是说这种情况下的PMD是光模块,nPPI就必然是一种chip to module间的接口,这也是IEEE802.3标准与OIF_CEI标准兼容的地方之一。

推荐阅读

例说七层OSI参考模型

TCP/IP模型

TCP和UDP

以太网遵循的IEEE 802.3 标准

媒体访问控制(MAC,Media Access Control)

媒体独立接口(MII,Meida Independent Interface)

GMII、SGMII和SerDes的区别和联系

一大波HLS设计资料来了

2020版深入浅出玩转FPGA视频教程

点击上方字体即可跳转阅读哟

最后

以上就是追寻铃铛最近收集整理的关于PHY(Physical Layer,PHY)通俗理解的全部内容,更多相关PHY(Physical内容请搜索靠谱客的其他文章。

发表评论 取消回复