写在前面

全部答案汇总:刷完这套题,我才发现Verilog原来如此简单----HDLBits答案汇总

今天更新Circuits章节中Verification:Reading Simulation的1个小节:Build a circuit from a simulation waveform

这个章节的内容是根据波形图编写Verilog代码,从波形图到硬件描述语言的转变是FPGAer的基本功(核心),而且在信号多、时序复杂的项目中读懂波形图更是一项一定要熟练掌握的能力。

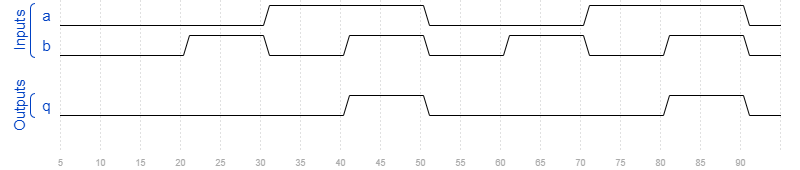

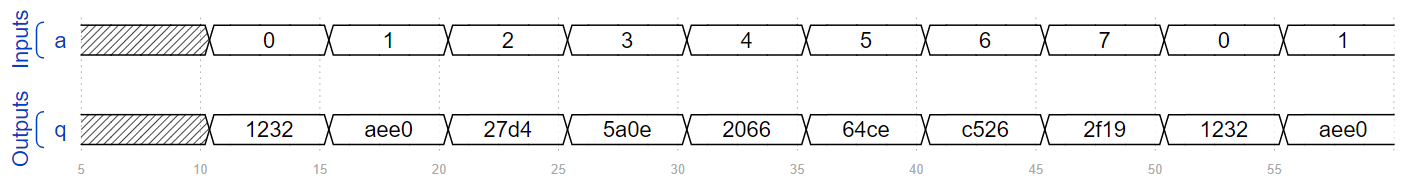

Combinational circuit 1

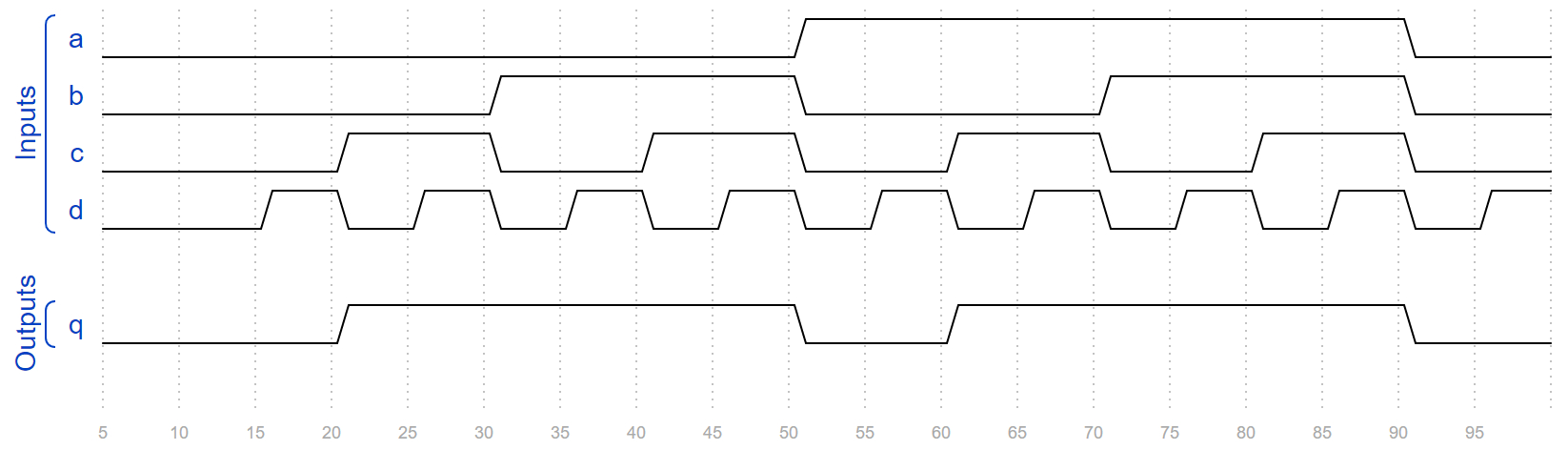

【题目】:

根据下面的时序图实现这个组合逻辑电路。

【个人思路】:

从上面的q输出为1处,可以看到a、b均为1,所以逻辑是 a & b.

module top_module (

input a,

input b,

output q );//

assign q = a & b; // Fix me

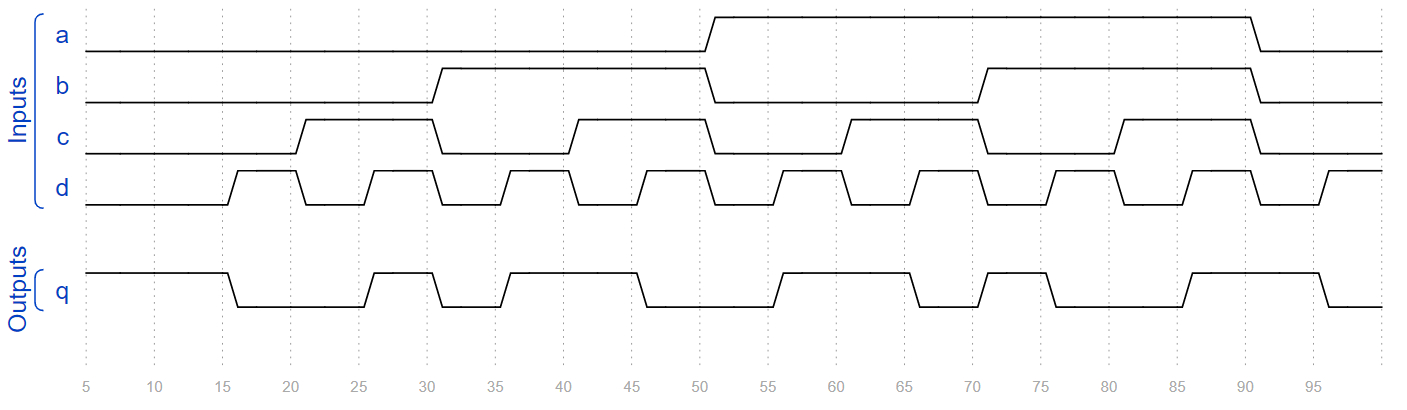

endmoduleCombinational circuit 2

【题目】:

根据下面的时序图实现这个组合逻辑电路。

【个人思路】:

这个时序图稍微复杂点,最好是列出卡诺图,如下:

红色部分的四个数据,可以看出来是 ( a同或b ) 与上 ( c同或d );

蓝色部分的四个数据,可以看出来是 ( a异或b ) 与上 ( c异或d );

红色+蓝色 = ( a异或b ) 同或( c异或d ) =~a^b^c^d;

module top_module (

input a,

input b,

input c,

input d,

output q );//

//assign q = 1-a^b^c^d;

assign q = ~a^b^c^d;

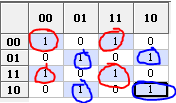

endmoduleCombinational circuit 3

【题目】:

根据下面的时序图实现这个组合逻辑电路。

【个人思路】:

这个时序图稍微复杂点,最好是列出卡诺图,如下:

像我这样框起来:红色:b | d;黄色:b | c;黑色:a | d;绿色:a | c;

module top_module (

input a,

input b,

input c,

input d,

output q );//

assign q = b & d | b & c | a & d | a & c;

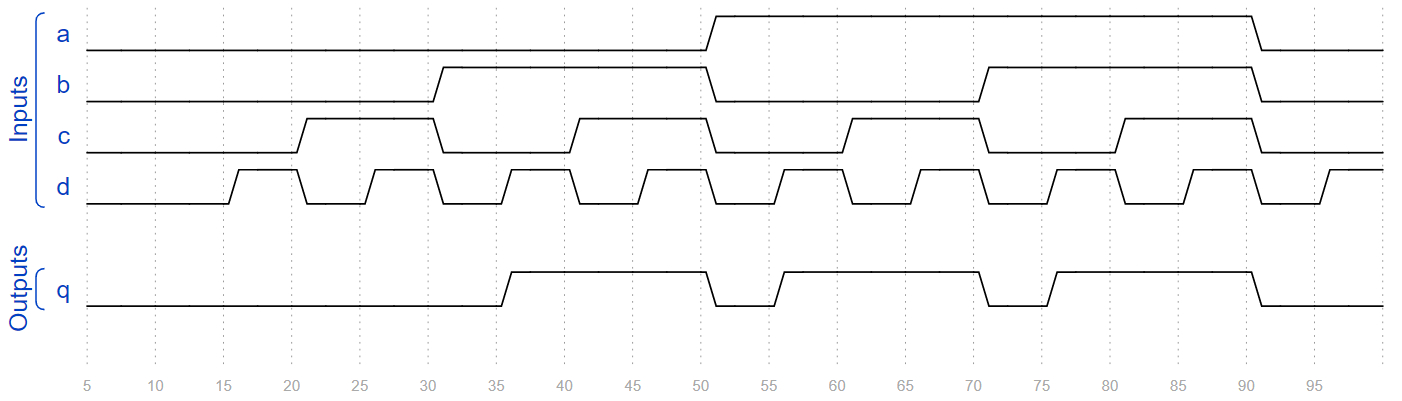

endmoduleCombinational circuit 4

【题目】:

根据下面的时序图实现这个组合逻辑电路。

【个人思路】:

这个时序图稍微复杂点,最好是列出卡诺图,如下:

红色:c;绿色:b;所以化简为 b | c。

module top_module (

input a,

input b,

input c,

input d,

output q );//

assign q = b | c; // Fix me

endmoduleCombinational circuit 5

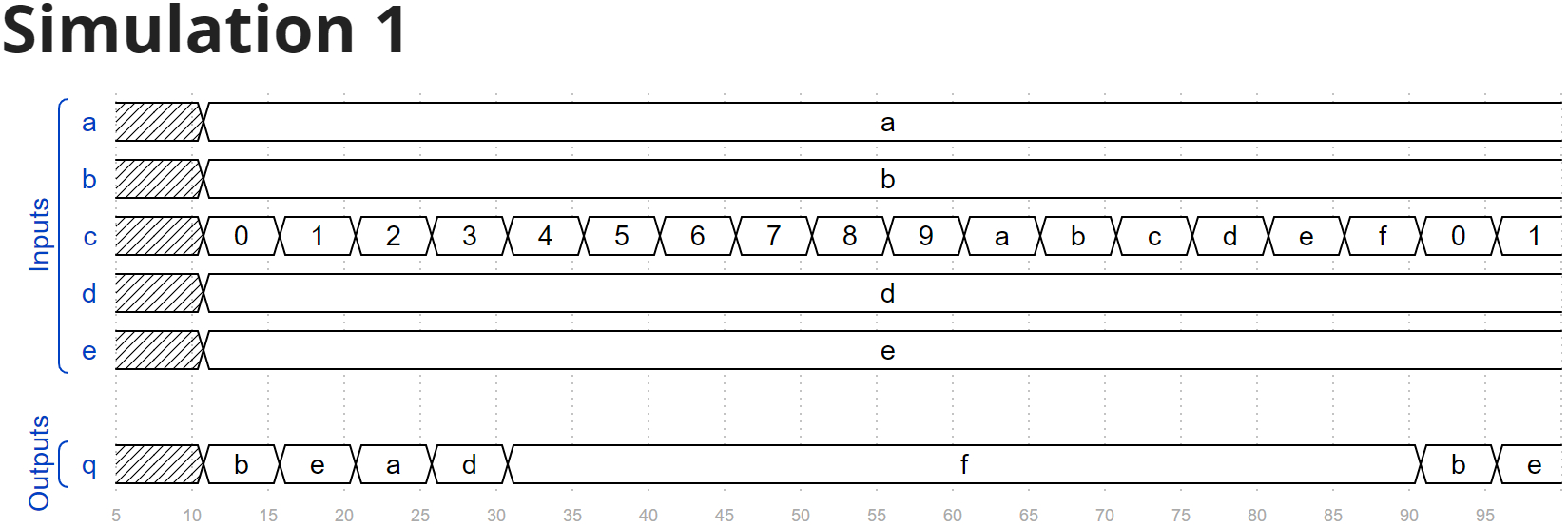

【题目】:

根据下面的时序图实现这个组合逻辑电路。

【个人思路】 :

可以看出这是一个4输入、1输出的组合电路,且输出是根据c的取值来的,所以这个是个4选1电路(MUX4),所以可以用case语句来根据c的取值来进行输出。

module top_module (

input [3:0] a,

input [3:0] b,

input [3:0] c,

input [3:0] d,

input [3:0] e,

output [3:0] q );

always@(*)begin

case(c)

4'd0: q = b;

4'd1: q = e;

4'd2: q = a;

4'd3: q = d;

default: q = 4'hf;

endcase

end

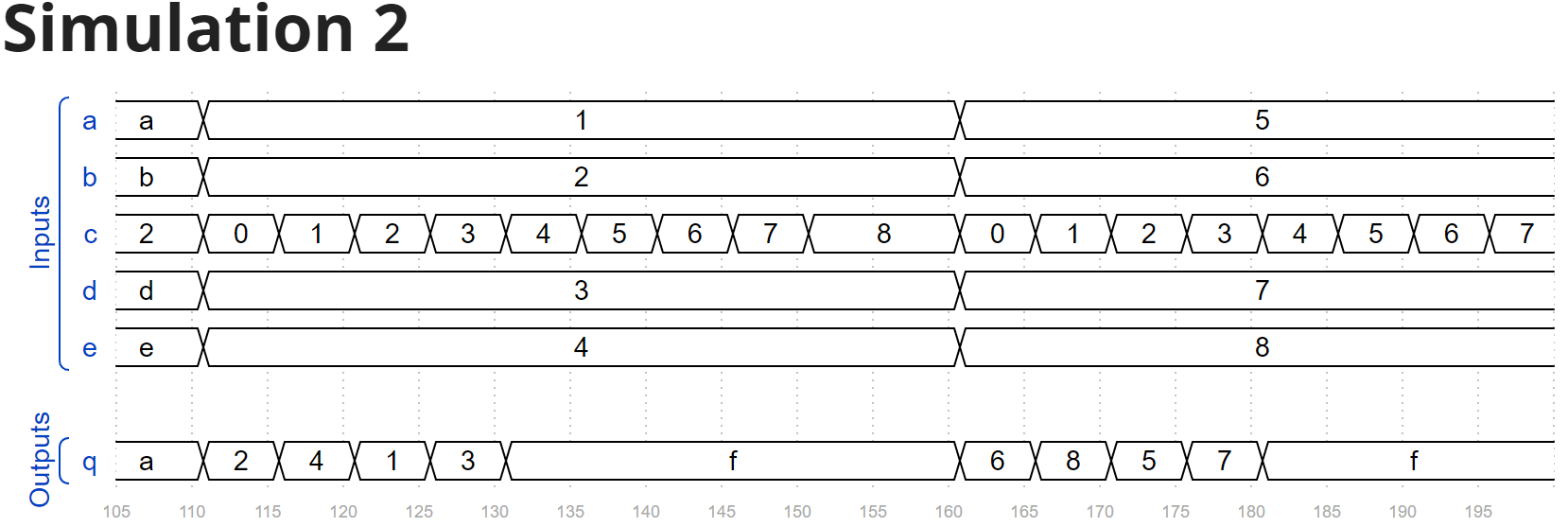

endmoduleCombinational circuit 6

【题目】:

根据下面的时序图实现这个组合逻辑电路。

【个人思路】 :

可以看出这是一个根据输入a的取值来进行输出的组合电路,可以用case语句来根据a的取值来进行输出。

module top_module (

input [2:0] a,

output [15:0] q );

always@(*)begin

case(a)

3'd0: q = 16'h1232;

3'd1: q = 16'haee0;

3'd2: q = 16'h27d4;

3'd3: q = 16'h5a0e;

3'd4: q = 16'h2066;

3'd5: q = 16'h64ce;

3'd6: q = 16'hc526;

3'd7: q = 16'h2f19;

default:;

endcase

end

endmoduleSequential circuit 7

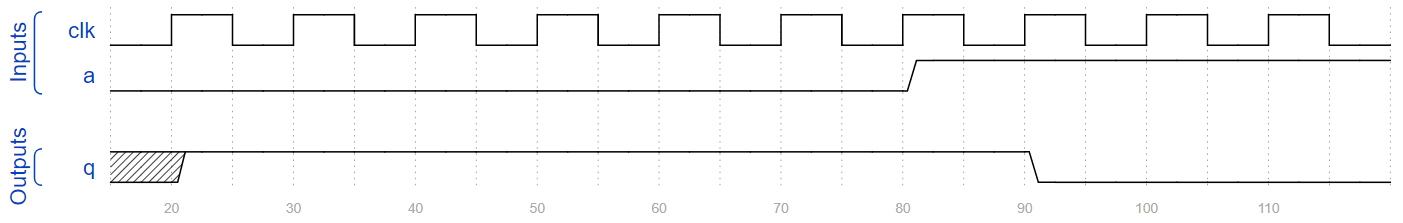

【题目】:

根据下面的时序图实现这个时序逻辑电路。

【个人思路】 :

可以看出输出q是输入a的取反,因为是时序逻辑,所以输出落后输入一个时钟周期。

module top_module (

input clk,

input a,

output q );

always@(posedge clk)begin

if(a)

q <= 1'b0;

else

q <= 1'b1;

end

endmoduleSequential circuit 8

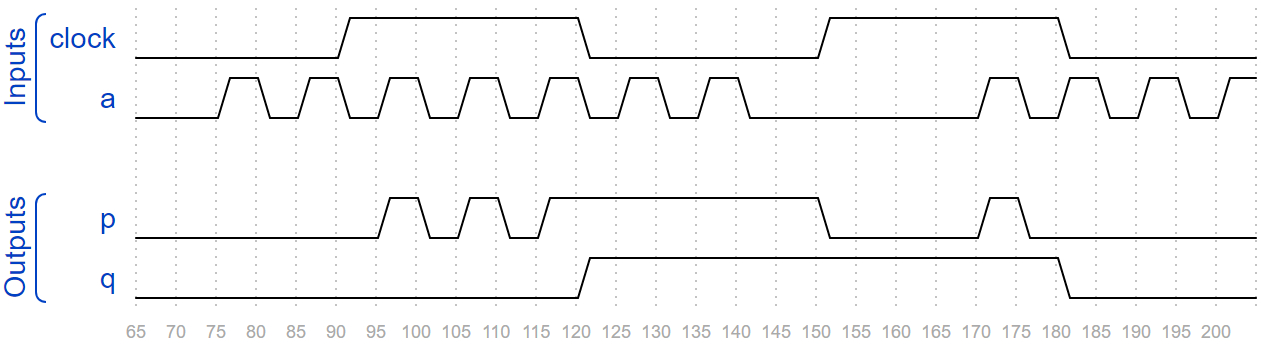

【题目】:

根据下面的时序图实现这个时序逻辑电路。

【个人思路】 :

由图可见,p为a在clock为高电平时的选通信号,q为clock下降沿触发的信号,存放p的值。

module top_module (

input clock,

input a,

output p,

output q );

always@(*)begin

if(clock)

p <= a;

else

p <= p;

end

always@(negedge clock)begin

q <= p;

end

endmoduleSequential circuit 9

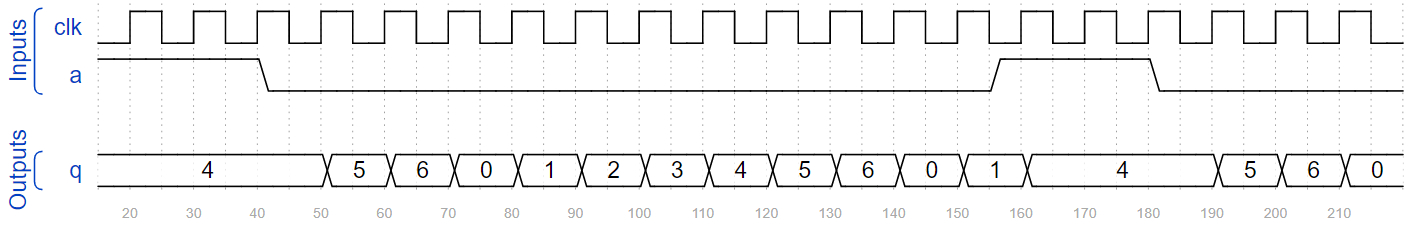

【题目】:

根据下面的时序图实现这个时序逻辑电路。

【个人思路】 :

可以看出这是一个~a使能的0~6计数器,a高电平时计数器复位到4.

module top_module (

input clk,

input a,

output [3:0] q );

always@(posedge clk)begin

if(~a)begin

if(q == 4'd6)

q <= 4'd0;

else

q <= q + 1'b1;

end

else

q <= 4'd4;

end

endmoduleSequential circuit 10

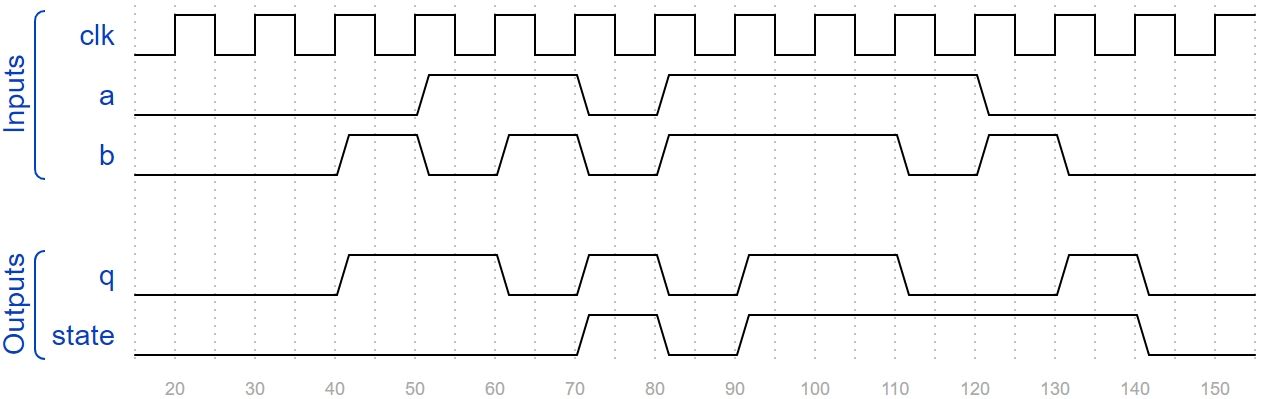

【题目】:

根据下面的时序图实现这个电路,该电路包含组合逻辑和D触发器。

【个人思路】 :

可以看到当输出q为高电平时,a、b、state三个中总是有奇数个高电平,所以q是a、b、state三个的偶校验位:q = a ^ b ^ state;

再来观察state的变化,state的变化都发生在(a == b)时,且变化的值为a(或者说b),当a不等于b时,state保持不变。

module top_module (

input clk,

input a,

input b,

output q,

output state );

assign q = a ^ b ^ state;

always @(posedge clk)begin

if(a == b)

state <= a;

else

state <= state;

end

endmodule最后

以上就是魁梧大门最近收集整理的关于刷完这套题,我才发现Verilog原来如此简单----HDLBits答案系列 -- Build a circuit from a simulation waveform写在前面Combinational circuit 1Combinational circuit 2Combinational circuit 3Combinational circuit 4Combinational circuit 5Combinational circuit 6Sequential circuit 7Sequ的全部内容,更多相关刷完这套题,我才发现Verilog原来如此简单----HDLBits答案系列内容请搜索靠谱客的其他文章。

发表评论 取消回复