一.概念

阻塞赋值 =

在always过程块中,当存在多条阻塞赋值语句时,在前面的赋值语句没有完成之前,后面的语句就不能被执行,阻塞赋值语句顺序执行,就像被阻塞了一样,因此被称为阻塞赋值。

非阻塞赋值 <=

在always过程块中,当存在多条阻塞赋值语句时,多条非阻塞赋值语句同时完成赋值操作,没有丝毫阻塞,因此被称为非阻塞赋值。

二.区别

1.使用上的区别

非阻塞赋值一般用于时序逻辑,阻塞赋值一般用于组合逻辑。

2.在vivado中综合后的区别

(1)在vivado中编写阻塞与非阻塞赋值的代码。

(2)在RTL原理图中观察他们的区别。

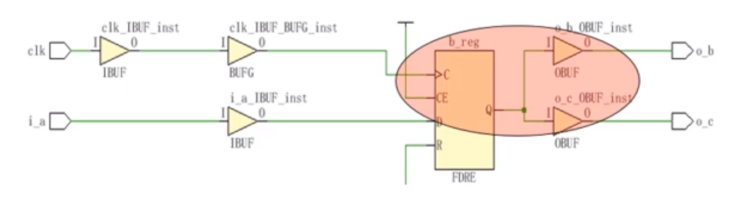

①阻塞赋值

综合后原理图:

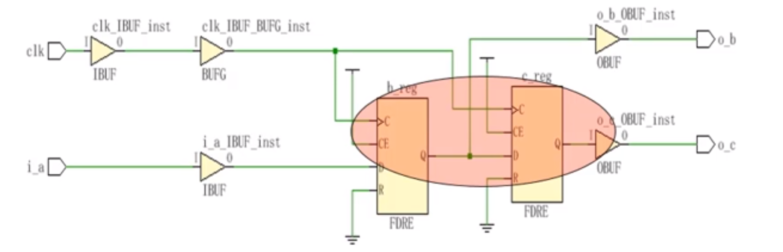

②非阻塞赋值

综合后原理图:

从图中可以看出,阻塞赋值综合出来为触发器,非阻塞赋值综合出来为移位寄存器。

最后

以上就是如意冬天最近收集整理的关于Verilog小心得 | 对阻塞赋值与非阻塞赋值的理解一.概念二.区别的全部内容,更多相关Verilog小心得内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复