前言

当需要采集外部信号时,外部信号多数为模拟信号,如电压、电流、温度、压力等,而单片机只能处理数字信号,这时便需要一个将模拟信号转换为数字信号的介质——模数转换器(ADC),F28335芯片内部自带有12位精度的ADC模块,如果想要更高精度的转换,可以外扩更高位16、24位的ADC模块。

一、AD转换原理介绍

1.1 ADC转换步骤

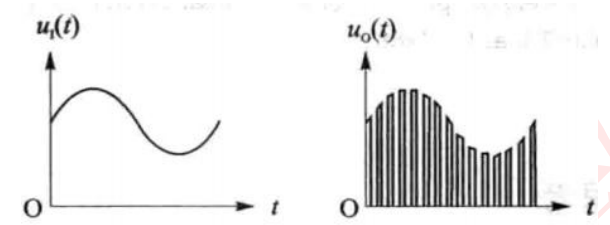

模拟量转换为数字量:采样 保持 量化 编码

采样:将一个时间上连续变化的模拟量转换为时间上离散变化的模拟量;

保持:将采样的结果存储起来,直到下一次采样;

量化:将采样电平归化为与之接近的离散数字电平;

编码:将量化后的结果按照一定数制形式表示;

在编码中:将采样电平(模拟值)转换为数字值时,可通过直接比较型与间接比较型。

直接比较型:就是将输入模拟信号直接与标准的参考电压比较,从而得到数字量。常见的有并行ADC与逐次比较型ADC。

间接比较型:输入模拟量不是直接与参考电压比较,而是将二者变为中间的某种物理量在进行比较,然后将比较所得的结果进行数字编码。常见的有双积分ADC。

1.2 ADC转换原理

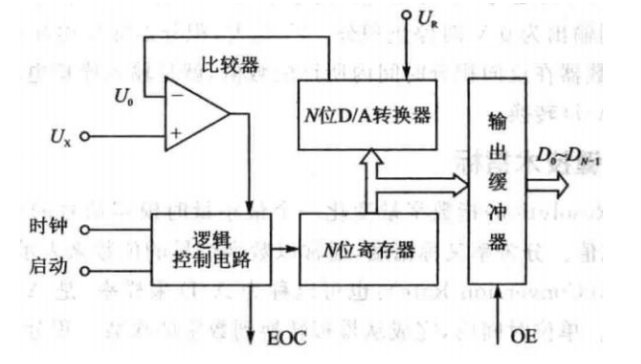

1) 逐次逼近型ADC

采用逐次逼近法的 AD 转换器是有一个比较器、DA 转换器、缓冲寄存器和控 制逻辑电路组成,如下图所示:

基本原理是:从高位到低位逐次试探比较,就像用天平秤物体,从重到轻逐 级增减砝码进行试探。逐次逼近法的转换过程是:初始化时将逐次逼近寄存器各 位清零,转换开始时,先将逐次逼近寄存器最高位置 1,送入 DA 转换器,经 DA 转换后生成的模拟量送入比较器,称为 U0,与送入比较器的待转换的模拟量 Ux 进行比较,若 U0<Ux,该位 1 被保留,否则被清除。然后再将逐次逼近寄存器次 高位置 1,将寄存器中新的数字量送 DA 转换器,输出的 U0 再与 Ux 比较,若 U0<Ux, 该位 1 被保留,否则被清除。重复此过程,直至逼近寄存器最低位。转换结束后, 将逐次逼近寄存器中的数字量送入缓冲寄存器,得到数字量的输出。逐次逼近的 操作过程是在一个控制电路的控制下进行的。

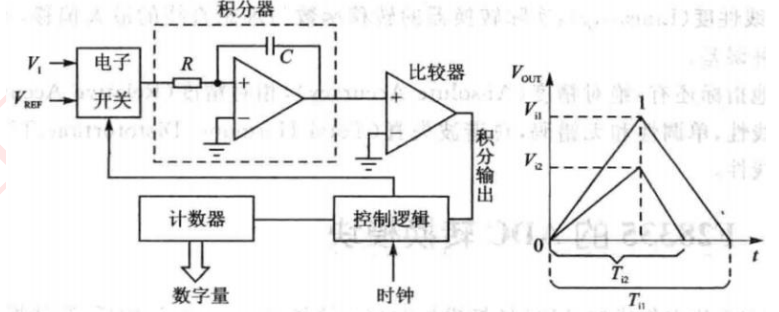

2) 双积分型ADC

采用双积分法的 AD 转换器由电子开关、积分器、比较器和控制逻辑等部件 组成。如下图所示:

其基本原理:将输入电压变换成与其平均值成正比的时间间隔,再把此时间 间隔转换成数字量,属于间接转换。双积分法 AD 转换的过程是:先将开关接通 待转换的模拟量 Vi,Vi 采样输入到积分器,积分器从零开始进行固定时间 T 的 正向积分,时间 T 到后,开关再接通与 Vi 极性相反的基准电压 Vref,将 Vref 输入到积分器,进行反向积分,直到输出为 0V 时停止积分。Vi 越大,积分器输 出电压越大,反向积分时间也越长。计数器在反向积分时间内所计的数值,就是 输入模拟电压 Vi 所对应的数字量,实现了 AD 转换。

1.3 ADC核心技术指标:

1) 分辨率:指数字量变化一个最小量时模拟量信号的变化量,定义为满刻度与2^ n的比值。分辨率又叫做精度,通常以数字信号的位数来表示。精度3/2^ 12,1/2^12为分辨率。

2) 转换速率:采样率,是AD转换一次所需要时间的倒数。单位时间内,完成从模拟转换到数字转换的次数。积分型AD的转换时间是毫秒级属低速AD,逐次比较型AD是微秒级属于中速AD,全并行/串并行型AD可达到纳秒级。

3) 量化误差: 由于AD的有限分辨率而引起的误差,即有限分辨率AD的阶梯状态转移特性与无限分辨率AD(理想AD)的转移特性曲线(直线)之间的最大偏差。通常是1个或半个最小数字量的模拟变换两,表示1LSB、0.5LSB

采样时间是指两次转换的间隔。(一般采样速率必须小于或等于转换速率) 先转换后采样。

4) 偏移误差: 输入信号为0时,输出信号不为零的值。通过外接电位器调至最小。

5) 满刻度误差: 满刻度输出时对应的输入信号与理想信号值之差。

6) 线性度: 实际转换器的转移函数与理想直线的最大偏移,

二、F28335ADC介绍

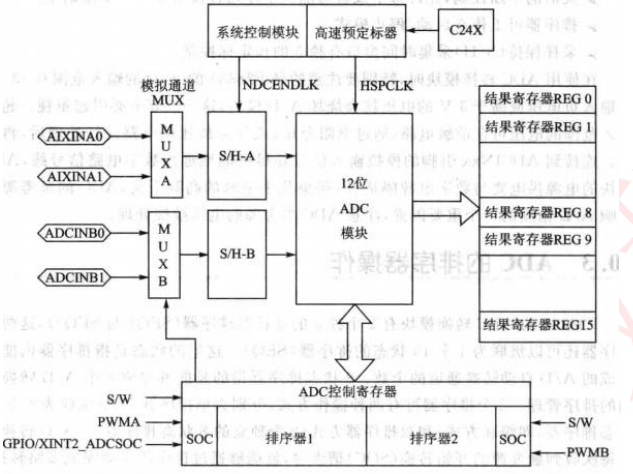

28335AD模块有16个模拟输入源:分为8个A组、8个B组。 AB两个组也可以级联成一个16通道模块。 且该ADC模块核心资源是一个12位的模数转换器。

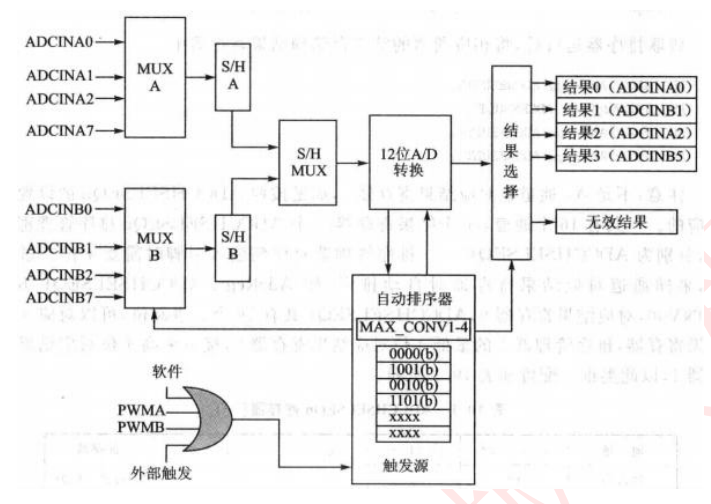

F28335ADC转换模块具有16个通道,由2个独立的8通道组成,这两个独立的8通道也可以级联成一个16通道。尽管AD转换器中有多个输入通道和两个序列发生器,但只有一个转换器。 AD转换器模块的内部结构如下:

两个8通道模块能够自动排序构成一系列转换器,每个模块可以通过模拟的多路开关(MUX)选择8个通道中的任何一个通道。在级联模式下,自动序列发生器是16通道的,对每个序列发生器而言,一旦完成转换,所选通道的转换值将存储到对应的ADCRESULT寄存器中。自动排序过程允许系统对同一个通道进行多次变换,允许用户进行过采样算法从而得到比一般的单采样更精确的结果。

F28335 的 ADC 模块主要包括以下特点:

–12 位模数转换

–2 个采样保持器(S/H)

–同时或顺序采样

–模拟电压输入范围 0-3V

–ADC 转换时钟频率最高可配置为 25MHz,采样带宽 12.5MHz

–16 通道模拟输入

–排序器支持 16 通道独立循环“自动转换”,每次转换通道可以软件编程 选择。

–16 个结果寄存器存放 ADC 转换的结果,转换后的数字量表示为: 数字值=4095*(输入模拟值-ADCLO)/3,输入模拟值在 0-3V 之间

–多个触发源启动 ADC 转换(SOC):

①S/W–软件立即启动

②外部引脚

③ePWMx SOCA 启动

④ePWMx SOCB 启动

–灵活的中断控制,允许每个或者每隔一个序列转换结束产生中断请求

–排序器可工作在启动/停止模式

–采样保持(S/H)采集时间窗口有独立的预定标控制

在使用 ADC 转换模块时,特别要注意的是 F28335 的 AD 的输入范围 0-3V,若 输入负电压或高于 3V 的电压就会烧坏 AD 模块,这一点要务必引起重视。超出输 入范围的电压可在前级电路,通过电阻进行分压,或经运放比例电路进行处理后 再输入。连接到 ADCINxx 引脚的模拟输入信号要尽可能的远离数字电路信号线, ADC 模块的电源供电要与数字电源电源隔离开,避免数字电源的高频干扰,ADC 的参考源是影响 AD 精度的一个重要因数,注意 ADC 参考源的电压纹波处理。

2.1 排序器的工作原理:

F28335的ADC转换模块有2个独立的8状态排序器(SEQ1与SEQ2),这两个排序器还可以级联为1个16状态的排序器(SEQ)。这里的状态是指排序器内能够完成的AD自动转换通道的个数。8状态排序器指的是能够完成8个AD转换通道的排序管理。

2个排序器还可以有两种操作方式:

单排序器方式(级联为1个16状态排序器,即级联方式)和双排序器方式(2个独立的8状态排序器)。

AD转换模块每次收到触发源的开始转换SOC请求,就能够通过排序器自动完成多路转换,将模拟输入信号引入采样保持器与ADC内核转换完成后,将转换结果存入结果寄存器。

两种操作方式最大差别就在于:单排序操作方式响应触发源是唯一的,可双排序的方式可以分别响应各自的触发源。

两种工作方式都可以进行顺序采样或者同步采样,两种采样的方式最大的不同在于,顺序采样相当于串行模式;同步采样相当于并行模式,能保证信号的同时性,显然同时同步采样要求会更好一点。

1) 级联操作方式

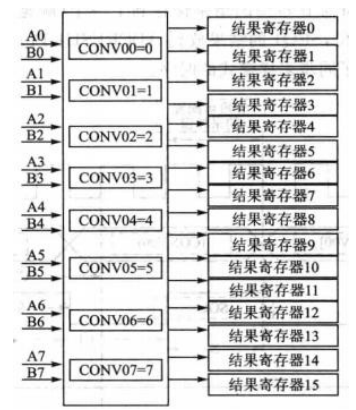

排序器级联方式内部结构图如下:

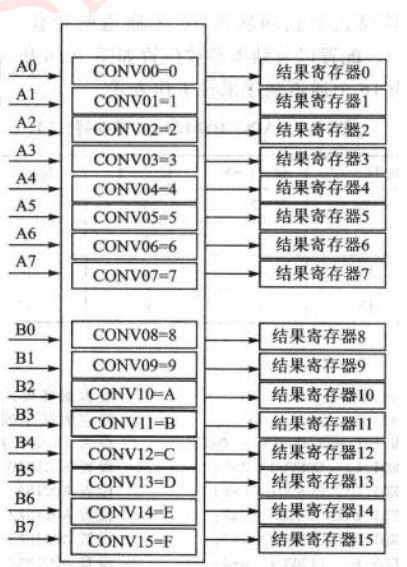

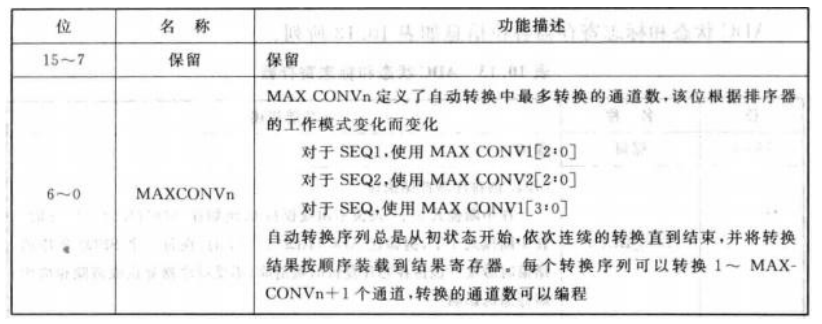

启动ADC之前,首先要进行一些初始化的工作,初始化转换的最多通道数(MAX_CONV),这个参数限制了最多有效通道数,对于级联模式,最大为16,在双排序方式下,最大为8。假如输入信号为6,设置值为4,实际只有4个输入有效通道。配置需要的转换输入信号对应的转换次序(CHSELxx),最终的转换结果放在各自的结果寄存器中,结果寄存器不与输入通道完全对应,而是结果寄存器与转换次序对应。16通道对应结果寄存器如下:

1.1) 级联排序器顺序采样模式

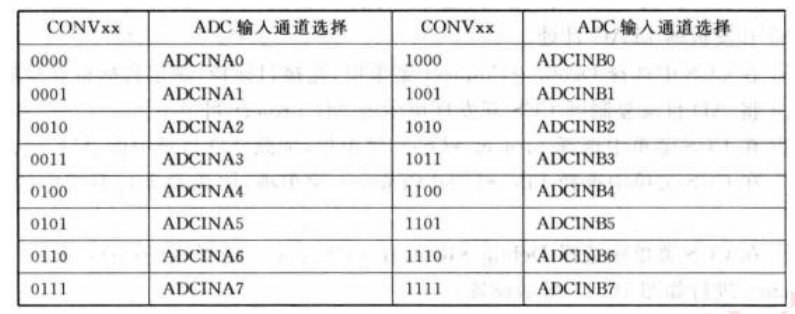

在级联排序器操作方式下,2个8状态排序器(SEQ1和SEQ2)构成一个16状态排序器SEQ控制外部输入的模拟的模拟信号的排序,通过控制寄存器CONVxx的4位值确定输入引脚,其中最高位确定采用哪个采样保持缓冲器,其他3位定义具体的输入引脚。两个采样保持器对应各自的8选1多路选择器和8个输入通道。

1.2) 级联排序同步采样模式

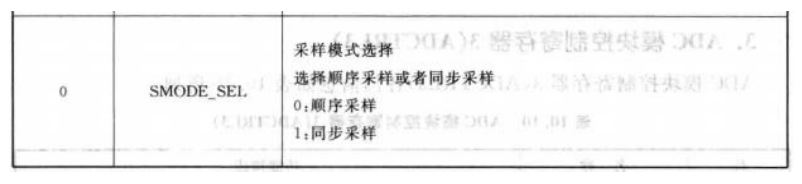

如果一个输入来自 ADCINA0-ADCINA7,另一个输入来自 ADCINB0-ADCINB7, ADC 能够实现 2 个 ADCINxx 输入的同时采样。此外,要求 2 个输入必须有同样的 采样和保持偏移量(比如 ADCINA4 和 ADCINB4,不能是 ADCINA7 和 ADCINA6)。 为了让 ADC 模块工作在同步采样模式,必须设置 ADCTRL3 寄存器中的 SMODE_SEL 位为 1。

在同步采样模式下,CONVxx 寄存器的最高位不起作用,每个采样和保持缓冲 器对 CONVxx 寄存器低 3 位确定的引脚进行采样。例如,如果 CONVxx 寄存器的值 是 0110b,ADCINA6 就由采样保持器 A 采样,ADCINB6 有采样保持器 B 采样,和 1110b 的效果是一样的,如果 CONVxx 寄存器的值是 1001b,ADCINA1 由采样和保 持器 A 采样,ADCINB1 由采样和保持器 B 采样。采样保持两路可以同步进行,因 为有两个采样保持器,但是转换不可能同时进行。转换器首先转换采样保持器 A 中锁存的电压量,然后转换采样保持器 B 中锁存的电压量。采样保持器 A 转换的 结果保存到当前的 ADCRESULTn 寄存器(如果排序器已经复位,SEQ1 的结果放到 ADCRESULT0),采样保持器 B 转换的结果保存到下一个(顺延)ADCRESULTn 寄 存器(如果排序器已经复位,SEQ1 的结果放到 ADCRESULT1),结果寄存器指针 每次增加 2。

2) 双排序器操作方式

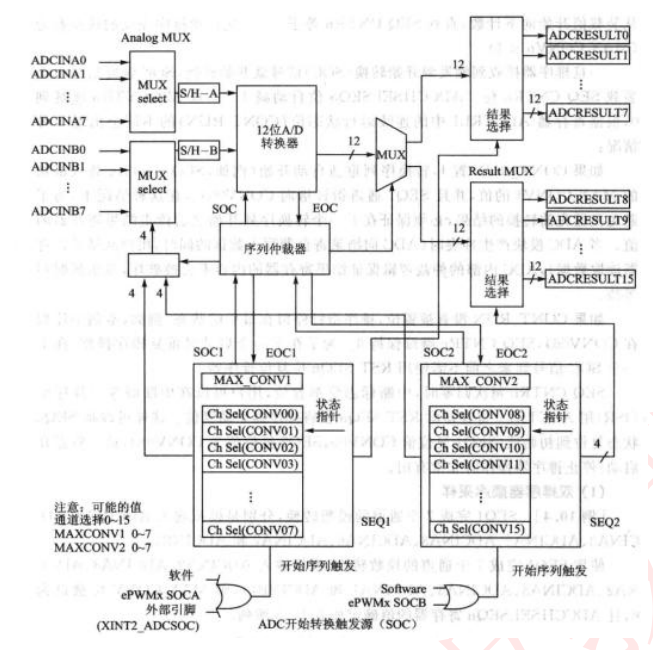

双排序器方式内部结构图如下:

当 ADC 工作在双排序器工作方式下时,2 个 8 状态排序器(SEQ1 和 SEQ2)彼 此独立。在这种方式下 PWMA 触发 SEQ1,PWMB 触发 SEQ2,触发源是独立的。双 排序器工作方式可以将 ADC 看成两个独立的 AD 转换单元,每个单元由各自的触 发源触发转换。

在双排序器连续采样模式下,一旦当前工作的排序器完成排序,任何一个排 序器的挂起 ADC 开始转换都会开始执行。例如,当 SEQ1 产生 ADC 开始转换请求 时,AD 单元正在对 SEQ2 进行转换,完成 SEQ2 的转换后会立即启动 SEQ1。SEQ1 排序器有更高的优先级,如果 SEQ1 和 SEQ2 的 SOC 请求都没有挂起,并且 SEQ1 和 SEQ2 同时产生 SOC 请求,则 ADC 完成 SEQ1 的有效排序后,将会立即处理新的 SEQ1 的转换请求,SEQ2 的转换请求处于挂起状态。

双排序方式使用了 2 个排序器,SEQ1/SEQ2 能在一次排序过程中对 8 个任意 通道进行排序转换。每次转换结果保存在相应的结果寄存器中,这些寄存器由低 地址到高地址依次填充。

每个排序器中的转换通道个数依然受 MAXCONVn 控制,最大控制通道数为 7, 而不是前面的 16。该值在自动排序转换的开始时被载到自动排序状态寄存器 (AUTO_SEQ_SR)的排序计数器控制位(SEQ CNTR3-0),MAX CONVn 的值在 0-7 内变化。当排序器安排内核从 CONV00 开始按顺序转换时,SEQ CNTRn 的值从装 载值开始向下计数,直到 SEQ CNTRn 为 0.一次自动排序完成的转换数为 MAX

CONVn+1。

一旦排序器接收到触发源开始转换(SOC)信号就开始转换,SOC 触发信号也 会装载 SEQ CNTRn 位,ADCCHSELSEQn 位自动减 1。一旦 SEQCNTRn 递减到 0,根 据寄存器 ADCTRL1 中的连续运行状态位(CONT_RUN)的不同会出现 2 种情况:

①如果 CONT_RUN 置 1,转换序列重新自动开始(比如 SEQ_CNTRn 装入最初的 MAX_CONV1 的值,并且 SEQ1 通道指针指向 CONV00)。在这种情况下,为了避免 覆盖先前转换的结果,必须保证在下一个转换序列开始之前读走结果寄存器的 值。当 ADC 模块产生冲突时(ADC 向结果寄存器写入数据的同时,用户从结果寄 存器读取数据),ADC 内部的仲裁逻辑保证结果寄存器的内容不会被破坏,发出 延时写等待。

②如果 CONT_RUN 没有置位,排序指针停留在最后的状态,SEQ_CNTRn 继续保 持 0。为了在下一个启动时重复排序操作,在下一个 SOC 信号到来之前不需使用 RST_SETQn 位复位排序器。 SEQ_CNTRn 每次归零时,中断标志位都置位,用户可以在中断服务子程序中 用 ADCTRL2 寄存器的 RST_SETQn 位将排序器手动复位。这样可以将 SETQn 状态复 位到初始值(SEQ1 复位值 CONV00,SEQ2 复位值 CONV08),这一特点在启动/停止排序器操作时非常有用。

2.1) 双排序器顺序采样

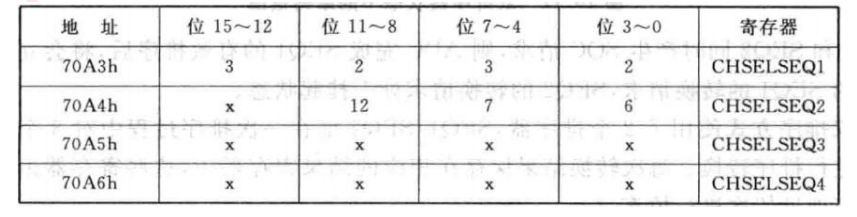

【例①】SEQ1 完成 7 个通道的模数转换,分别是模拟输入 ADCINA2、ADCINA3、 ADCINA2、ADCINA3、ADCINA6、ADCINA7 和 ADCINB4。

使用 SEQ1 完成 7 个通道的模数转换(模拟输入 ADCINA2、ADCINA3、ADCINA2、 ADCINA3 、ADCINA6 、 ADCINA7 和 ADCINB4) , 则 MAX_CONV 应 被 设为 6 ,且 ADCCHSELSEQn 寄存器的值确定如下所示:

2.2) 双排序器同步采样

如果一个输入来至 ADCINA0-ADCINA7,另一个输入来至 ADCINB0-7,ADC 能够实现 2 个 ADCINxx 输入的同时采样。此外要求 2 个输入必须有同样的采样保持偏 移量(如 ADCINA4 和 ADCINB4,不能是 ADCINA7 和 ADCINB6)。为了让 ADC 模块 工作在同步采样模式,必须设置 ADCTRL3 寄存器中的 SMODE_SEL 位为 1.在同步 采样模式下,双排序器同级联排序器相比,主要区别在于排序器控制:在双排序 器中每个排序器分别控制 4 个转换 8 个通道,共构成 16 通道,而在级联排序器 的同步采样模式下,实际只是用 SEQ1 作为排序器,控制 8 个转换 16 个通道。

下面给出了双排序器模式下同步采样设计例子。

【例②】双排序器同步采样模式 ADC 应用实例

AdcRegs.ADCTRL3.bit.SMODE_SEL = 1;//设置同步采样模式 AdcRegs.ADCMAXCONV.bit.MAX_CONV1 = 0x33;//设置 4 对转换,共 8 通道 AdcRegs.ADCCHSELSEQ1.bit.CONV00 = 0x0;//设置 ADCINA0 和 ADCINB0 AdcRegs.ADCCHSELSEQ1.bit.CONV01 = 0x1;//设置 ADCINA1 和 ADCINB1 AdcRegs.ADCCHSELSEQ1.bit.CONV02 = 0x2;//设置 ADCINA2 和 ADCINB2 AdcRegs.ADCCHSELSEQ1.bit.CONV03 = 0x3;//设置 ADCINA3 和 ADCINB3 AdcRegs.ADCCHSELSEQ3.bit.CONV08 = 0x4;//设置 ADCINA4 和 ADCINB4 AdcRegs.ADCCHSELSEQ3.bit.CONV09 = 0x5;//设置 ADCINA5 和 ADCINB5 AdcRegs.ADCCHSELSEQ3.bit.CONV10 = 0x6;//设置 ADCINA6 和 ADCINB6 AdcRegs.ADCCHSELSEQ3.bit.CONV11 = 0x7;//设置 ADCINA7 和 ADCINB7 AdcRegs.ADCTRL2.bit.EPWM_SOCA_SEQ1 = 1;//使能 PWMA SOC 触发 AdcRegs.ADCTRL2.bit.INT_ENA_SEQ1 = 1;//使能 SEQ1 中断

SEQ1 和 SEQ2 同时运行,将相应通道的转换结果存储到结果寄存器中:

3) 排序器启动/停止模式

排序器的启动/停止模式是相对于连续的自动排序模式而言的,任何一个排 序器(SEQ1、SEQ2 或 SEQ)都可以工作在启动/停止模式,这种方式可在不同时 间上分别和多个启动触发信号同步。一旦排序器完成了第一个排序(假定排序器 在中断服务子程序中未被复位),可允许排序器不需要复位初始状态 CONV00 情 况下重新触发排序器。因此当一个转换序列结束时,排序器就停止在当前转换状 态。在这种工作模式下,ADCTRL1 寄存器中的连续运行位(CONT_RUN)必须设置 为 0。

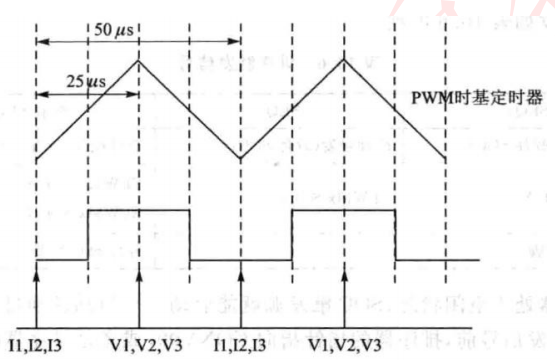

【例①】排序器启动/停止操作模式:要求触发源 1 启动 3 个自动转换 (I1I2I3),触发源 2 启动 3 个自动转换(V1V2V3)。触发源 1 和触发源 2 在时间上是独立的,间隔 25us,触发信号由 ePWM 提供。如下图所示,这里只使 用 SEQ1。

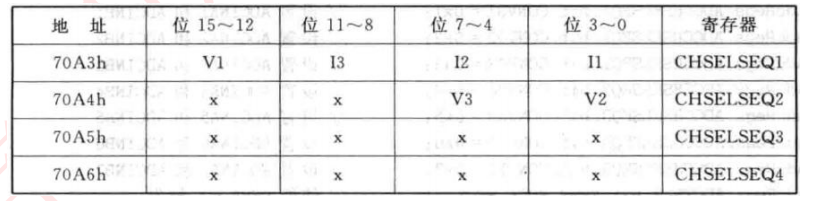

在这种情况下,MAX_CONV1 的值设置为 2,ADC 模块的输入通道选择排序控制 寄存器(ADCCHSELSEQn)应按下图所示设置值。

一旦复位和初始化完成,SEQ1 就等待触发。第一个触发到来之后,执行通道 选择值为 CONV00(I1)、CONV01(I2)和 CONV02(I3)的 3 个转换。转换完成 后,SEQ1 停在当前的状态等待下一个触发源,25us 后另一个触发源到来,ADC 模块开始选择通道为 CONV03(V1)、CONV04(V2)和 CONV05(V3)的 3 个转换。

对于这两种触发,MAX_CONV1 的值会自动地装入 SEQ_CNTRn 中。如果第 2 个 触发源要求转换的个数与第 1 个不同,用户必须通过软件在第 2 个触发源到来之 前改变 MAX_CONV1 的值,否则 ADC 模块会重新使用原来的 MAX_CONV1 的值。可以使用中断服务程序 ISR 适当的改变 MAX_CONV1 的值。

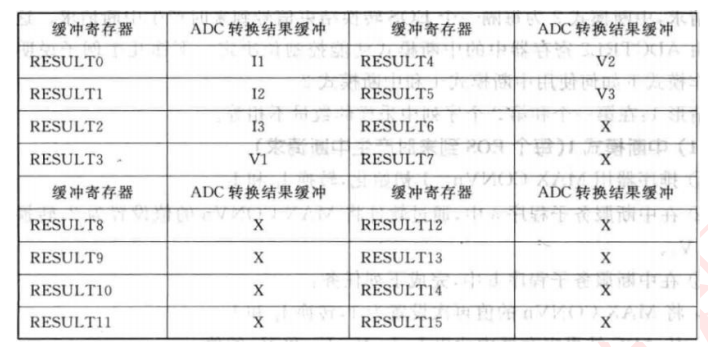

在第 2 个转换序列完成之后,ADC 模块的转换结果存储到相应的寄存器,如下图所示:

第 2 个转换序列完成后,SEQ1 保持在下一个触发的等待状态。用户可以通过 软件复位 SEQ1,将指针指导 CONV00,重复同样的触发源 1、2 转换操作。

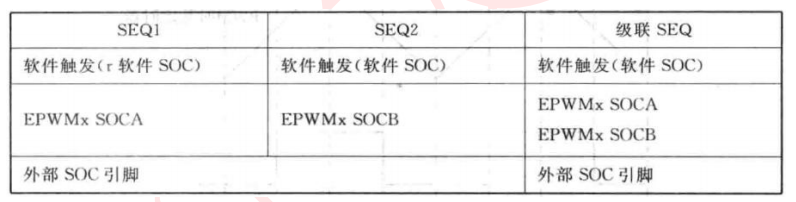

4) 输入触发源

每个排序器都有一系列可以使能或禁止的触发源。SEQ1、SEQ2 和级联 SEQ 的有效输入触发源如下图所示:

只要排序器处于空闲状态,SOC 触发源就能启动一个自动转换排序器。空闲 状态是指在收到触发信号前,排序器的指针指向 CONV00,或者是排序器已经完 成了一个转换排序,也就是 SEQ_CNTRn 为 0。如果转换序列正在运行时,到来一 个新的 SOC 触发信号,则 ADCTRL2 寄存器中的 SOC_SEQn 位置 1(该位在前一个 转换开始时已经清除)。但如果又一个 SOC 触发信号到来,则该信号将被丢失, 也就是当 SOC_SEQn 位置 1 时(SOC 挂起),随后的触发不起作用。被触发后, 排序器不能在中途停止或中断。程序必须等到一个序列的结束或复位排序器,才 能使排序器恢复到初始空闲状态(SEQ1 和级联的排序器指针指向 CONV00,SEQ1 的指针指向 CONV08)。当 SEQ1/2 用于级联同步采样模式时,SEQ2 的触发源被忽 略,SEQ1 的触发源有效。因此级联模式可以看做 SEQ1 有 16 个转换通道。

只要排序器处于空闲状态,SOC 触发源就能启动一个自动转换排序器。空闲 状态是指在收到触发信号前,排序器的指针指向 CONV00,或者是排序器已经完 成了一个转换排序,也就是 SEQ_CNTRn 为 0。如果转换序列正在运行时,到来一 个新的 SOC 触发信号,则 ADCTRL2 寄存器中的 SOC_SEQn 位置 1(该位在前一个 转换开始时已经清除)。但如果又一个 SOC 触发信号到来,则该信号将被丢失, 也就是当 SOC_SEQn 位置 1 时(SOC 挂起),随后的触发不起作用。被触发后, 排序器不能在中途停止或中断。程序必须等到一个序列的结束或复位排序器,才 能使排序器恢复到初始空闲状态(SEQ1 和级联的排序器指针指向 CONV00,SEQ1 的指针指向 CONV08)。当 SEQ1/2 用于级联同步采样模式时,SEQ2 的触发源被忽 略,SEQ1 的触发源有效。因此级联模式可以看做 SEQ1 有 16 个转换通道。

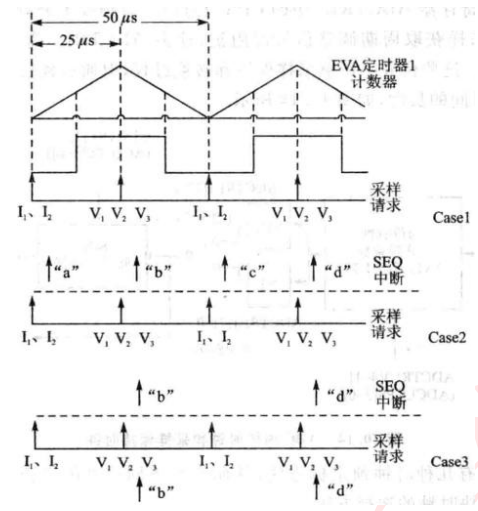

5) 排序器转换的中断操作

排序器有两种中断工作模式,中断模式 1 为每个 EOS 转换结束信号到来时产生中断请求,中断模式 2 为每隔一个 EOS 转换结束信号到来时产生中断请求。这 两种方式由 ADCTRL2 寄存器中的中断模式使能控制位决定。下面我们用几个例子 说明在不同工作模式下如何使用中断模式 1 和中断模式 2。

情形 1:在第 1 个和第 2 个序列中采样的数量不相等。

(1)中断模式 1(每个 EOS 到来时产生中断请求)

①排序器用 MAX_CONVn=1 初始化,转换 I1 和 I2。

②在中断服务子程序 a 中,通过软件将 MAX_CONVn 的值设为 2,转换 V1、V2 和 V3。

③在中断服务子程序 b 中,完成下列任务:

–将 MAX_CONVn 的值再次设置为 1,转换 I1 和 I2。

–从 ADC 结果寄存器中读出 I1、I2、V1、V2 和 V3 的值。

–复位排序器。

④重复操作第②、③步。每次 SEQ_CNTRn 等于 0 时产生中断,并且中断能够被识别。

情形 2:在第 1 个和第 2 个序列中采样的数量相等。

(2)中断模式 2 操作(每隔一个 EOS 信号产生中断请求)

①排序器设置 MAX_CONVn=2 初始化,转换 I1、I2、I3 或 V1、V2 和 V3。

②在服务子程序 b 和 d 中,完成下列任务。

–从 ADC 结果寄存器中读出 I1、I2、I3 或者 V1、V2 和 V3 的值。

–复位排序器。 --重复第②步。

情形 3:两个序列的采样个数是相等的(带空读)

(3)中断模式 2(隔一个 EOS 信号产生中断请求)

①MAX_CONVn=2,初始化序列器,转换 I1、I2 和 x(空采样)。

②在中断服务子程序 b 和 d 中,完成下列任务:

–从 ADC 结果寄存器中读出 I1、I2、x、V1、V2 和 V3 的值。

–复位排序器。

–重复第②步。在①中,I1、I2 后的 X 采样为一个空的采样,其实并没有要 求采样。然而利用模式 2 间隔产生中断请求的特性,可以减小中断服务子程序和CPU 的开销。

如下图所示 ADC 在序列转换过程中的中断操作的时序:

6) 排序器覆盖功能

通常在运行模式下,排序器 SEQ1、SEQ2 或者级联 SEQ 用于选择 ADC 通道, 并将转换的结果存储在相应的 ADCRESULTn 寄存器中。在 MAX_CONVn 设置的转换 结束时,排序器自动返回 0。在使用排序器覆盖功能时,排序器的自动返回可通 过软件控制,这由 ADC 控制寄存器 1(ADCCTRL1)的第 5 位控制。例如假定 SEQOVRD 位为 0,ADC 工作在级联模式下的连续转换模式,MAX_CONV1 设置为 7,通常情况 下,排序器会递增并将 ADC 转换结果更新结果寄存器到 ADCRESULT7 寄存器,然 后返回到 0,。当 ADCRESULT7 寄存器更新完成后,相应的中断标志位被置位。当 SEQ_OVRD 位被重新置位,排序器在更新 7 个结果寄存器后不再回绕到 0,而将继 续增加,并更新 ADCRESULT8 寄存器,直到 ADCRESULT15 为止。ADCRESULT15 寄 存器更新完毕再返回到 0。这可以将结果寄存器看成 FIFO,用于 ADC 对连续数据 的捕捉。当 ADC 在最高数据速率下进行转换时,这个功能有助于捕捉 ADC 的数据。

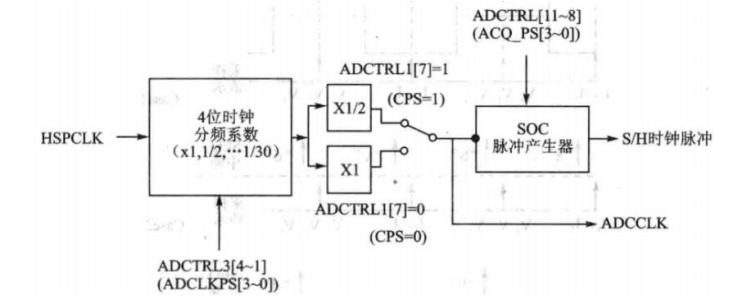

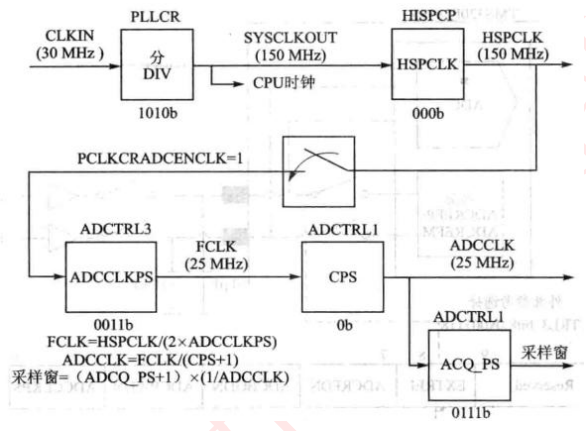

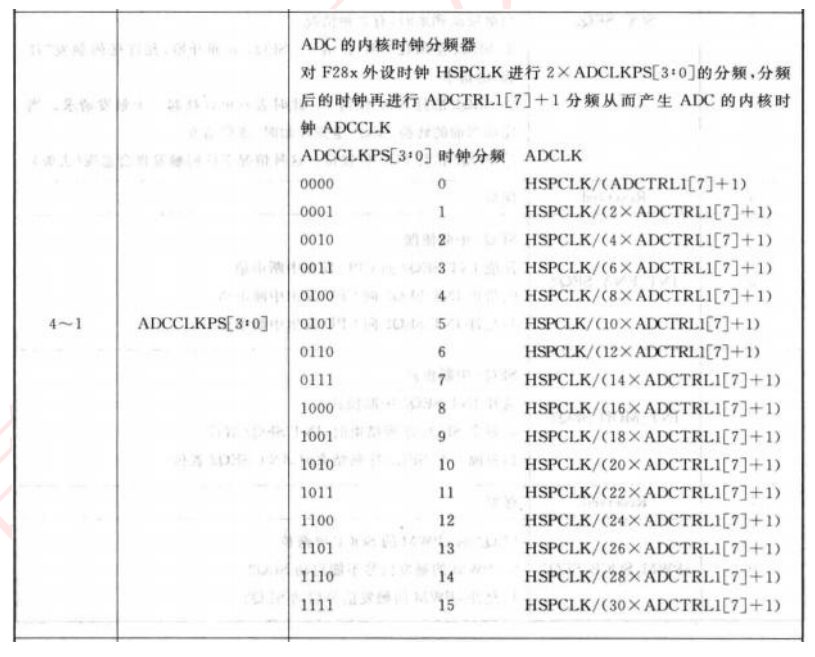

2.2 ADC时钟控制

外设时钟 HSPCLK 是通过 ADCTRL3 寄存器的 ADCCLKPS[3-0]位来分频的,然后 再通过寄存器 ADCTRL1 中的 CPS 位进行 2 分频或者不分频。此外,ADC 模块还通 过扩展采样获取周期调整信号源阻抗,这由 ADCTRL1 寄存器中的 ACQPS3-0 位控 制。这些位并不影响采样保持和转换过程,但通过延长转换脉冲的长度可以增加采样时间的长度,如下图所示:

ADC 模块有几种时钟预定标方法,从而产生不同速度的操作时钟。如下图所 示,图中给出了 ADC 模块时钟的选择方法。

2.3 相关寄存器

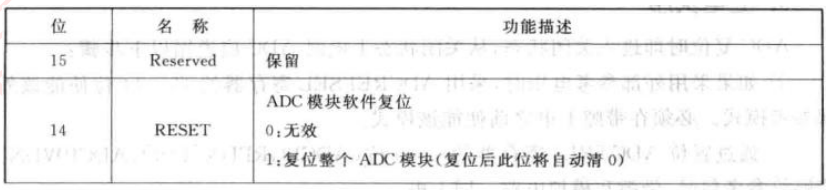

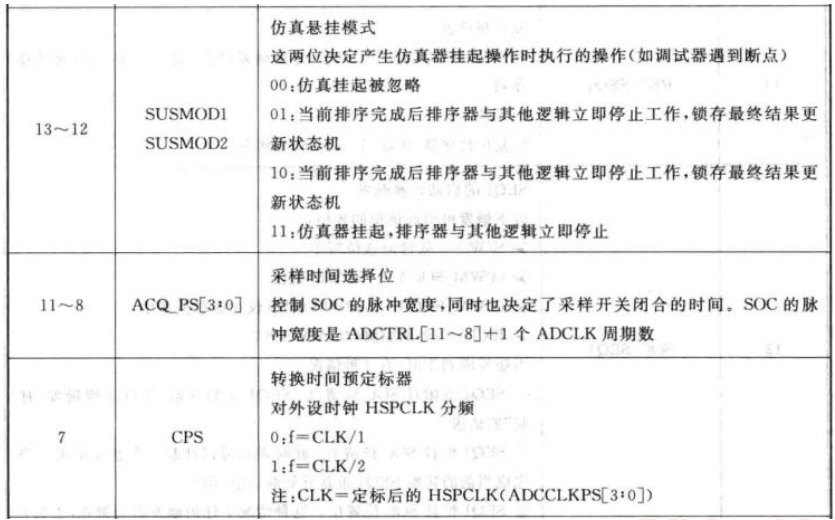

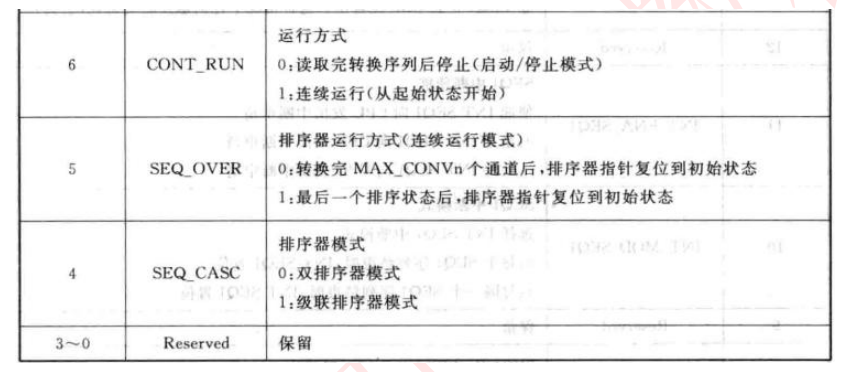

(1)ADC 模块控制寄存器 1(ADCTRL1)

ADC 模块控制寄存器 1(ADCTRL1)各位功能描述如下:

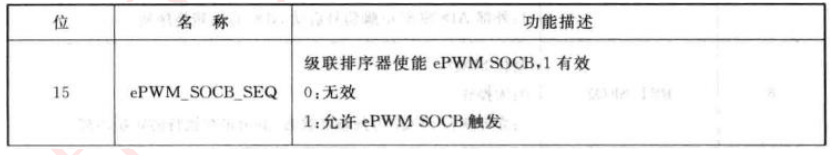

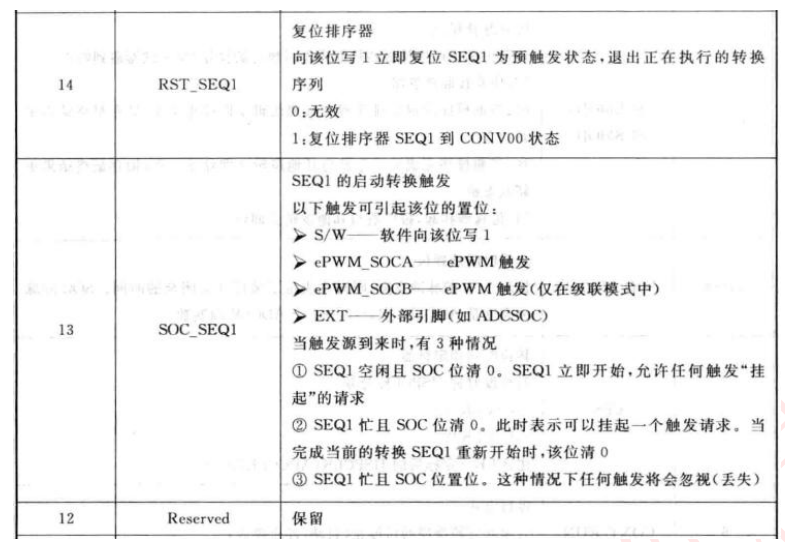

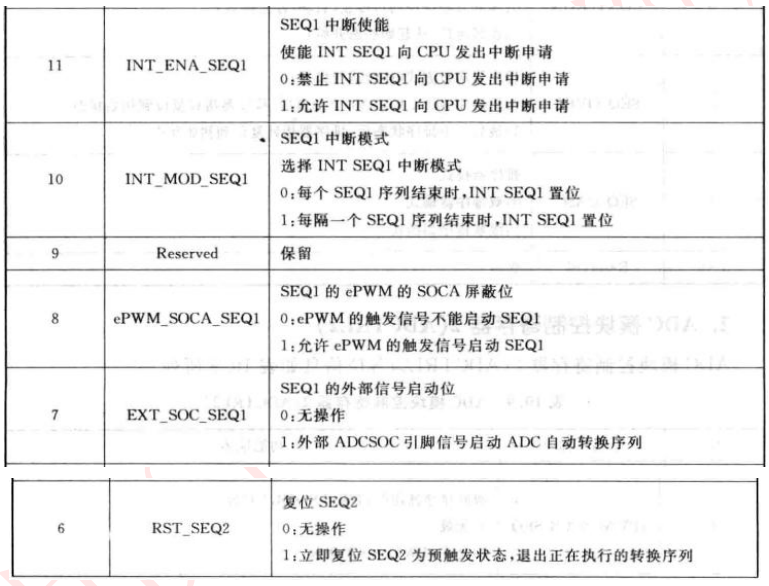

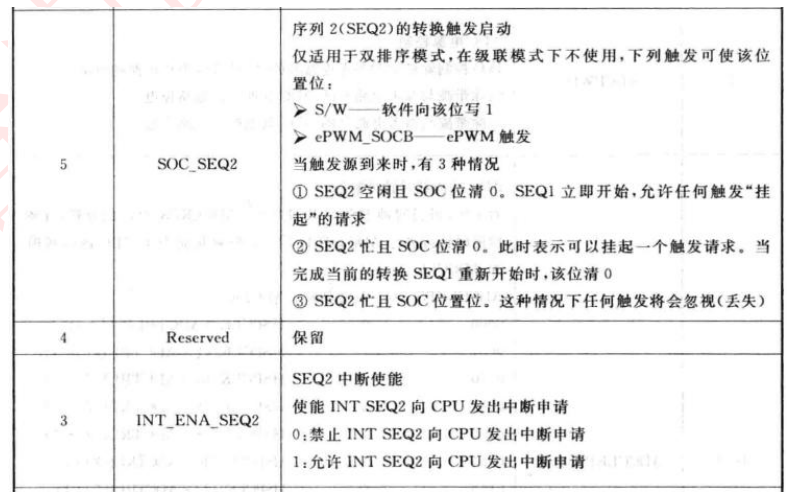

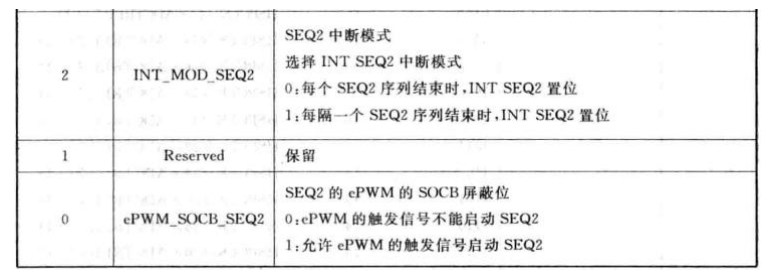

(2)ADC 模块控制寄存器 2(ADCTRL2)

ADC 模块控制寄存器 2(ADCTRL2)各位功能描述如下:

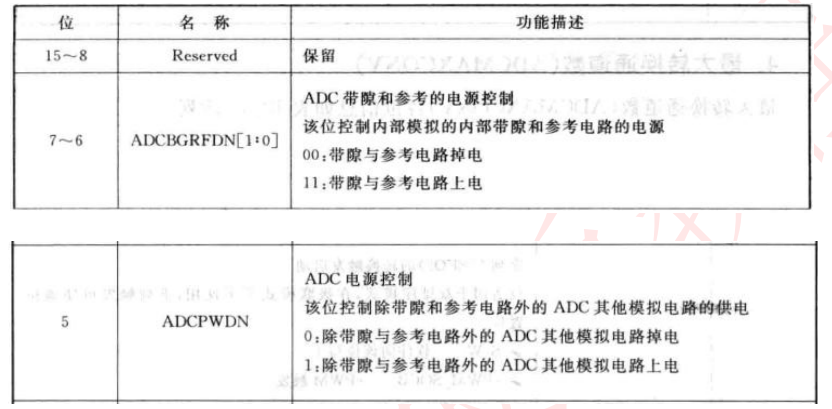

(3)ADC 模块控制寄存器 3(ADCTRL3)

ADC 模块控制寄存器 3(ADCTRL3)各位功能描述如下:

(4)最大转换通道数(ADCMAXCONV)

最大转换通道数(ADCMAXCONV)各位功能描述如下:

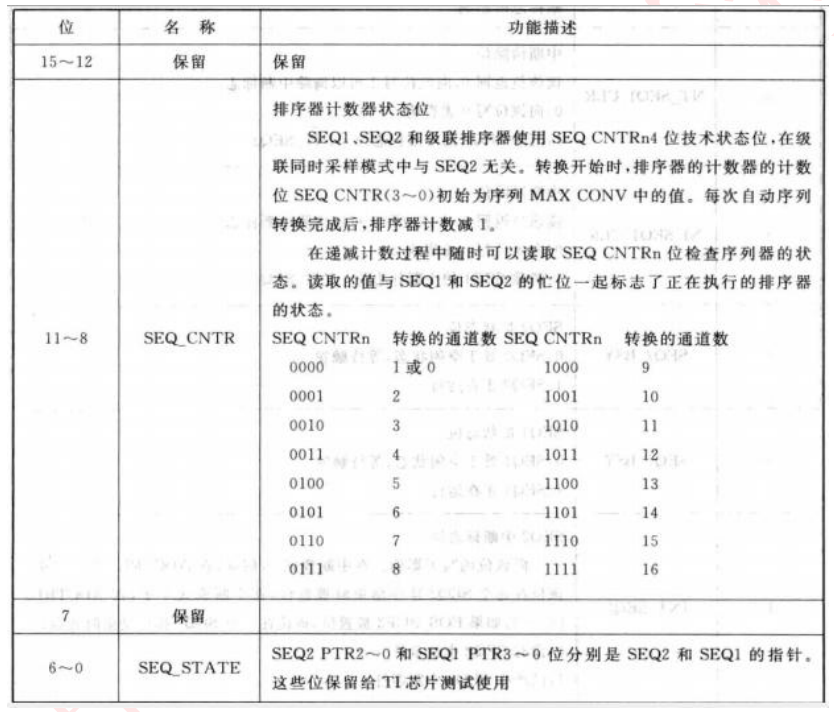

(5)自动排序状态寄存器(ADCASEQSR)

自动排序状态寄存器(ADCASEQSR)各位功能描述如下:

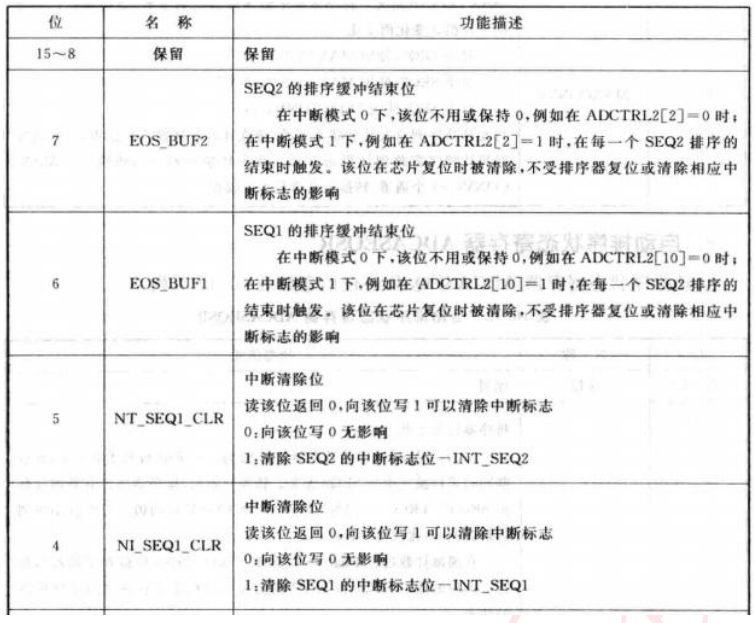

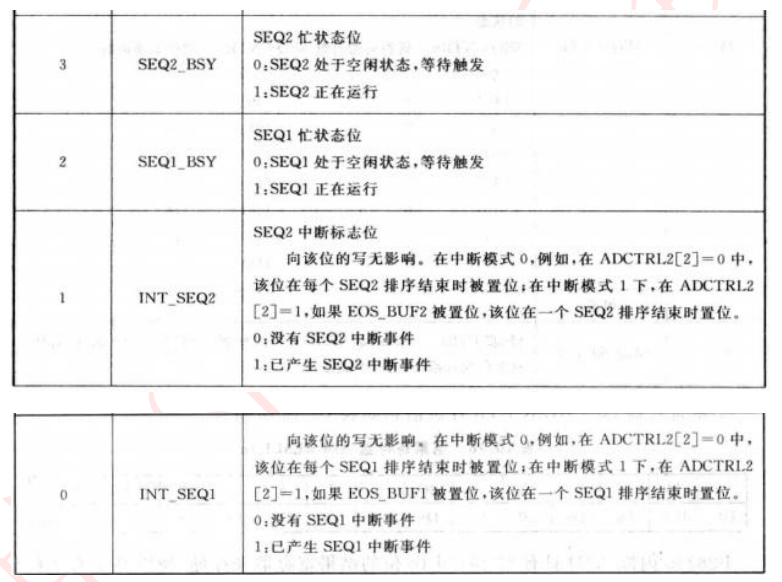

(6)ADC 状态和标志寄存器

ADC 状态和标志寄存器各位功能描述如下:

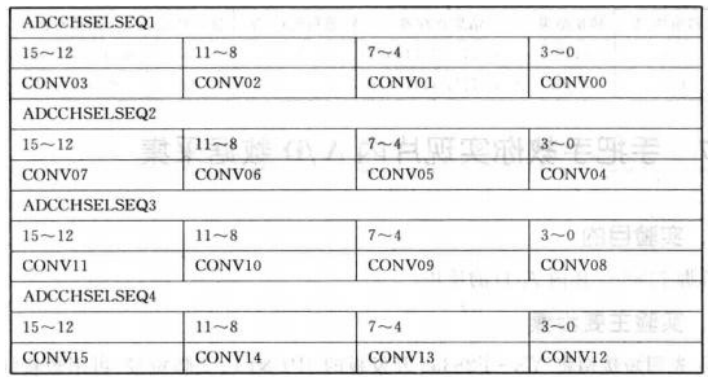

(7)ADC 输入通道选择排序控制寄存器

ADC 输入通道选择排序控制寄存器各位功能描述如下:

每 4 位 CONVxx 可以为一次自动排序转换选定 16 个 ADC 输入通道中的一个通 道,如下图所示:

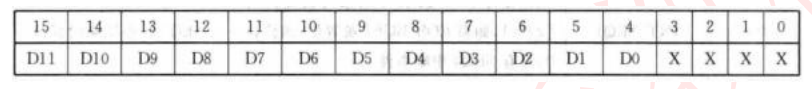

(8)结果寄存器(ADCRESULTn)

结果寄存器各位功能描述如下:

三、ADC配置步骤

(1)使能 ADC 外设时钟及设置 ADC 工作时钟

要使用 ADC 外设则需开启相应时钟,开启 ADC 外设时钟代码如下:

EALLOW;

SysCtrlRegs.PCLKCR0.bit.ADCENCLK = 1; // ADC

EDIS;

系统时钟 150M 不能直接供 ADC 工作时钟使用,需分频后才行,这个在前面ADC 时钟源部分已经介绍,最大为 25MHz。

EALLOW;

SysCtrlRegs.HISPCP.all = 3; // HSPCLK = SYSCLKOUT/(2*3)=25MHz

EDIS;

(2)ADC 初始化设置,包括对 ADCREFSEL 和 ADCOFFTRIM 寄存器设置等。

前面我们介绍 ADC 说过,使用 ADC 时除了开启外设时钟外,还需要对参考电 压寄存器设置,并且在 ADC 开始转换前需要一定的延时。TI 已经提供了一个函 数完成该初始化。调用的 ADC 初始化函数如下:

void InitAdc(void);

该函数在 TI 提供的 DSP2833x_Adc.c 文件内可查找到,内部实现过程如下:

void InitAdc(void)

{

extern void DSP28x_usDelay(Uint32 Count);

EALLOW;

SysCtrlRegs.PCLKCR0.bit.ADCENCLK = 1;//使能 ADC 时钟

ADC_cal();//调用 ADC_cal 汇编程序,它是 TI 提供的 ADC 校准程序,直接使用即可

EDIS;

AdcRegs.ADCTRL3.all = 0x00E0; // Power up bandgap/reference/ADC circuits/顺序采样

DELAY_US(ADC_usDELAY); // 在 ADC 转换前需要一定延时

}

(3)ADC 工作方式设置,包括采样方式、工作频率、采样通道数等。 上一步是对 ADC 内部参考源及校准等设置,只需调用 TI 提供给我们的函数 即可,对于 ADC 工作方式的设置需要我们自己编程实现。这里就以本章实验代码 为例介绍,

代码如下:

AdcRegs.ADCTRL1.bit.ACQ_PS = 0x0f;//顺序采样方式

AdcRegs.ADCTRL3.bit.ADCCLKPS = 1;//ADC 工作 25M 下不分频 AdcRegs.ADCTRL1.bit.SEQ_CASC = 1;// 1 通道模式

AdcRegs.ADCCHSELSEQ1.bit.CONV00 = 0x0;//A0 为采样通道

AdcRegs.ADCTRL1.bit.CONT_RUN = 1;//连续采样模式

AdcRegs.ADCMAXCONV.bit.MAX_CONV1 = 0x0;//最大采样通道数,因为只用 到 A0,所以只有 1 个,即数值为 0。

(4)选择 ADC 触发方式,开启转换。

上述配置好后,接下来就需要设置 ADC 的触发方式,前面介绍过,ADC 触发 方式有几种,软件触发、PWM 触发等,本章实验代码采用软件触发。实现代码如 下:

(5)读取 ADC 转换值

通过上面几步配置,ADC 就开启工作了,接下来我们要做的就是等待转换结 束后,读取转换结果值就可以了。通过前面介绍我们知道,ADC 转换后的数据存 储在结果寄存器内,只需读取相应的结果寄存器即可,并且有效数据是高 12 位, 所以读取后的值要将低 4 位移除。比如读取结果寄存器 0 的转换结果,代码如下:

Uint16 Read_ADCValue(void)

{

while (AdcRegs.ADCST.bit.INT_SEQ1== 0);//查询转换是否结束

AdcRegs.ADCST.bit.INT_SEQ1_CLR = 1;//清除中断标志位

return AdcRegs.ADCRESULT0>>4;//将转换结果返回出去

}

至此我们就将 ADC 的配置步骤介绍完了,按照上面的操作步骤配置 ADC,可 以实现简单的 ADC 检测转换功能。

最后

以上就是年轻芒果最近收集整理的关于ADC数模转换前言一、AD转换原理介绍二、F28335ADC介绍三、ADC配置步骤的全部内容,更多相关ADC数模转换前言一、AD转换原理介绍二、F28335ADC介绍三、ADC配置步骤内容请搜索靠谱客的其他文章。

发表评论 取消回复