目录

边缘对齐采样

时序图

更改PLL参数

综合布线

report timing

路径分析

两种约束模型

第一种模型

实际操作

添加约束

路径分析

第二种模型

顶层代码

添加时钟约束

解决办法

input delay约束

综合布线

结果

总结

往期系列博客

边缘对齐采样

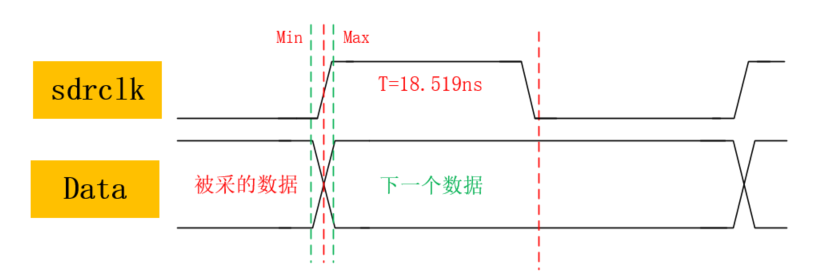

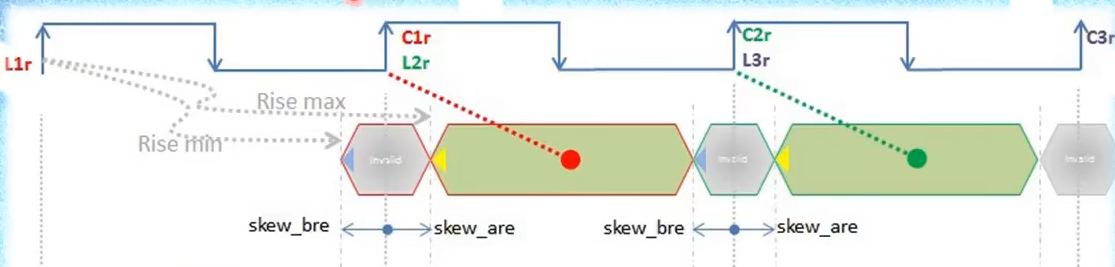

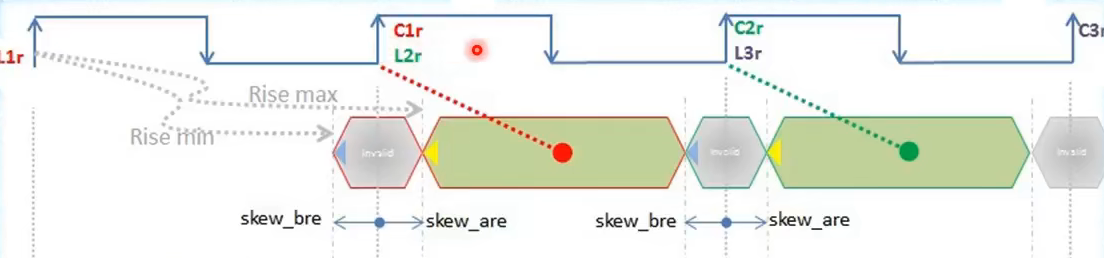

边缘对齐采样的方式进行input delay约束,在系列第八讲中介绍过,在边缘对齐采样的情况下,容易出现保持时间余量不足的情况,这是由于在发射时钟的下一个时钟作为采样时钟去采数据时,由于间隔了一个时钟周期,容易导致采样时钟的时间相对于数据结束的时间更靠后,导致采样时钟无法对数据进行采样,可以采用PLL对齐进行时序约束,利用PLL对时钟进行左移,可以使时钟提前,进而可以增加保持时间余量。

时序图

如果利用PLL将时间向右移,会出现什么结果呢?以具体实验验证一下。

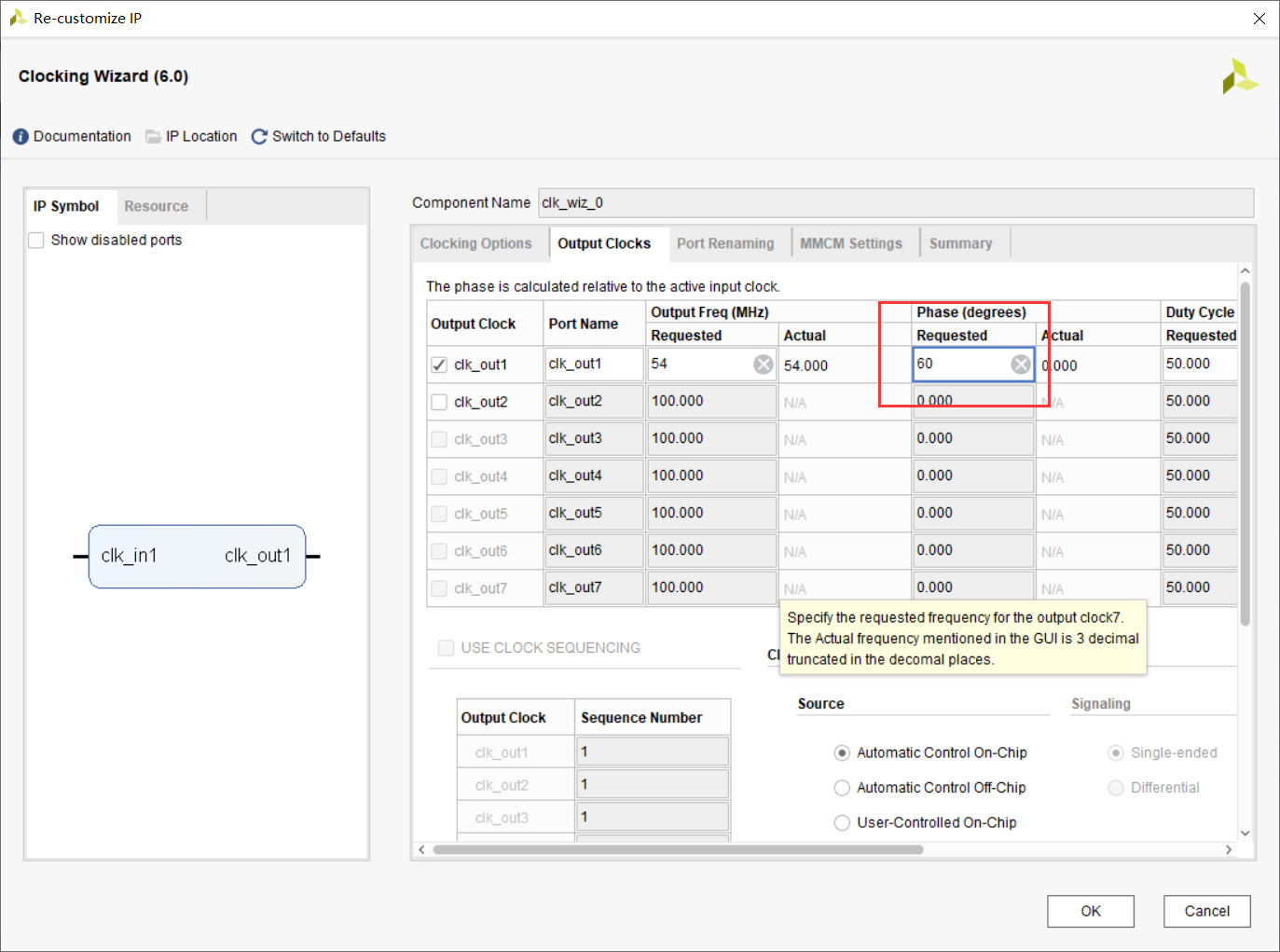

更改PLL参数

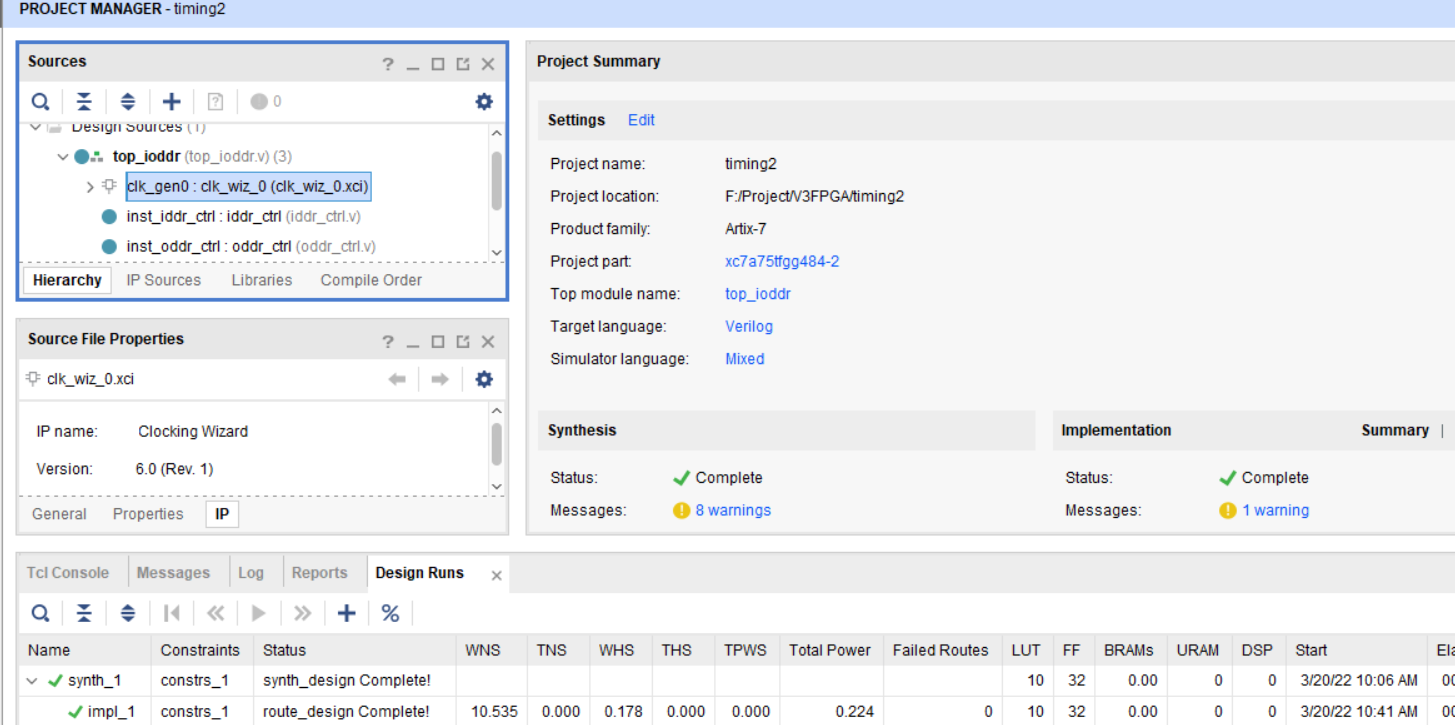

还是之前的实验工程,只需要将PLL IP核更改一下参数即可。

将相位偏移更改为60,其余参数不变。

综合布线

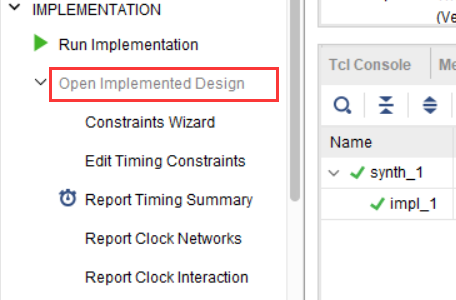

综合布线完成后打开布线设计

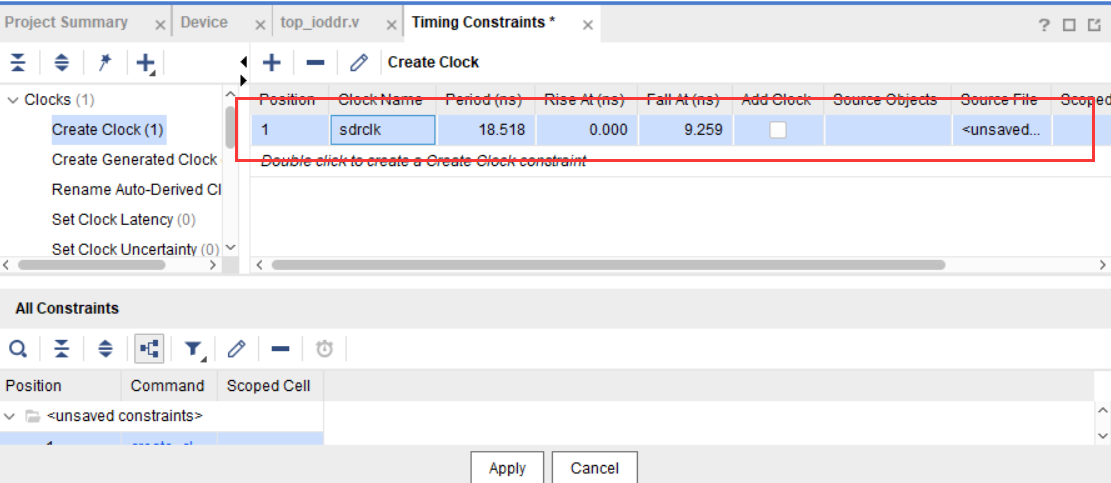

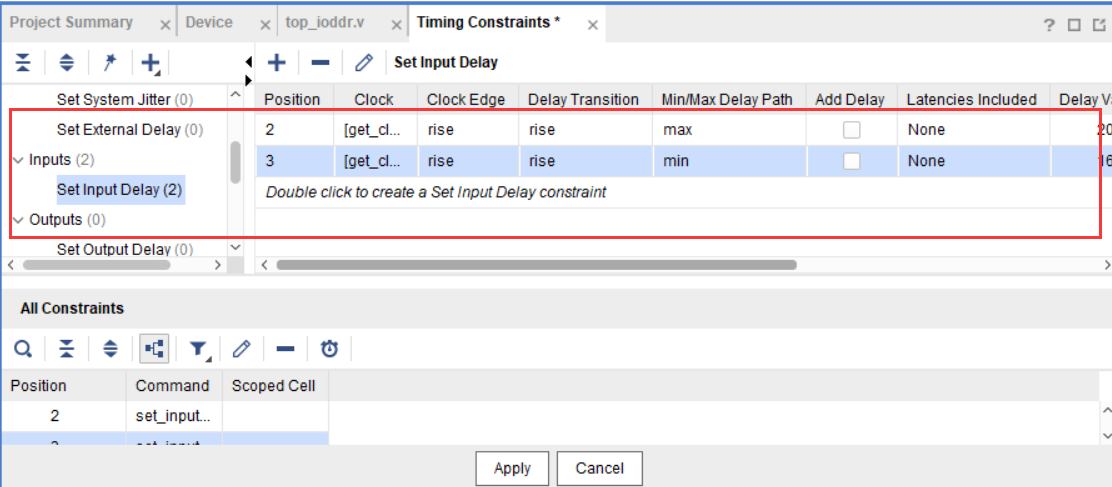

report timing

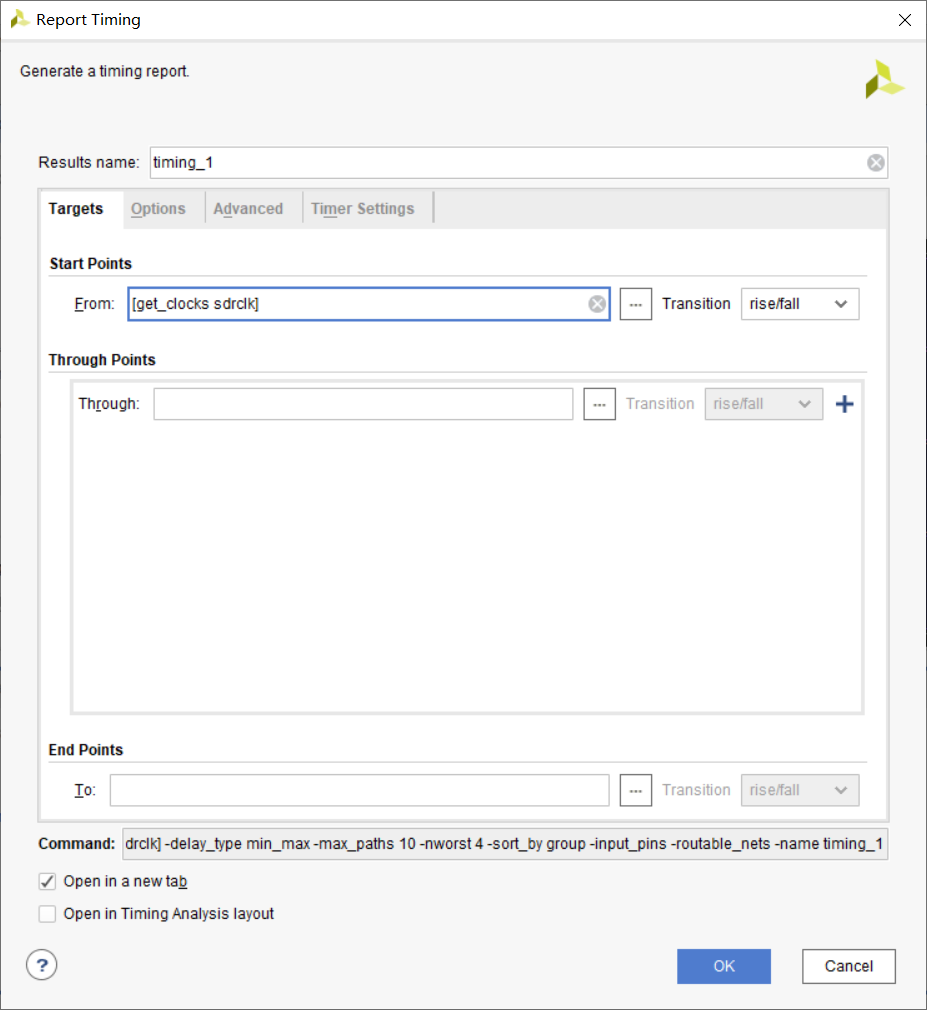

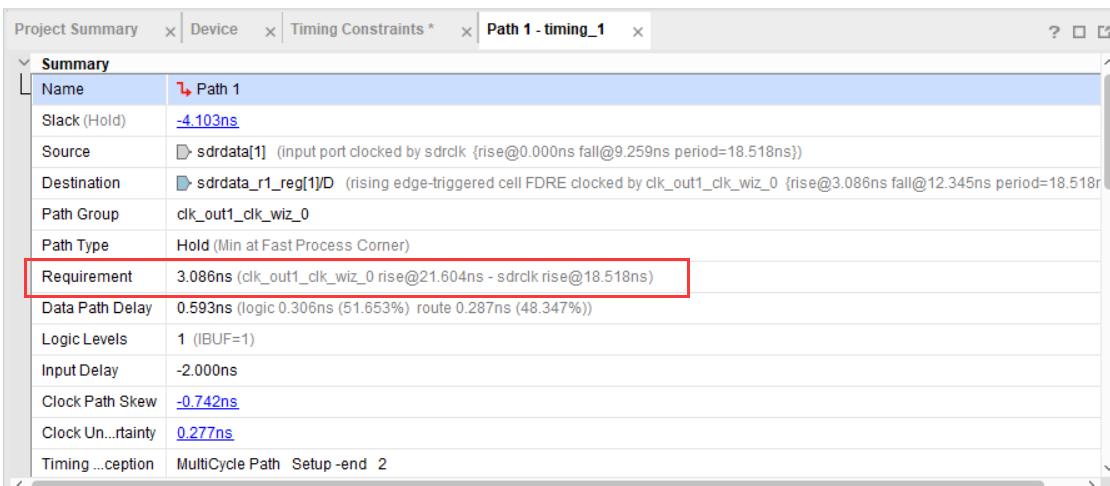

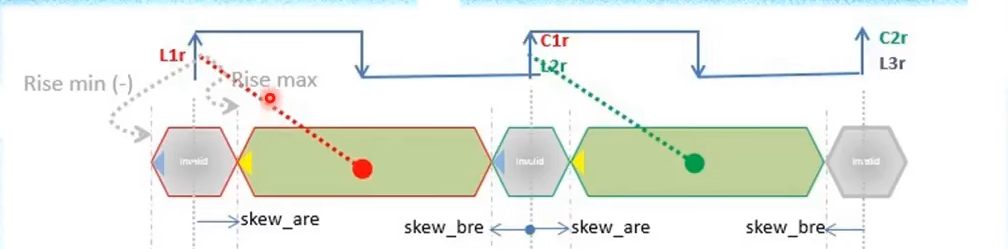

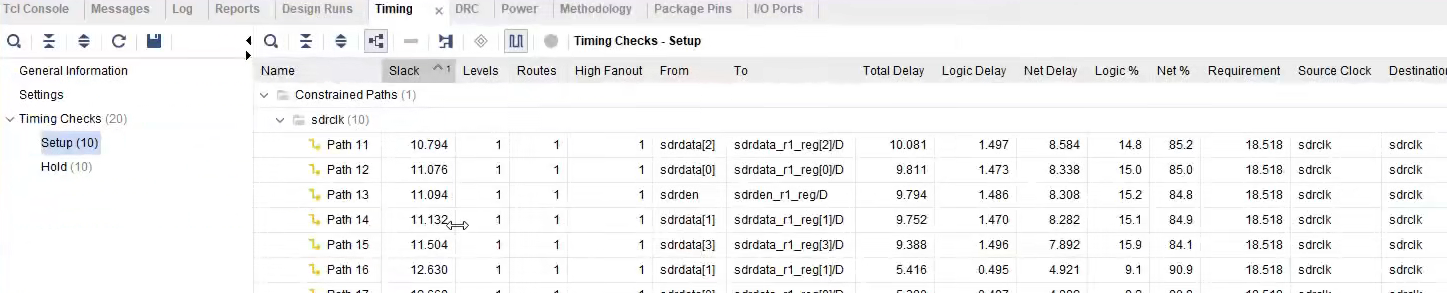

如下图设置

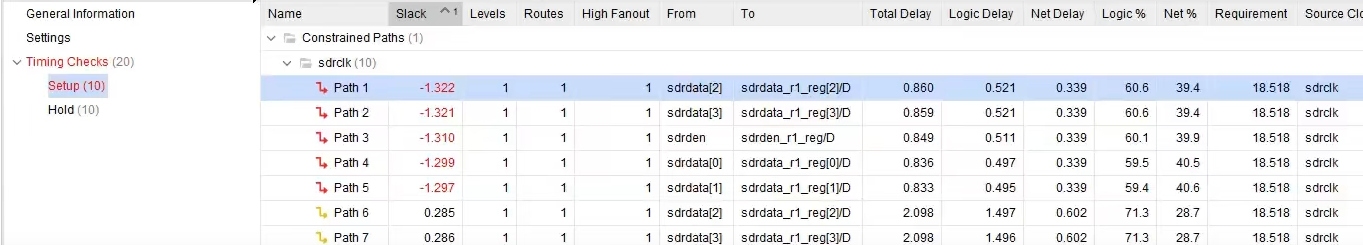

这时候可以看到建立时间出现了违例

路径分析

点击其中一条路径进行分析

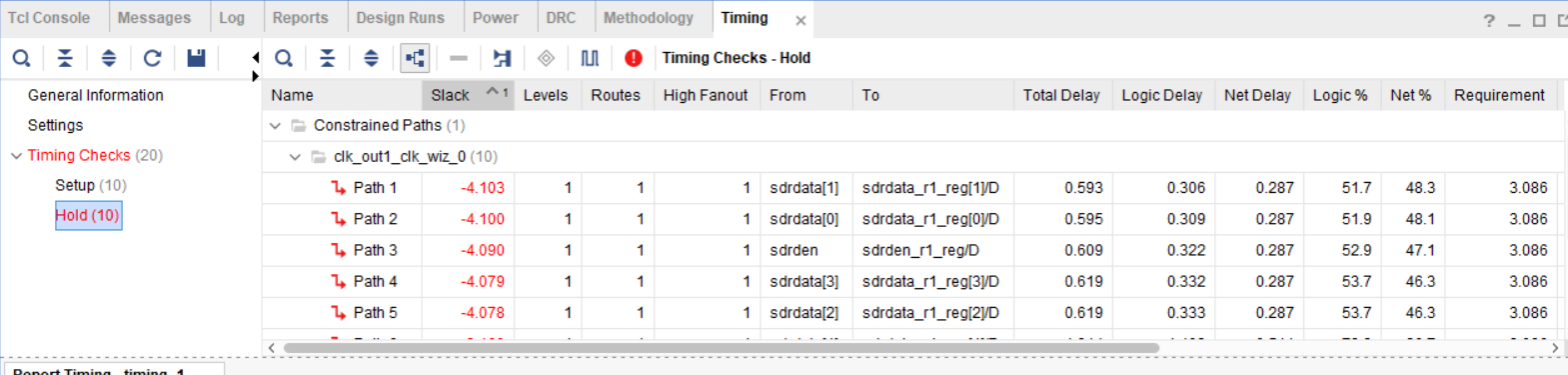

从这条路径的时序报告可以看到requirement这一栏中,表示的含义是:发送时钟再ons时刻,而采样时钟再3.086ns时刻,这明显是个错误的分析啊!一个时钟周期是18ns左右,享有偏移了一部分,采样时钟应该在20ns左右才对,这里应该是时序分析工具误以为采样时钟是刚刚偏移后的发送时钟,这应该怎么处理呢?

两种约束模型

第一种模型

这种时序模型可以用到input带有PLL的情况核不带有PLL的情况,带有PLL情况下采样时钟相移为正时需要进行“multicycle约束“,否则分析报告不正确。也就是说,在将时钟向右相移时,我们需要告诉时序分析工具我们所希望的采样时钟是哪个。

实际操作

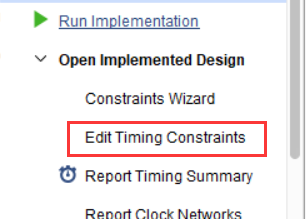

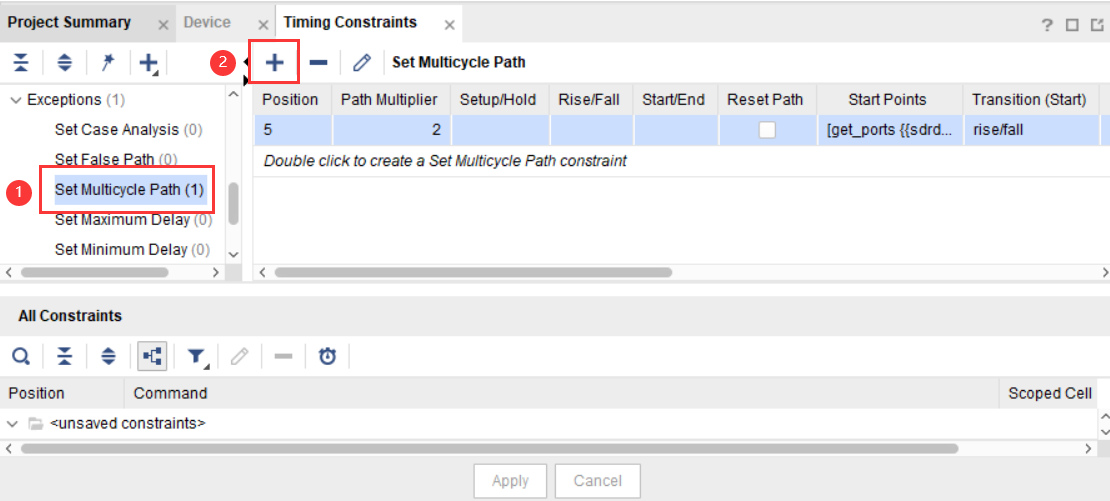

点击编辑时序约束

点击设置multicycle path

添加约束

将specify path multiplier设置为2,2表示我们需要将第二个上升沿作为采样时钟。

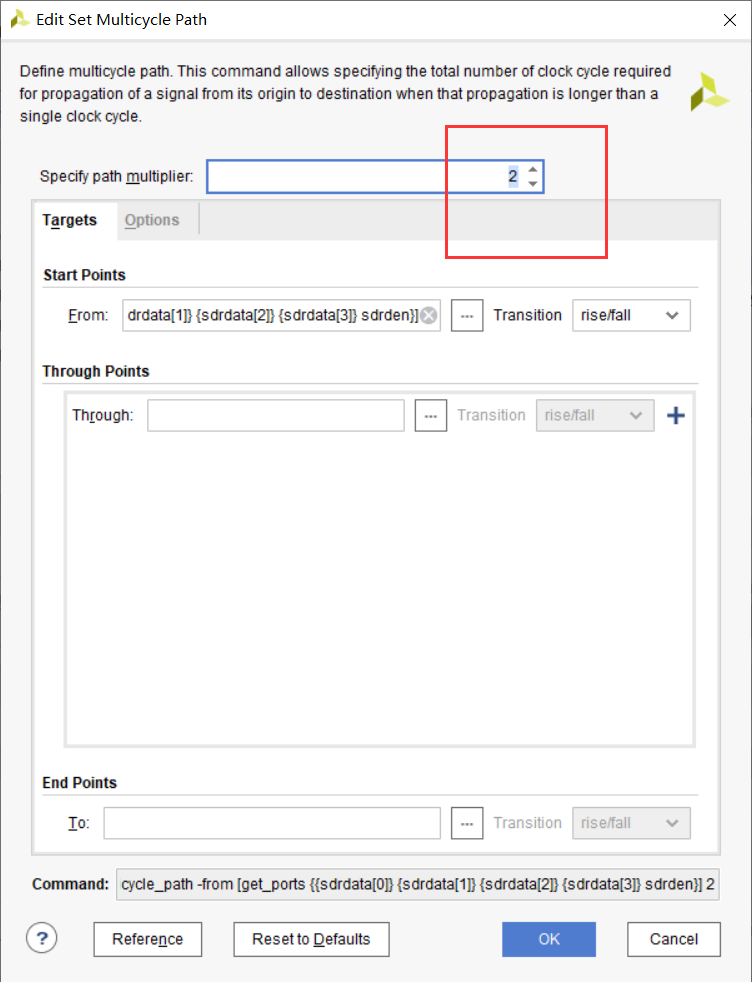

路径分析

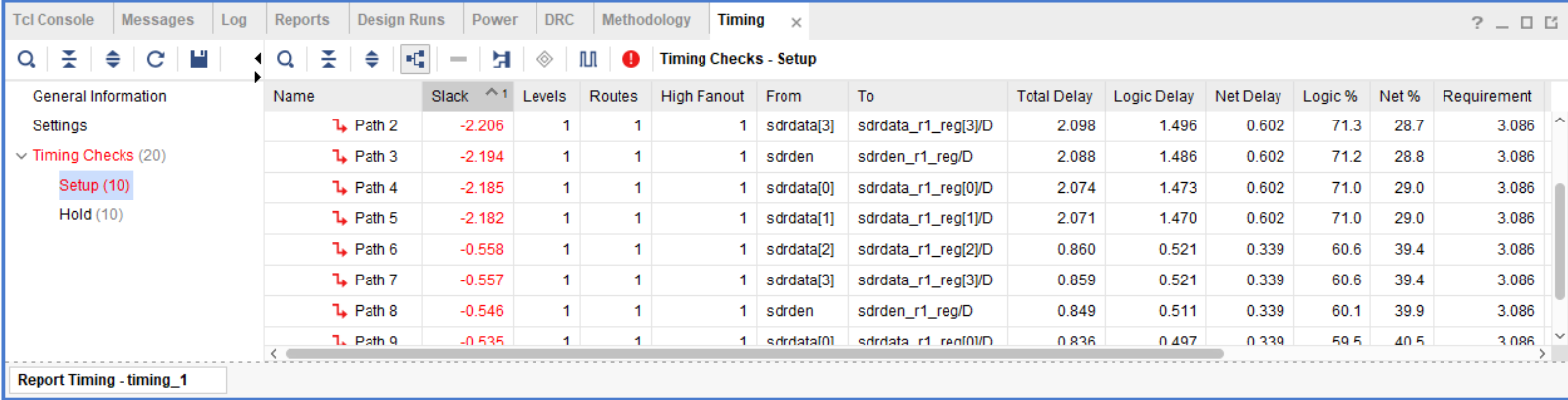

点击ok并reload,即可看到新的时序报告,可以看到这时候建立时间恢复了正常,但是保持时间出现了违例,可以点开其中一条路径进行分析。

依然看requirement这一栏的数据,表示采样时钟原来是18.518ns,现在变成了21.604ns,这与我们对时钟向右相移的操作得到的结果一致。虽然保持时间出现了违例,但是得到了正确的时序报告。因此在采样时钟相移为正的时候需要进行multicycle约束。

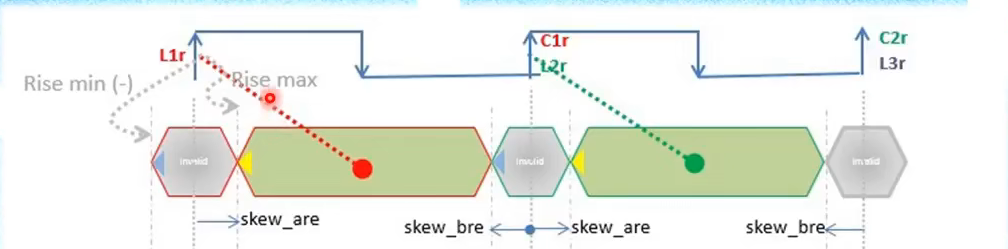

第二种模型

此类模型是上一个时钟作为发送时钟,下一个时钟作为采样时钟,相对于之前的模型来讲,相当于时钟提前了近一个时钟,这种时序模型可以用到input不带有PLL的情况,促使布线工具尽量增加时钟布线延迟使得建立时间满足要求,而上一个模型是为了让时钟布线更短一些。

以实际工程对两种模型进行仿真(不带PLL)

实验工程还是根据上一个进行更改,只需要在顶层中对PLL的例化代码进行注释即可。

顶层代码

module top_ioddr(

input wire rx_clk,

input wire rx_ctrl,

input wire [3:0] rx_dat,

//tx

output wire tx_clk,

output wire [3:0] tx_d,

output wire tx_dv,

input wire sdrclk,

input wire [3:0] sdrdata,

input wire sdrden,

output reg tout

);

wire rst;

wire rx_clk_90;

wire rx_en;

wire [7:0] rx_data;

reg tx_en1,tx_en2;

reg [7:0] tx_data1,tx_data2;

assign rst =0;

assign rx_clk_90 = rx_clk;

always @(posedge rx_clk_90 or posedge rst) begin

if (rst == 1'b1) begin

tx_data1 <= 'd0;

end

else if (rx_en == 1'b1) begin

tx_data1 <= rx_data+ rx_data -1;

end

end

always @(posedge rx_clk_90 or posedge rst) begin

if (rst == 1'b1) begin

tx_data2 <= 'd0;

end

else if (tx_en1 == 1'b1) begin

tx_data2 <= tx_data1+ tx_data1 -5;

end

end

always @(posedge rx_clk_90 ) begin

tx_en1 <= rx_en;

end

always @(posedge rx_clk_90 ) begin

tx_en2 <= tx_en1;

end

iddr_ctrl inst_iddr_ctrl

(

.rx_clk_90 (rx_clk_90),

.rst (rst),

.rx_dat (rx_dat),

.rx_ctrl (rx_ctrl),

.rx_en (rx_en),

.rx_data (rx_data)

);

oddr_ctrl inst_oddr_ctrl

(

.sclk (rx_clk_90),

.tx_dat (tx_data2),

.tx_en (tx_en2),

.tx_c (rx_clk_90),

.tx_data (tx_d),

.tx_dv (tx_dv),

.tx_clk (tx_clk)

);

reg [3:0] sdrdata_r1,sdrdata_r2;

reg sdrden_r1,sdrden_r2;

always @(posedge sdrclk) begin

{sdrdata_r2,sdrdata_r1} <= {sdrdata_r1,sdrdata};

end

always @(posedge sdrclk) begin

{sdrden_r2,sdrden_r1} <= {sdrden_r1,sdrden};

end

always @(posedge sdrclk) begin

if(sdrden_r2 == 1'b1) begin

tout <= (&sdrdata_r1)|(&sdrdata_r2);

end

else begin

tout <= (^sdrdata_r2);

end

end

endmodule重新对工程进行综合布线

打开布线设置

添加时钟约束

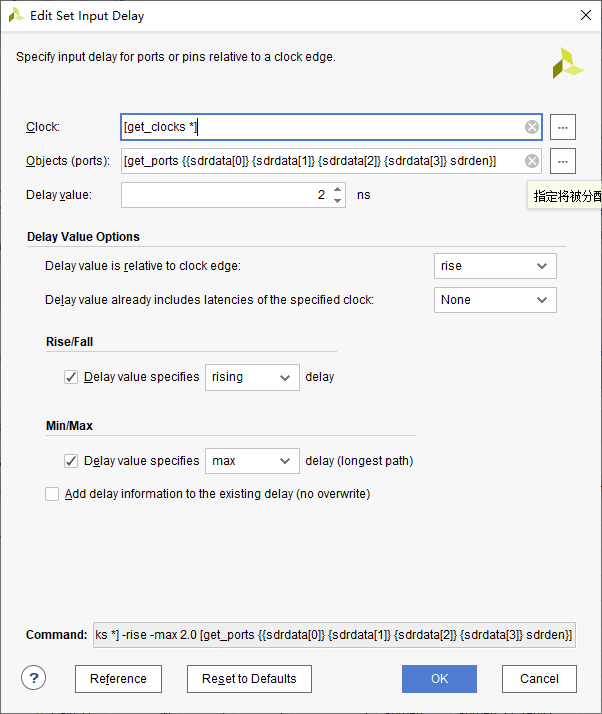

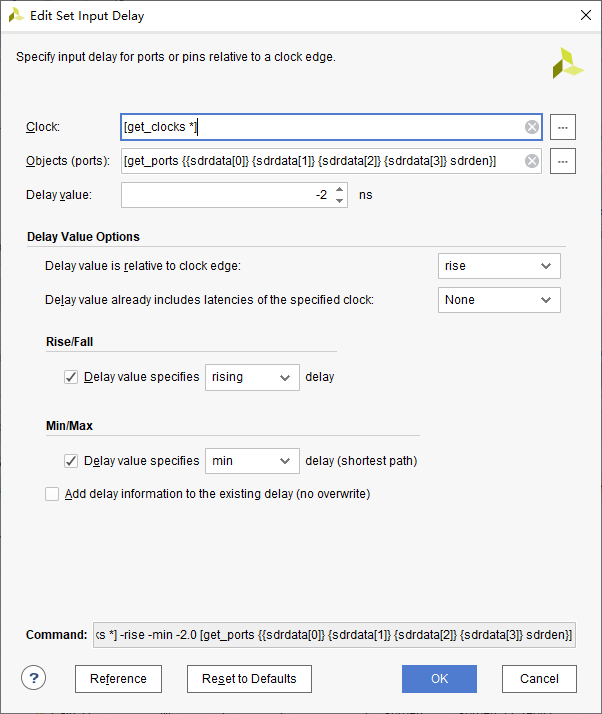

设置input delay

分别为最大20.518ns,最小16.518ns,设置方法和之前的教程基本一致。

此时时序出现违例

建立时间出现违例,说明在下一个时钟相对于数据开始的时间太靠前,导致建立时间出现违例,在这种模型下,本希望时序约束工具能够将时钟布线更长一些,就可以使建立时间余量更大一些,但是做不到,因此可以添加另一种约束条件,让时序恢复正常。

解决办法

将时序约束成下图的模型

input delay约束

最大为2ns,最小为-2ns,就相当于以当前的时钟作为发射时钟,下一个时钟作为采样时钟。

综合布线

结果

并report timing,就可以发现时序已经恢复了正常

总结

在有PLL进行约束的时候,两种模型都可以使用,但是要注意,在进行时钟右移的情况,需要额外添加一个”multicycle“的约束,为了省掉这部分的操作,一般是采用左移时钟的约束方法。

在没有PLL进行约束的情况下,就需要考虑,如果我们需要让数据路径布线更长一些(或者说是让时钟路径布线更短一些),就可以使用第一种模型进行约束;如果我们需要让时钟路径布线更长一些(或者说是让数据路径布线更短一些),就可以使用第二种模型进行约束。

往期系列博客

【Xilinx Vivado时序分析/约束系列1】FPGA开发时序分析/约束-寄存器间时序分析

【Xilinx Vivado时序分析/约束系列2】FPGA开发时序分析/约束-建立时间

【Xilinx Vivado时序分析/约束系列3】FPGA开发时序分析/约束-保持时间

【Xilinx Vivado时序分析/约束系列4】FPGA开发时序分析/约束-实验工程上手实操

【Xilinx Vivado时序分析/约束系列5】FPGA开发时序分析/约束-IO时序分析

【Xilinx Vivado时序分析/约束系列6】FPGA开发时序分析/约束-IO时序输入延时

【Xilinx Vivado时序分析/约束系列7】FPGA开发时序分析/约束-FPGA单沿采样数据input delay时序约束实操

【Xilinx Vivado时序分析/约束系列8】FPGA开发时序分析/约束-FPGA数据中间采样、边缘采样PLL时序优化实操

最后

以上就是细腻人生最近收集整理的关于【Xilinx Vivado时序分析/约束系列9】FPGA开发时序分析/约束-FPGA单沿数据input delay边沿对齐,不同时序模型实操练习边缘对齐采样两种约束模型总结往期系列博客的全部内容,更多相关【Xilinx内容请搜索靠谱客的其他文章。

发表评论 取消回复