一、CY7C68013简介

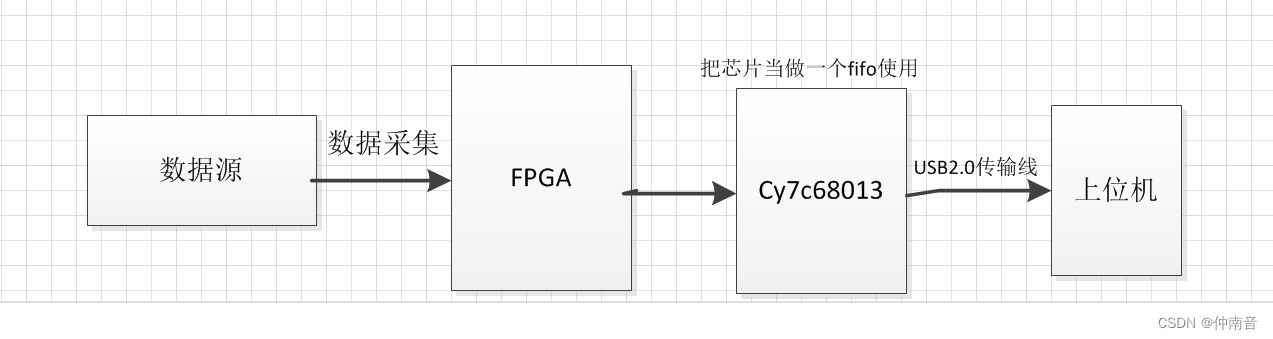

CY7C68013是Cypress公司的FX2系列芯片,是一款USB2.0芯片,最大传输速度60MByte/S ,半双工通信方式。

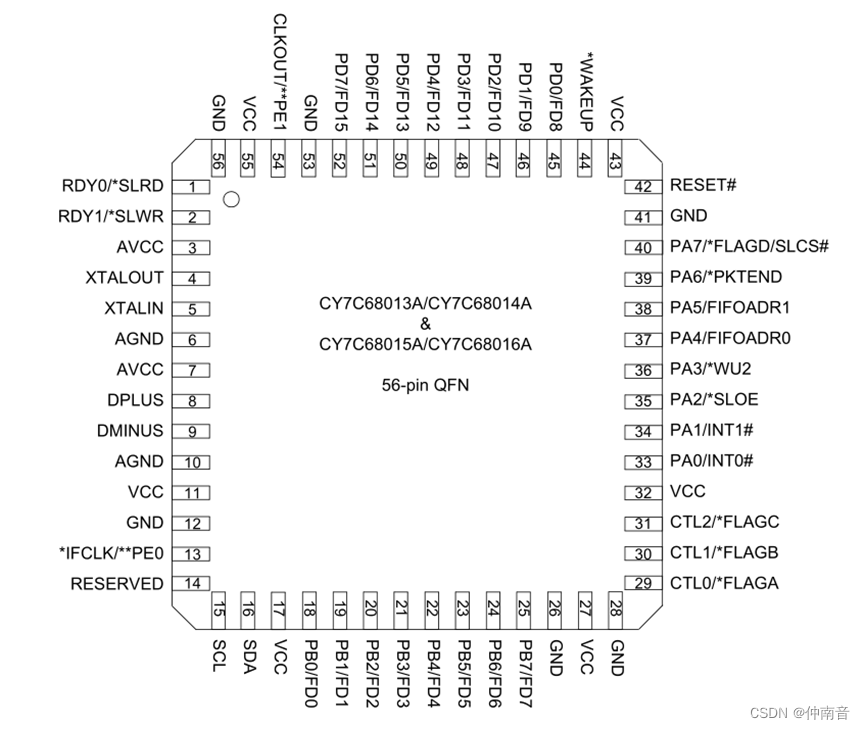

| 功能 | 引脚 | 说明 |

| FD0~FD7 | 18~25 | 数据线低字节 |

| FD8~FD15 | 45~52 | 数据线高字节 |

| FIFOADDR0 FIFOADDR1 | 37 38 | 地址线,接收:2'b00 发送:2'b10 |

| SLRD | 1 | 读控制信号,低电平有效 |

| SLWR | 2 | 写控制信号,低电平有效 |

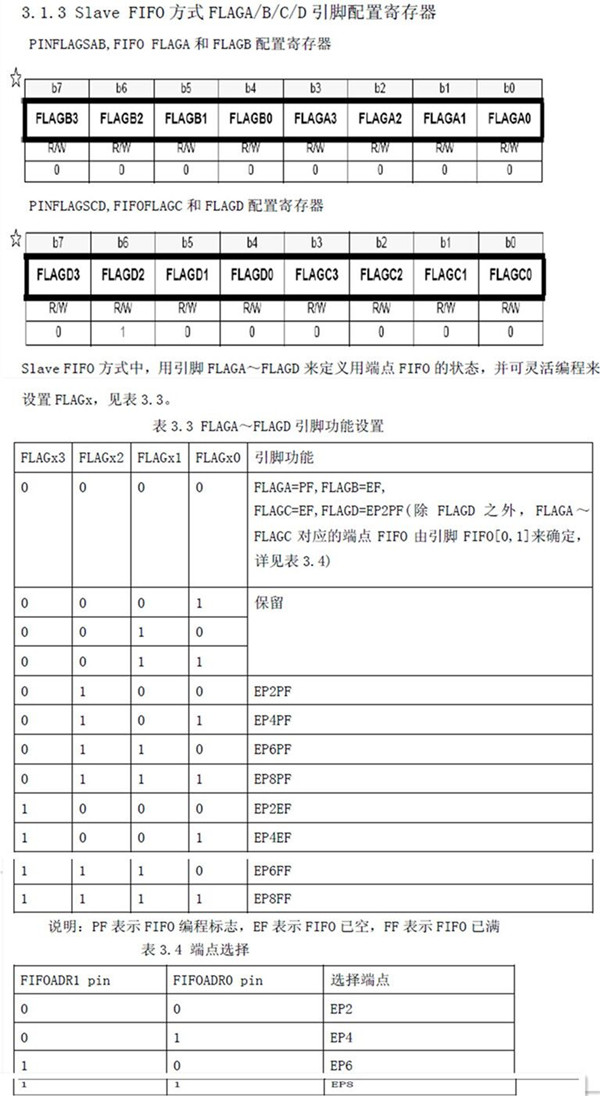

| FLAGA FLAGB FLAGC FLAGD | 31 30 29 40 | 可通过程序配置,映射到不同功能,一般用于指示fifo的空、满状态 |

| SLCS | 40 | 片选信号,拉低即可,与FLAGD复用,一般程序设计尽量避免FLAGD的使用 |

| PKTEND | 39 | 数据包结束标志信号 ,一般拉高即可 |

| SLOE | 35 | 输出使能,低电平有效(接收USB数据时使用) |

1.1 Cy7C68013的Slave FIFO模式

Cy7C68013内嵌一个8051处理器,将芯片Slave FIFO 相关的寄存器修改,控制芯片工作在Slave FIFO模式下。外部逻辑(如FPGA)即可按照SlaveFIFO的传输时序,高速与主机进行通讯,而在通讯过程中不需要8051固件的参与。

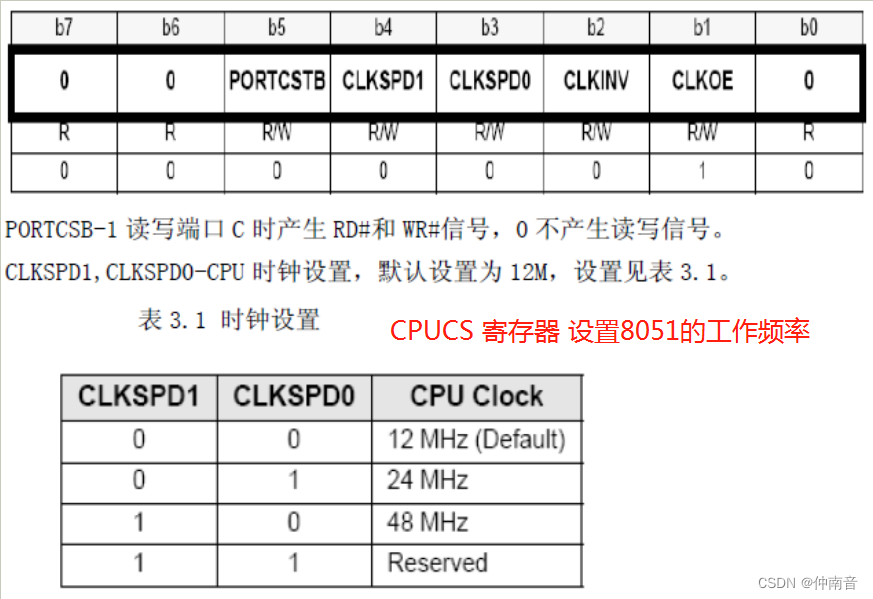

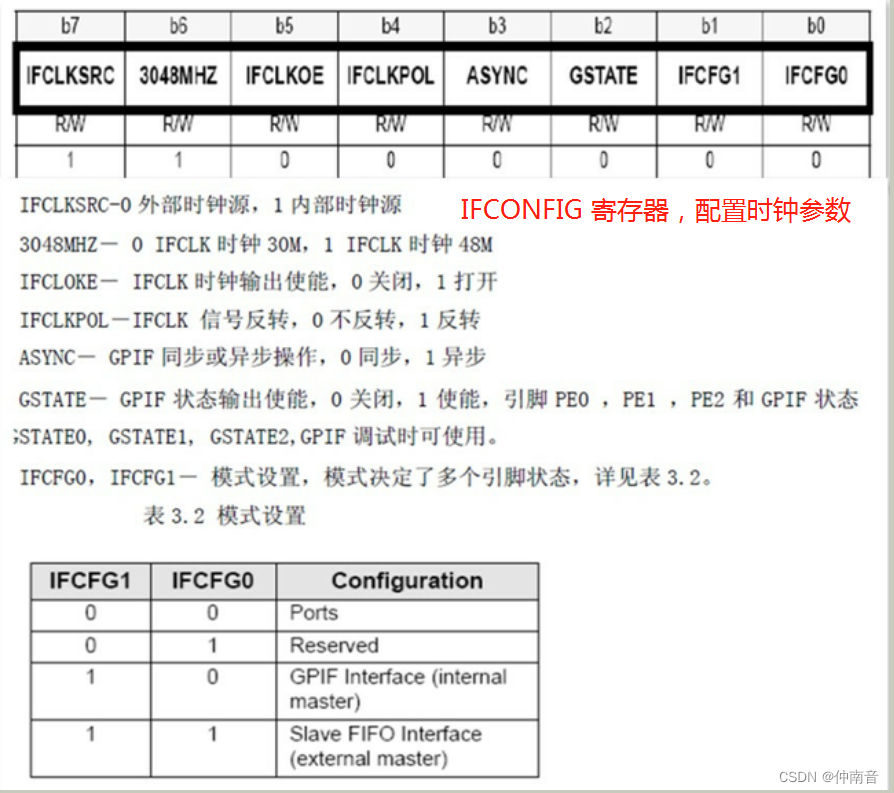

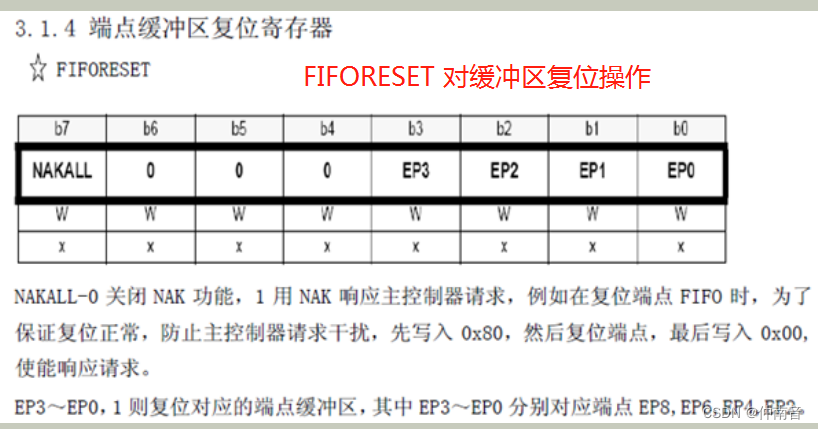

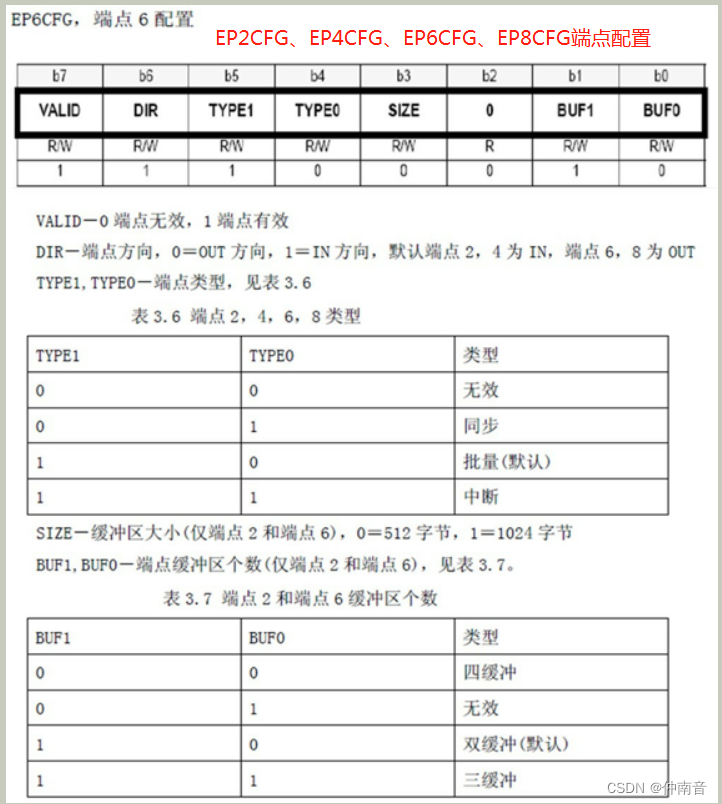

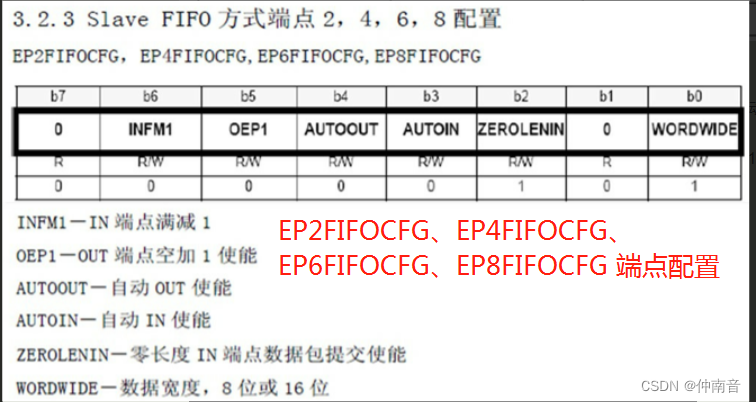

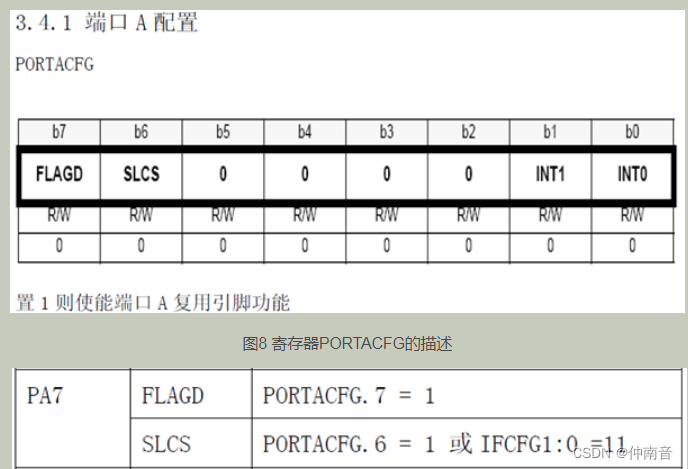

1.2、Slave FIFO模式相关寄存器

FLAGA、FLAGB、FLAGC、FLAGD功能配置

二、硬件设计

芯片高速模式下最大传输速度60MByte/S ,全速模式下最大传输速度12MByte/S方式。所以电路布局时要考虑一下因素对信号的影响

2.1、振荡器、晶振

在电路设计阶段踩过的坑,根据官方手册建议,振荡器要满足一下要求:

- 频率24MHZ

- 并联谐振电容

- 基本模式

- 驱动电平为500uw

- 12pf(容差5%)的负载电容

- 精度 +/-50PPM

- 晶振不宜与芯片距离较大,尽可能缩短晶振到芯片的走线

- 晶振走线原理 应D+ 和D-的走线

2.2、D+ 与D-信号

- 采用差分走线,两根线等长、等宽、间距相等,保持在同一层

- 根据电路板生产厂家,计算走线,控制90欧姆阻抗

- 在电路板上的走线不得过长不得超过75mm

- 尽量保证两根线周围的250mil空间没有铺铜、走线

- 避免使用过孔,如果 使用较小的过孔(25mil焊盘、10mil过孔)

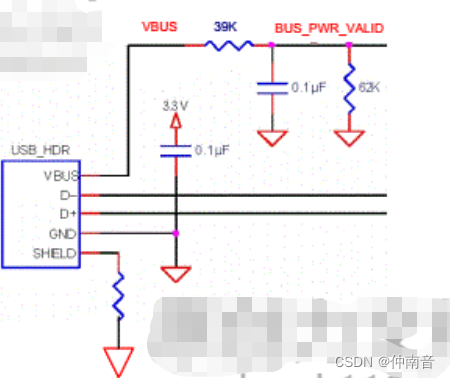

2.3、VBUS、GND、屏蔽信号

电源线尽量走粗

三、使用过程中记录

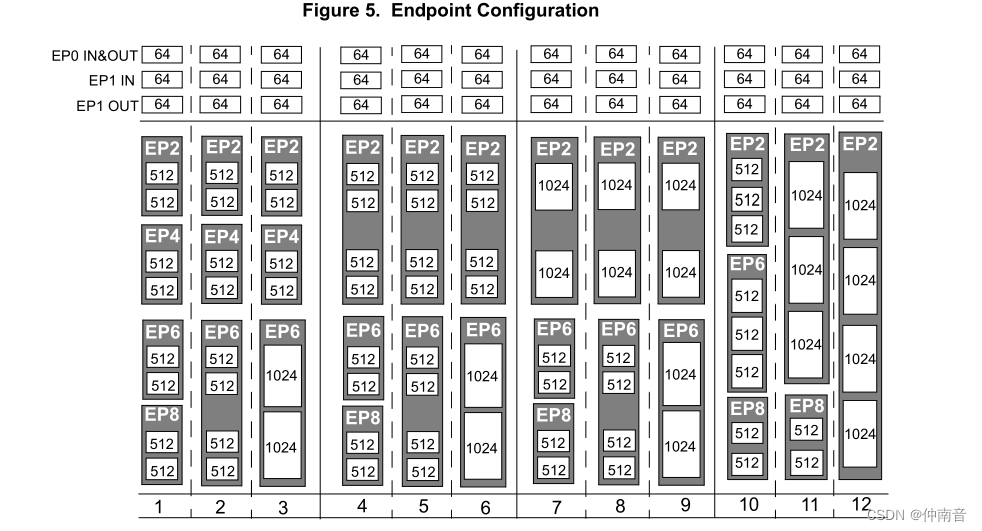

芯片的Slave FIFO模式,可将EP2、EP4、EP6、EP8配置成上图几种存储方式,在通信的数据格式上要考虑512字节的基础存储单位。

最后

以上就是想人陪河马最近收集整理的关于FPGA----CY7C68013使用记录一、CY7C68013简介二、硬件设计 三、使用过程中记录的全部内容,更多相关FPGA----CY7C68013使用记录一、CY7C68013简介二、硬件设计内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复