文章目录

- 第一章 微型计算机基础概论

- 第一讲 关于

- 第二讲 微型计算机系统组成

- 第三讲 微机工作过程

- 第四讲 常用数制

- 第五讲 编码

- 第六讲 数及其运算

- 第七讲 基本逻辑运算和逻辑门

- 第八讲 基本逻辑运算及其门电路

- 第二章 微处理器与总线

- 第九讲 8088/8086微处理器

- 第十讲 8088的主要引线及其内部结构

- 第十一讲 8088CPU内部寄存器

- 第十二讲 实模式下的存储器寻址

- 第十三讲 8088 系统总线

- 第三章 指令系统概述

- 第十四讲 8088/8086指令系统

- 第十五讲 指令的寻址方式

- 第十六讲 数据传送指令

- 第四章 算术运算,逻辑运算与移位操作指令

- 第十七讲 算术运算类指令

- 第十八讲 逻辑运算指令

- 第十九讲 移位操作指令

- 第五章 串操作指令

- 第二十讲 串操作指令

- 第二十一讲 串传送与串比较指令

- 第二十二讲 串扫描指令

- 第二十三讲 串装入与串存储指令

- 第六章 程序与处理器控制指令

- 第二十四讲 程序控制指令

- 第二十五讲 处理器控制指令

- 第七章 汇编语言

- 第二十六讲 汇编语言程序设计

- 第二十七讲 数据定义伪代码

- 第二十八讲 符号与段定义相关伪指令

- 第二十九讲 其他伪指令

- 第三十讲 系统功能调用

- 第八章 半导体存储器

- 第三十一讲 半导体存储器概述

- 第三十二讲 微机中的存储器

- 第三十三讲 存储单元的编址

- 第三十四讲 存储器扩展技术

- 第九章 输入输出与中断技术

- 第三十五讲 输入输出技术概述

- 第三十六讲 简单接口芯片

- 第三十七讲 基本输入输出方法

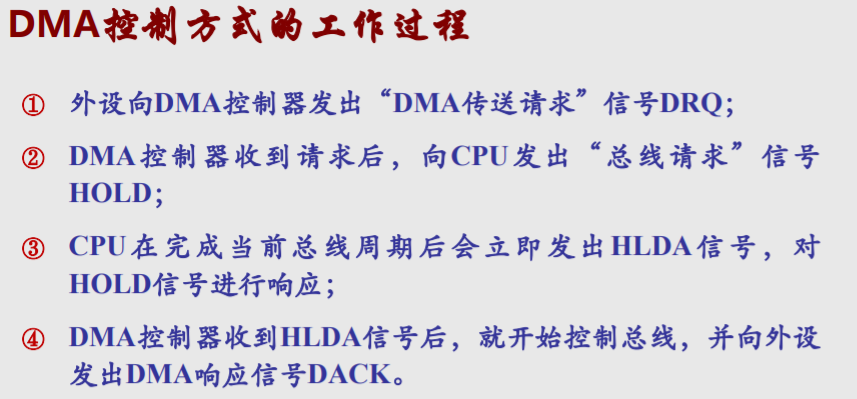

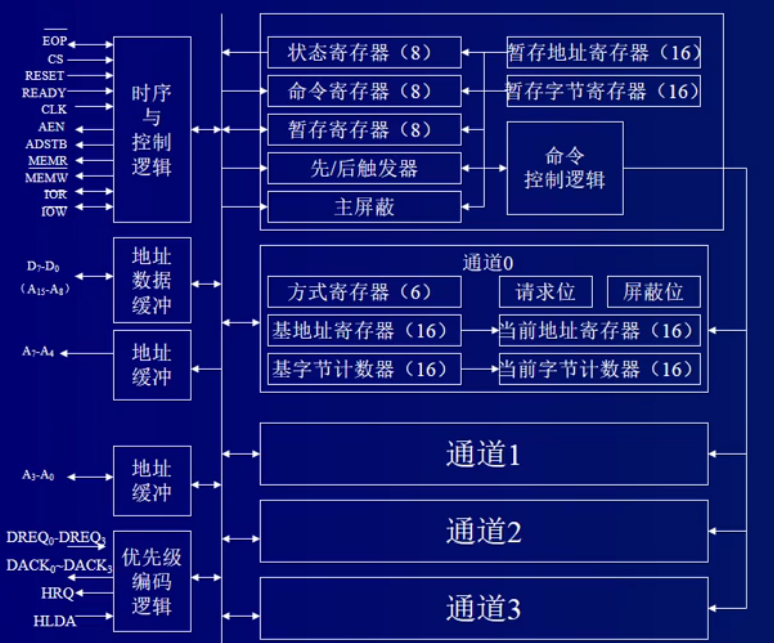

- DMA控制器8237A

- 第三十八讲 中断技术

- 第十章 可编程数字接口电路

- 可编程定时计数器8253

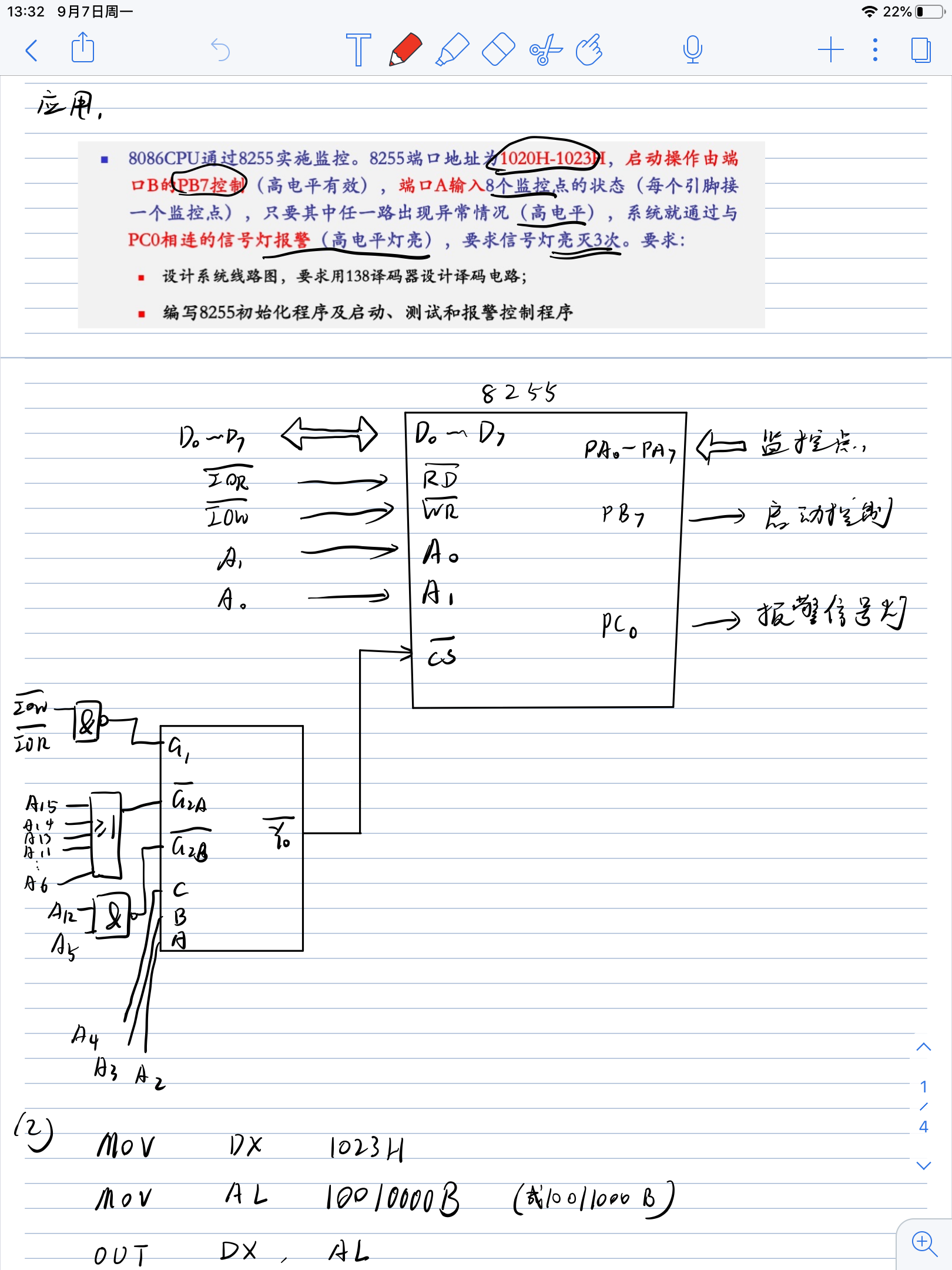

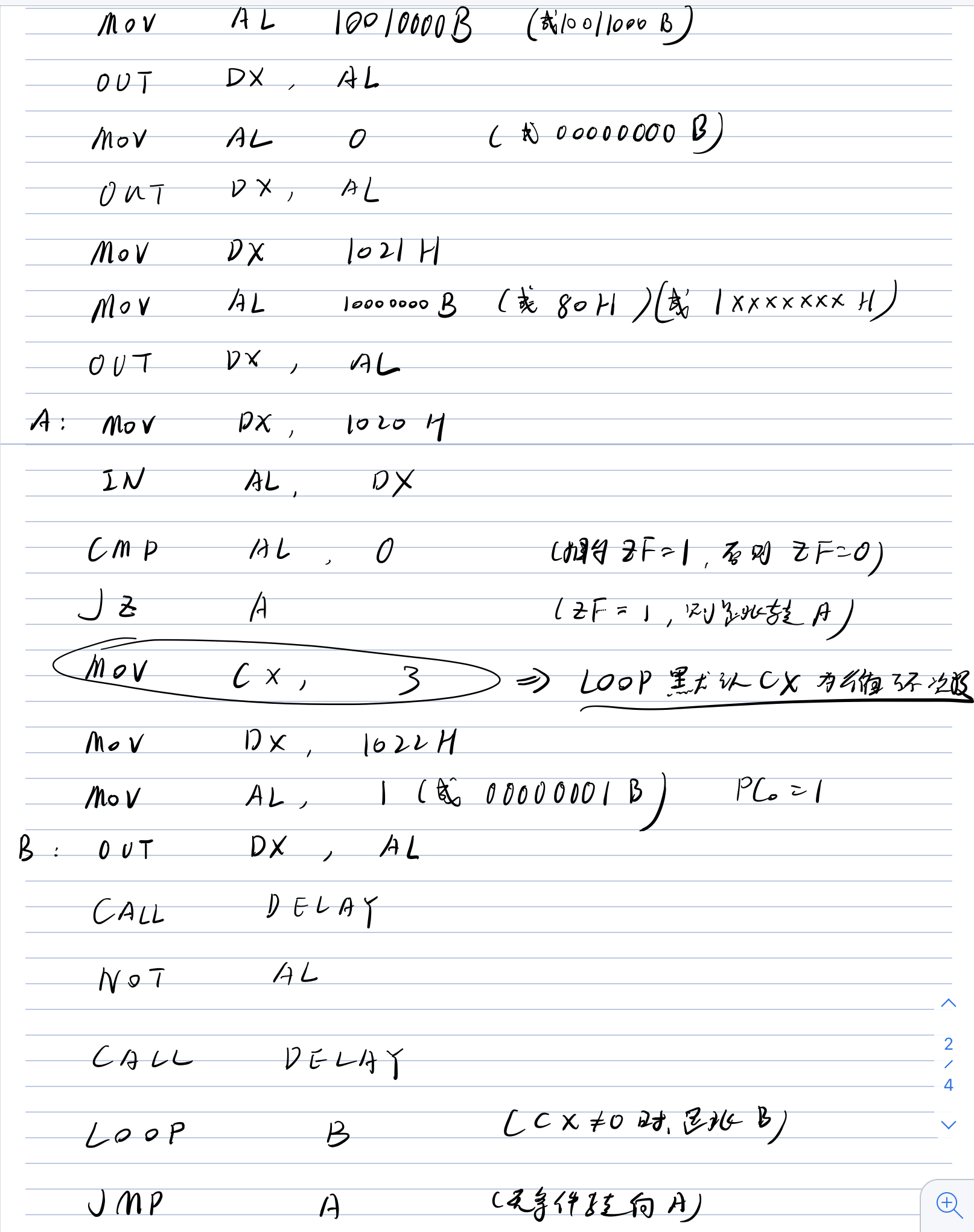

- 可编程并行接口8255

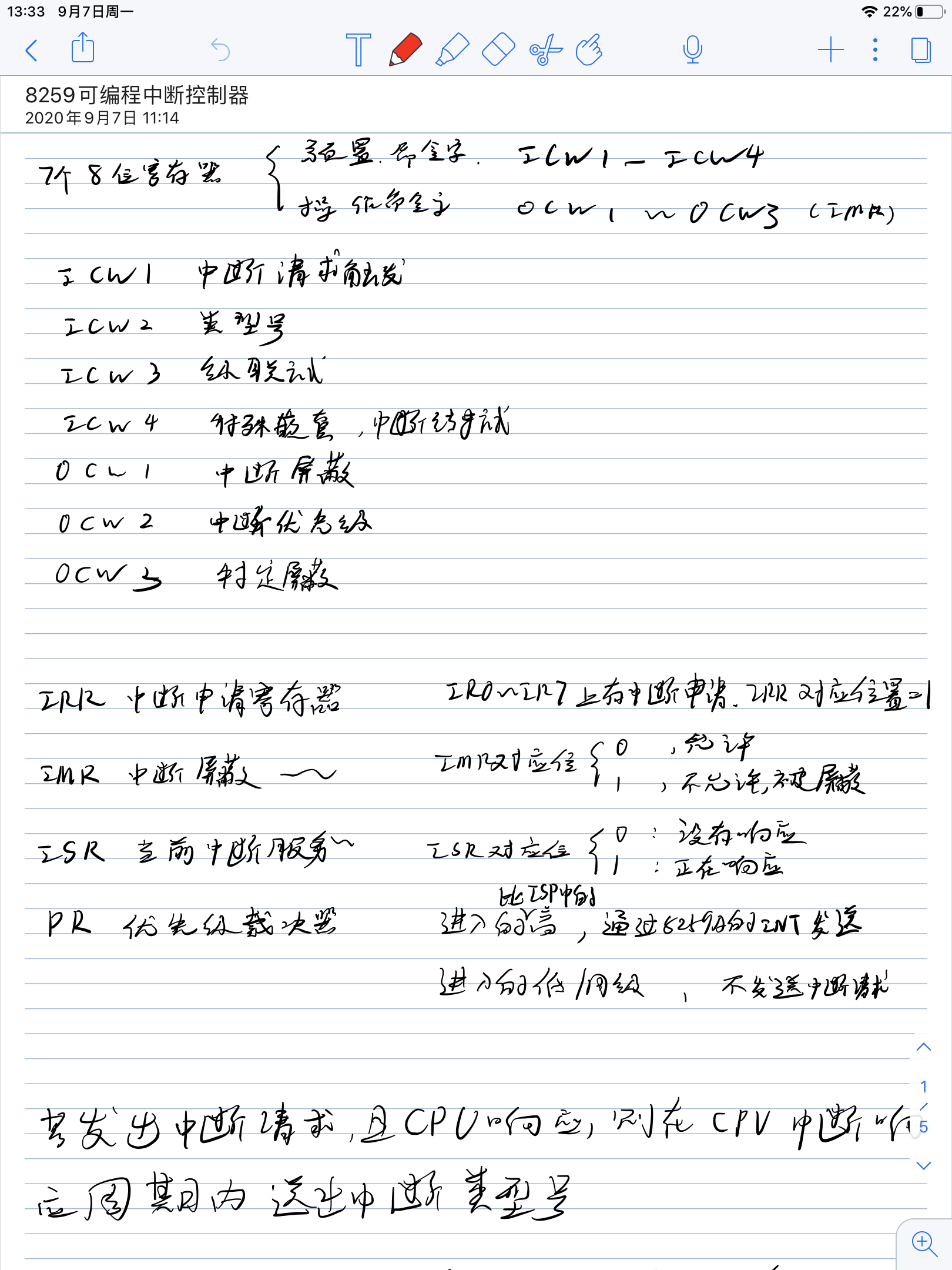

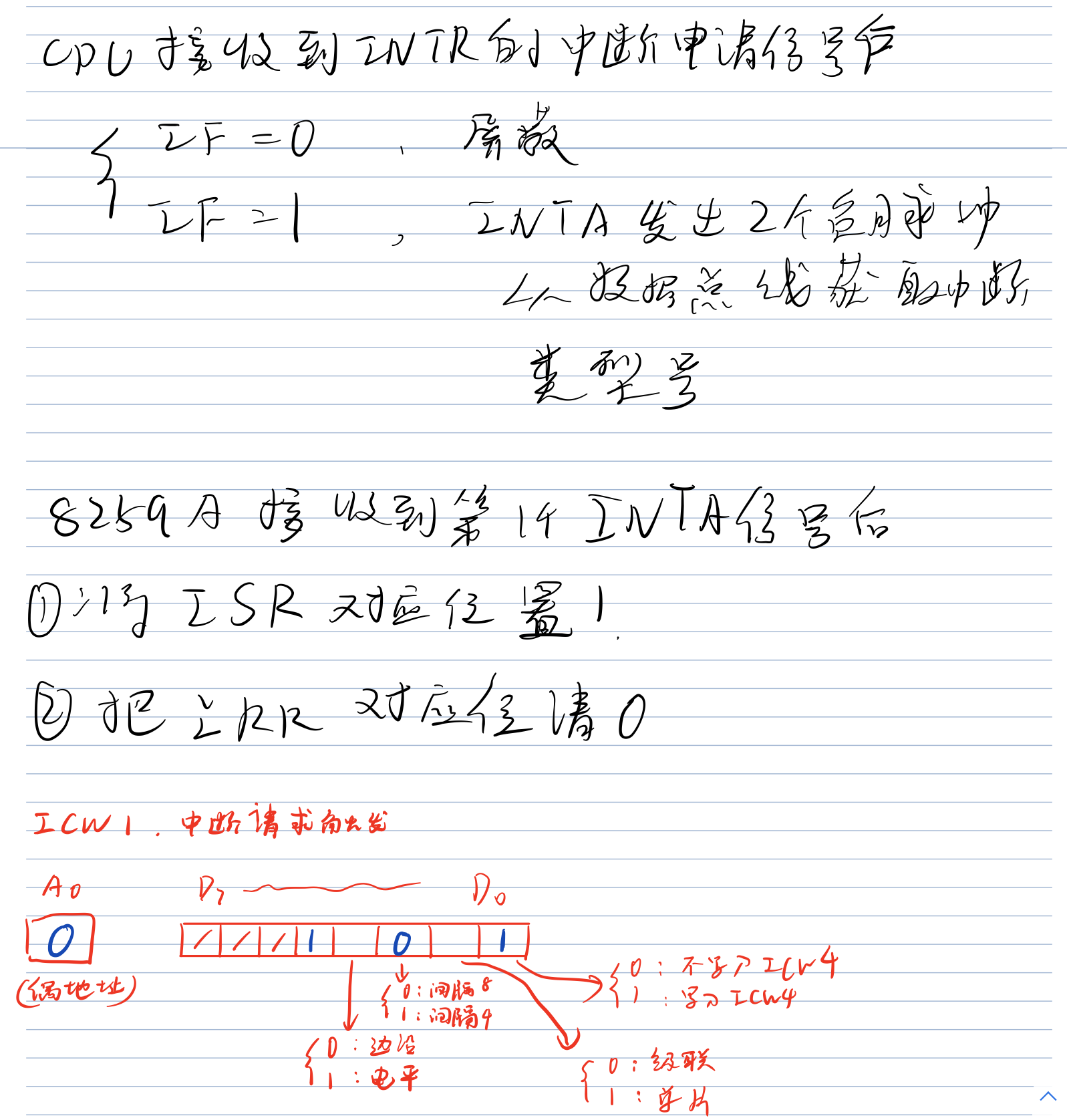

- 可编程中断控制器8259

- 第十一章 模拟接口电路

- 模拟量的输入输出

- D/A转换器和A/D转换器

- D/A转换器(DAC0832)NS

- A/D转换器(ADC0809)

- 补充

大学课程《微机原理与接口技术》学习笔记整理

我的博客原文链接

大学课程《微机原理与接口技术》学习笔记整理

第一章 微型计算机基础概论

第一讲 关于

- 计算机的主要应用:数值计算,信息处理,过程控制

- 微机原理与接口技术包括:数值信息表示,微型机基本原理,汇编程序设计,半导体存储器及其接口设计,输入输出技术

第二讲 微型计算机系统组成

- 计算机系统:

- 硬件系统

- 主机系统:CPU,存储器,输入输出接口,总线

- 外部设备

- 软件系统

- 硬件系统

- 能够与CPU直接进行信息交换的部件属于主机系统,不能够与CPU直接进行信息交换的部件属于外部设备

- CPU

- 微处理器简称CPU,是计算机的核心

- 主要包括:运算器,控制器,寄存器组

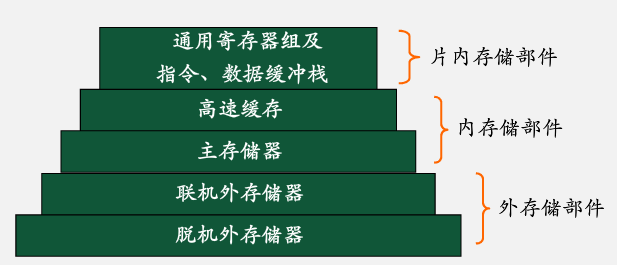

- 存储器:

- 计算机中的记忆装置。用于存放计算机工作过程中需要操作的数据和程序

- 内存储器 :

- 存取速度较快,容量相对较小

- 内存按单元组织,每单元都对应一个惟一的地址

- 每个内存单元中存放1Byte数据【每8位0或1称 为1字节(Byte)】

- 内存单元个数称为内存容量

- 按工作方式分类:随机存取存储器(RAM),只读存储器(ROM)

- 外存储器

- 联机外存:硬磁盘

- 脱机外存:各种移动存储设备

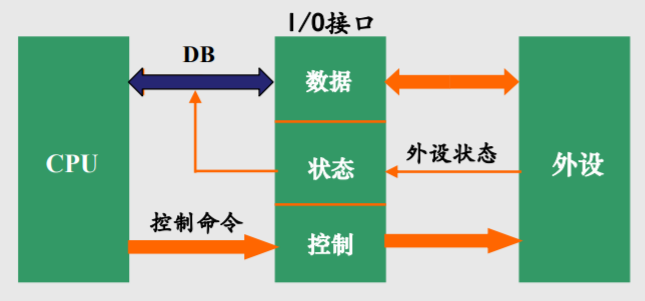

- 输入/输出接口

- 接口是CPU与外部设备间的桥梁

- 主要功能:

- 数据缓冲寄存;

- 信号电平或类型的转换;

- 实现主机与外设间的运行匹配。

- 总线

- 是一组导线和相关的控制、驱动电路的集合。

- 是计算机系统各部件之间传输地址、数据和控制信息的通道

- 地址总线(AB) 数据总线(DB) 控制总线(CB)

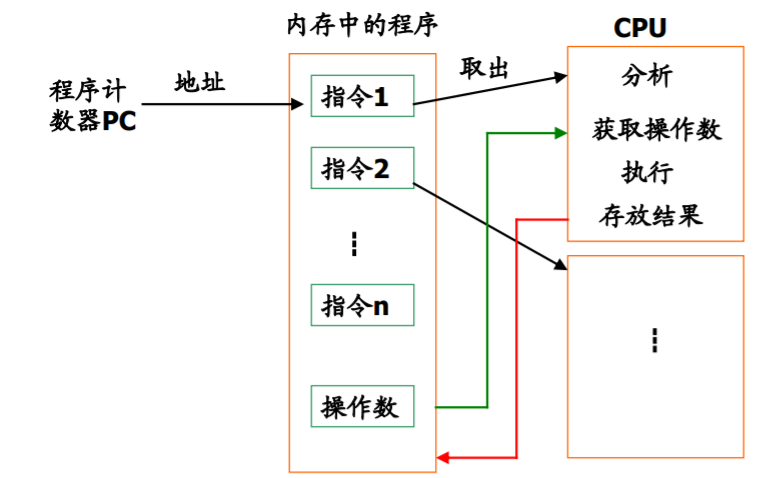

第三讲 微机工作过程

- 计算机的工作就是按照一定的顺序,一条条地执行指令

- 指令: 由人向计算机发出的、能够为计算机所识别的命令

- 过程:取指令->分析指令->读取操作数->执行指令->存放结果

- 顺序执行: 一条指令执行完了再执行下一条指令。

- 执行时间=取指令+分析指令+执行指令

- 设:三个部分的执行时间均为Δt,则:执行n条指令时间T0为:

- T0=3nΔt

- 并行执行: 同时执行两条或多条指令。

- 仅第1条指令需要3 Δt时间,之后每经过1 Δt,就有一条指令执行结束

- 执行时间: T =3Δt +( n-1)Δt

- 并行: 更高的效率,更高的复杂度

- 相对于顺序执行方式,指令并行执行的优势用加速比S表示:

- S=顺序执行花费的时间/并行执行花费的时间

- 例: 3n Δt /(3Δt +( n-1)Δt) =3n/(2+n)

- 冯 • 诺依曼计算机的工作原理: 存储程序工作原理,结构特点:运算器为核心

- 冯 • 诺依曼机的工作过程

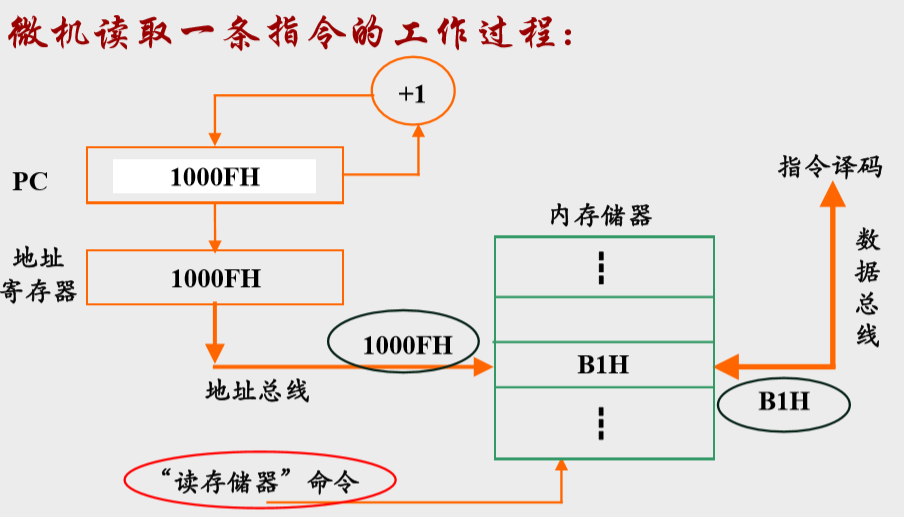

- 取一条指令的工作过程:

- ① 将指令所在地址赋给程序计数器PC;

- ② PC内容送到地址寄存器AR,PC自动加1;

- ③ 把AR的内容通过地址总线送至内存储器,经地址译码器译码,选中相应单元。

- ④ CPU的控制器发出读命令。

- ⑤ 在读命令控制下,把所选中单元的内容(即指令操作码)读到数据总线 DB。

- ⑥ 把读出的内容经数据总线送到数据寄存器DR。

- ⑦ 指令译码:数据寄存器DR将它送到指令寄存器IR,然后再送到指令译码器ID

- 特点:

- 程序存储,共享数据,顺序执行

- 属于顺序处理机,适合于确定的算法和数值数据的处理。

- 不足:

- 与存储器间有大量数据交互,对总线要求很高;

- 执行顺序由程序决定,对大型复杂任务较困难;

- 以运算器为核心,处理效率较低;

- 由PC控制执行顺序,难以进行真正的并行处理。

- 取一条指令的工作过程:

- 哈佛结构

- 指令和数据分别存放在两个独立的存储器模块中;

- CPU与存储器间指令和数据的传送分别采用两组独立的总线;

- 可以在一个机器周期内同时获得指令操作码和操作数。

第四讲 常用数制

- 计算机中的常用计数制:十进制 ,二进制数 ,十六进制数 ,八进制数

第五讲 编码

- 编码:

- 信息从一种形式或格式转换为另一种形式的过程

- 用代码来表示各种信息,以便于计算机处理。

- 需要编码的信息种类:数值,字符,声音,图形,图像

- 所有需要由计算机处理的信息,都需要编码,使所有信息都以二进制码形式表示

- 计算机中的编码

- 数值编码:

- 二进制码

- BCD码

- 西文字符编码

- ASCII码

- 数值编码:

- BCD(Binary Coded Decimal)码

- 用二进制表示的十进制数

- 特点:

- 保留十进制的权,数字用0和1表示。

- 8421BCD编码:

- 用4位二进制码表示1位十进制数,每4位之间有一个空格

- 1010—1111是非法BCD码

- (0001 0001 .0010 0101)BCD =11 .25 =(1011 .01)B

- BCD码在计算机中的存储方式

- 以压缩BCD码形式存放:

- 用4位二进制码表示1位BCD码

- 一个存储单元中存放2位BCD数

- 以扩展BCD码形式存放

- 用8位二进制码表示1位BCD码.即高4位为0,低4位为有效位

- 每个存储单元存放1位BCD

- 以压缩BCD码形式存放:

- ASCII码

- 西文字符编码:将每个字母、数字、标点、控制符用1Byte二进制码表示

- 标准ASCII的有效位:7bit,最高位默认为0

- ASCII码的奇偶校验

- 奇校验:加上校验位后编码中“1”的个数为奇数。

- 偶校验:加上校验位后编码中“1”的个数为偶数。

第六讲 数及其运算

- 定点数

- 浮点数

- 小数点的位置可以左右移动的数

- 规格化浮点数:尾数部分用纯小数表示,即小数点右边第1位不为0

- 无符号数

- 有符号数:用最高位表示符号,其余是数值,0正,1负

- 原码:最高位为符号位,其余为真值部分

- [X]原=符号位+|绝对值|

- 有[+0]和[-0]之分

- 反码:

- 若X>0 ,则 [X]反 = [X]原

- 若X<0, 则 [X]反 = 对应原码的符号位不变,数值部分按位求反。

- 有[+0]和[-0]之分

- 补码:

- 若X>0, 则 [X]补 = [X]反= [X]原

- 若X<0, 则 [X]补 = [X]反+1

- 没有[+0]和[-0]之分

- 原码:最高位为符号位,其余为真值部分

- 无符号整数的表示范围(n表示字长): 0 ≤ X ≤ 2^n - 1

- 有符号整数的表示范围:

- 原码和反码: -(2^(n-1) -1) ≤ X ≤ 2^(n-1) -1

- 补码: -2^(n-1) ≤ X ≤ 2^(n-1) -1

- 对8位二进制数:

- 原码: -127 ~+127

- 反码: -127 ~+127

- 补码: -128 ~+127

第七讲 基本逻辑运算和逻辑门

- 逻辑,命题,推理

- 基本逻辑运算:与或非

- 逻辑运算是按位进行的运算,低位运算结果对高位运算不产生影响

- 算术运算是两个数之间的运算,低位运算结果将对高位运算产生影响

第八讲 基本逻辑运算及其门电路

- 与非,或非,异或,同或

第二章 微处理器与总线

第九讲 8088/8086微处理器

- 8088/8086 CPU的特点

- 采用并行流水线工作方式

- 通过设置指令预取队列实现

- 对内存空间实行分段管理

- 将内存分为4个段并设置地址段寄存器,以实现对1MB空间的寻址

- 支持协处理器

- 采用并行流水线工作方式

- 8088/8086可工作于两种模式下

- 最小模式:单处理器模式,所有控制信号由微处理器产生

- 最大模式:最大模式为多处理器模式,部分控制信号由外部总线控制器产生

- 最小模式:单处理器模式,所有控制信号由微处理器产生

第十讲 8088的主要引线及其内部结构

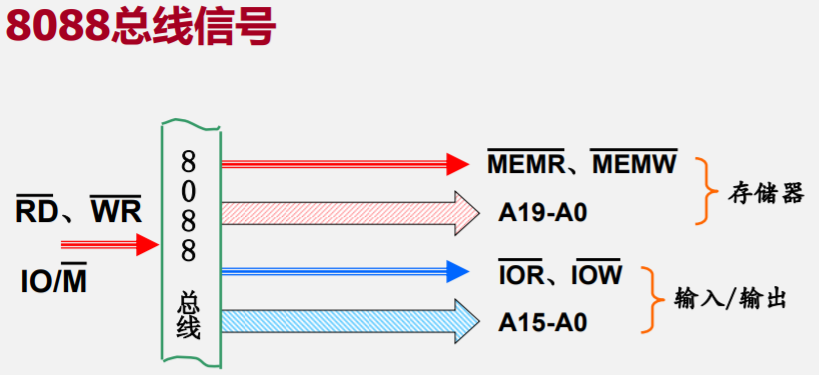

- 8088最小模式下的主要引脚信号

- 完成一次访问内存或接口所需要的主要信号

- 与外部同步控制信号

- 中断请求和响应信号

- 总线保持和响应信号

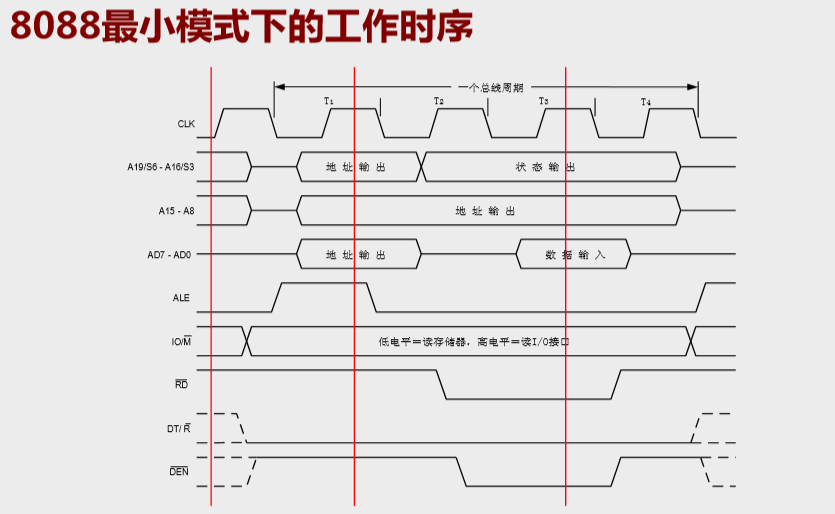

- 主要控制信号

- WR: 写信号;

- RD: 读信号;

- IO/M:为“0”表示访问内存,为“1”表示访问接口;

- DEN: 低电平有效时,允许进行读/写操作;

- DT/R:数据收发器的传送方向控制;

- ALE: 地址锁存信号;

- RESET:复位信号。

- 中断请求和响应信号

- INTR:可屏蔽中断请求输入端

- NMI: 非屏蔽中断请求输入端

- INTA:中断响应输出端

- 总线保持信号

- HOLD:总线保持请求信号输入端。当CPU以外的其他设备要求占用总线时,通过该引脚向CPU发出请求。

- HLDA:总线保持响应信号输出端。CPU对HOLD信号的响应信号。

- 微处理器读取一条指令的控制过程

- 1.发出读取数据所在的目标地址

- 内存储器单元地址

- I/O接口地址

- 2.发出读控制信号

- 3.送出传输的数据

- 1.发出读取数据所在的目标地址

- 地址线和数据线:

- 20位地址信号(20根地址线)–》可产生2^20=1M个编码

- 8位数据信号(8位数据线)–》可同时传输8bit二进制码

- 8088内部结构:

- 执行单元EU

- 构成:运算器,8个通用寄存器,1个标志寄存器,EU部分控制电路

- 功能:指令译码,指令执行,暂存中间运算结果,保存运算结果特征

- 总线接口单元BIU

- 功能:

- 从内存中取指令到指令预取队列,指令预取队列是并行流水线工作的基础

- 负责与内存或输入/输出接口之间的数据传送

- 在执行转移程序时,BIU使指令预取队列复位,从指定的新地址取指令,并立即传给执行单元执行。

- 执行单元EU

- 指令预取队列的存在使EU和BIU两个部分可同时进行工作

- 8088和8086CPU引线功能比较

- 数据总线宽度不同:8088的外部总线宽度是8位,8086为16位。

- 访问存储器和输入输出控制信号含义不同:8088——IO/M=0表示访问内存;8086——IO/M=1表示访问内存。

- 其他部分引线功能的区别

第十一讲 8088CPU内部寄存器

- 含14个16位寄存器,按功能可分为三类:

- 8个通用寄存器

- 数据寄存器(AX,BX,CX,DX)

- 地址指针寄存器(SP,BP)

- 变址寄存器(SI,DI)

- 4个段寄存器

- 2个控制寄存器

- 8个通用寄存器

- 通用寄存器:

- 数据寄存器:8088/8086含4个16位数据寄存器,它们又可分为8个8位寄存器,即:

- AX-------AH,AL:累加器,所有I/O指令都通过AX与接口传送信息,中间运算结果也多放于AX中;

- BX-------BH,BL:基址寄存器,在间接寻址中用于存放基地址

- CX-------CH,CL:计数寄存器,用于在循环或串操作指令中存放计数值

- DX-------DH,DL:数据寄存器,在间接寻址的I/O指令中存放I/O端口地址;在32位乘除法运算时,存放高16位数。

- 地址指针寄存器:

- SP:堆栈指针寄存器,其内容为栈顶的偏移地址

- BP:基址指针寄存器,常用于在访问内存时存放内存单元的偏移地址。

- 变址寄存器

- SI:源变址寄存器

- DI:目标变址寄存器

- 变址寄存器在指令中常用于存放数据在内存中的地址。

- 数据寄存器:8088/8086含4个16位数据寄存器,它们又可分为8个8位寄存器,即:

- BX与BP在应用上的区别

- 作为通用寄存器,二者均可用于存放数据;

- 作为基址寄存器,用BX表示所寻找的数据在数据段;用BP 则表示数据在堆栈段。

- 段寄存器:

- 作用:用于存放相应逻辑段的段基地址

- 8086/8088内存中逻辑段的类型

- 代码段: 存放指令代码

- 数据段: 存放操作的数据

- 附加段: 存放附加的操作的数据

- 堆栈段: 存放暂时不用但需保存的数据。

- CS:代码段寄存器,存放代码段的段基地址。

- DS:数据段寄存器,存放数据段的段基地址。

- ES:附加段寄存器,存放附加段的段基地址。

- SS:堆栈段寄存器,存放堆栈段的段基地址

- 段寄存器的值表明相应逻辑段在内存中的位置

- 控制寄存器:

- 指令指针控制寄存器IP

- 状态标志寄存器FLAGS

- 状态标志位:

- CF:进位标志位。加(减)法运算时,若最高位有进(借)位则CF=1

- OF:溢出标志位。当算术运算的结果超出了有符号数的可表达范围时,OF=l

- ZF:零标志位。当运算结果为零时ZF=1

- SF:符号标志位。当运算结果的最高位为1时,SF=l

- PF:奇偶标志位。运算结果的低8位中“1”的个数为偶数时PF=l

- AF:辅助进位标志位。加(减)操作中,若Bit3(D3)向Bit4(D4)有进位(借位), AF=1

- 控制标志位:

- TF:单步陷阱标志位,也叫跟踪标志位。TF=1时,使CPU处于单步执行指令的工作方式。

- IF:中断允许标志位。IF=1时,CPU可以响应中断请求。

- DF:方向标志位。在数据串操作时确定操作的方向。

- 状态标志位:

第十二讲 实模式下的存储器寻址

- 存储单位地址及其内容表示

- 若X表示某个单元地址,则[X]表示X单元的内容

- 例如:[0004H]=34H代表34存放在4号单元,而[0004H]=1234H,代表34存放在4号单元,12存放在5号单元

- 字的存储

- 占连续两个字节(16位)

- 低对低,高对高

- 用低位地址来表示字的地址

- 规则存放,非规则存放

- 8088:数据总线8位,每次传送1个字节

- 8086:数据总线16位

- 字:16位,规则字,以偶地址开始存放

- 字节: 高8位传送奇地址,低8位传送偶地址

- 内存储器管理

- 8088CPU是16位体系结构的微处理器

- 可以同时处理16位二进制码

- 8088CPU需要管理1MB内存

- 分段技术

- 分为若干个逻辑段,取内地址,用16位表示,每段最大64KB

- 对段首地址(物理地址)规定,段首地址低4位为0,例如:00000H,00010H,FFFF0H

- 段地址:段的起始地址的高16位

- 偏移地址:段内相对于段的起始地址的偏移量(字节数)

- 实地址模式下的存储器地址变换

- 内存物理地址由段基地址和偏移地址组成

- 物理地址=段基地址×16+偏移地址

- 内存地址变换

- 内存单元编址

- 段(基)地址

- 段内地址(相对地址/偏移地址)

- 存储器的编址

- 段(基)地址

- 相对地址(偏移地址)

- 逻辑段的起始地址称为段首,段首的偏移地址0000H

- 内存单元编址

- 段寄存器:

- 作用:用于存放相应逻辑段的段基地址

- 8086/8088内存中逻辑段的类型

- 代码段==>CS(代码段寄存器)

- CS×16+IP

- 数据段==>DS(数据段寄存器)

- DS×16+偏移地址

- 附加段==>ES(附加段寄存器)

- ES×16+偏移地址

- 堆栈段==>SS(堆栈段寄存器)

- SS×16+SP

- 代码段==>CS(代码段寄存器)

- 8086/8088内存中每类逻辑段的数量最多64K个

- 逻辑段与逻辑地址

- 内存的分段式逻辑分段,不是物理段

- 两个逻辑段可以完全重合或部分重合

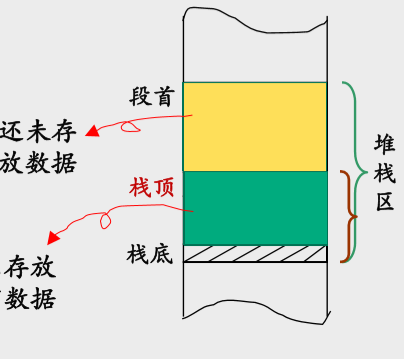

- 堆栈及堆栈段的使用

- 堆栈:

- 内存中一个特殊区域,用于存放暂时不用或需要保护的数据。

- 常用于响应中断或子程序调用

- 堆栈:

第十三讲 8088 系统总线

- 总线时序

- CPU工作时序

- CPU各引脚信号在时间上的关系

- 总线周期

- CPU完成一次访问内存(或接口)操作所需要的时间

- 8086的基本总线周期为4个时钟周期,每个时钟周期间隔称为一个T状态(8086/8088:5MHz时钟信号,时钟周期T=200ns)

- T1 状态:BIU将RAM或I/O地址放在地址/数据复用 总线(AD)上。

- T2 状态:

- 读总线周期: A/D总线为接收数据做准备。改变线路的方向。

- 写总线周期: A/D总线上形成待写的数据,且保持到总线周期的结束(T4)。

- T3, T4:对于读或写总线周期,AD总线上均为数据。

- Tw: 当RAM或I/O接口速度不够时,T3与 T4 之间可插入等待状态 Tw 。

- Ti : 当BIU无访问操作数和取指令的任务时,8086不执行总线操作,总线周期处于空闲状态 Ti 。

- CPU工作时序

- 总线:

- 按层次结构分类:

- CPU总线

- 系统总线

- 外部总线

- 按传送信息的类别分类:

- 地址总线

- 数据总线

- 控制总线

- 按总线在微机系统的位置分类:

- 片内总线

- 片间总线

- 系统总线

- 通信总线

- 总线的基本功能

- 数据传送

- 仲裁控制

- 出错处理

- 总线驱动

- 总线的主要性能指标

- 总线带宽(B/S)

- 单位时间内总线上可传送的数据量

- 总线带宽=位宽×工作频率

- 总线位宽(bit)

- 能同时传送的数据位数

- 总线的工作频率(MHz)

- 总线带宽=(位宽/8)×(工作频率/每个存储周期的时钟数)

- 总线带宽(B/S)

- 按层次结构分类:

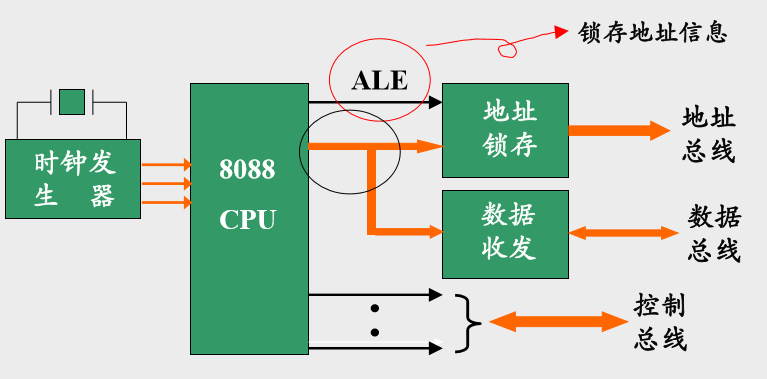

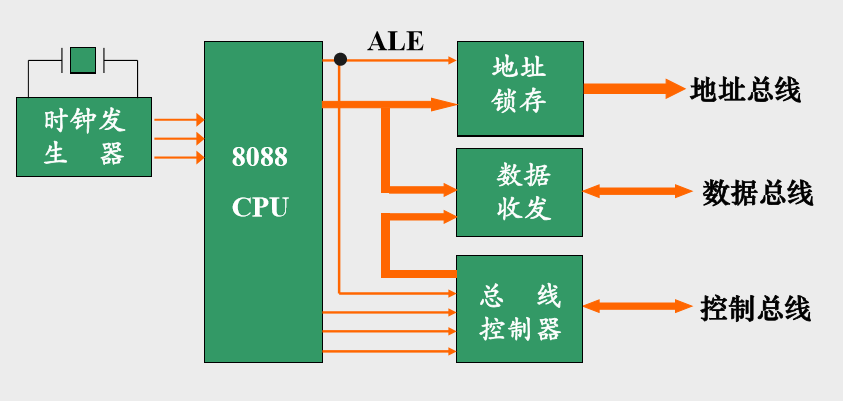

- 引脚信号设计特点

- 分时复用,如引脚AD0-AD15

- 如何实现:增加地址锁存器

- 8282三位锁存器

- 8286八位数据收发器

- 两种工作模式复用

- 最大模式

- 最小模式

- 分时复用,如引脚AD0-AD15

第三章 指令系统概述

第十四讲 8088/8086指令系统

- 指令:控制计算机完成某种操作的命令

- 指令系统:处理器所能识别的所有指令的集合

- 指令的兼容性:同一系列机的指令都是兼容的

- 一条指令应包含的信息:

- 运算数据的来源

- 运算结果的去向

- 执行的操作

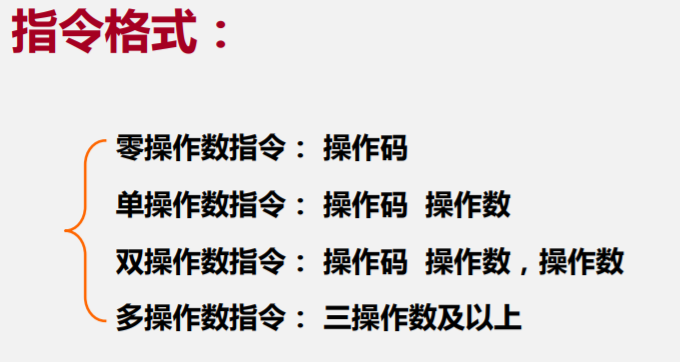

- 指令格式

- 指令中的操作数

- 立即数:参加操作的数据本身,可以是8位或16位,只能作为源操作数,无法作为目标操作数

MOV AX, 1234H

- 寄存器:数据存放地址

MOV AX, BX

- 存储器:数据存放地址

- 参加运算的数存放在存储器的某一个或两个单元中

- 表现形式: [操作数在内存中的偏移地址]

MOV AL, [1200H]

- 立即数:参加操作的数据本身,可以是8位或16位,只能作为源操作数,无法作为目标操作数

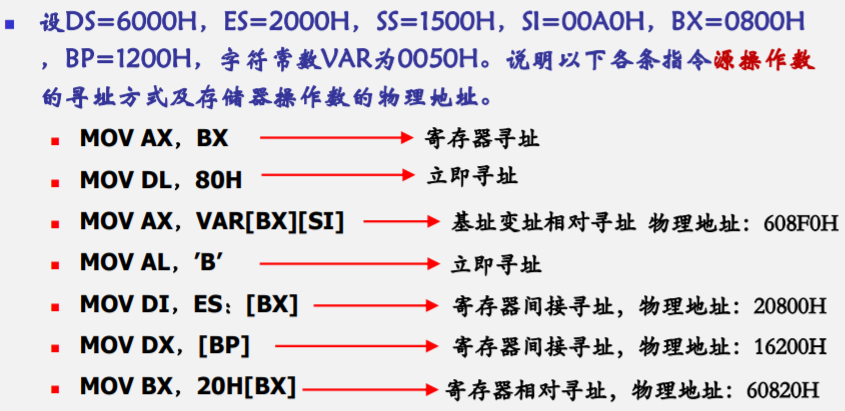

第十五讲 指令的寻址方式

-

操作数可能的来源或运算结果可能的去处:

- 由指令直接给出

- 寄存器

- 内存单元

-

寻找操作数所在地址的方法可以有三种大类型:

- 指令直接给出的方式

- 存放于寄存器中的寻址方式

- 存放于存储器中的寻址方式

-

1.直接寻址:

- 指令中直接给出操作数的偏移地址

- 直接寻址方式下,操作数默认为在数据段,但允许段重设,即由指令给出所在逻辑段。

MOV AX,ES:[1200H]ES:段重设符

-

2.寄存器间接寻址

- 操作数存放在内存中,数据在内存中的偏移地址为方括号中通用寄存器的内容

- 仅有4个通用寄存器可用于存放数据的偏移地址,

BX,BP,SI,DI- 若使用

BX,SI,DI,则操作数在数据段DS中- 物理地址=DS×16+{BX/SI/DI}

- 若使用

BP,则操作数在堆栈段SS中- 物理地址=SS×16+BP

- 若使用

- 间接寻址的一般格式:[ 间址寄存器 ]

- 例:

MOV AX,[BX] - 可以段重设

-

3.寄存器相对寻址

- 操作数的偏移地址为寄存器的内容加上一个位移量

- 相对寻址主要用于一维数组的操作

MOV AX,[BX+DATA]

-

4.基址、变址寻址

- 操作数的偏移地址为

- 一个基址寄存器的内容 + 一个变址寄存器的内容;

- 操作数的段地址由选择的基址寄存器决定

- 基址寄存器为

BX,默认在数据段DS - 基址寄存器为

BP,默认在堆栈段SS

- 基址寄存器为

- 基址变址寻址方式与相对寻址方式一样,主要用于一维数组操作。

- 操作数的偏移地址为

-

5.基址、变址、相对寻址

- 操作数的偏移地址为:

- 基址寄存器内容+变址寄存器内容+位移量

- 操作数的段地址由选择的基址寄存器决定。

- 基址变址相对寻址方式主要用于二维表格操作。

- 例如:

MOV AL, [BP][DI]5==>也可以表示为[BP+DI+5]

- 操作数的偏移地址为:

-

6.隐含寻址

- 指令中隐含了一个或两个操作数的地址,即操作数在默认的地址中。

- 例:

MUL BL

- 指令执行:

AL×BL-->AX

-

I/O端口寻址方式

- 直接端口寻址

- 由指令提供一个8位端数(0-255)

- 间接端口寻址

- 由DX寄存器给出,寻址64KB

- 直接端口寻址

第十六讲 数据传送指令

- 8086指令系统从功能上包括六大类:

- 数据传送

- 算术运算

- 逻辑运算和移位

- 串操作

- 程序控制

- 处理器控制

- 数据传送类指令

- 1.通用数据传送指令

- 一般数据传送指令

MOV- 格式:

MOV dest,src - 操作:

src->dest - 例子:

MOV AL, BL - 注意点:两操作数字长必须相同;两操作数不允许同时为存储器操作数;两操作数不允许同时为段寄存器;在源操作数是立即数时,目标操作数不能是段寄存器;IP和CS不作为目标操作数,FLAGS一般也不作为操作数在指令中出现。

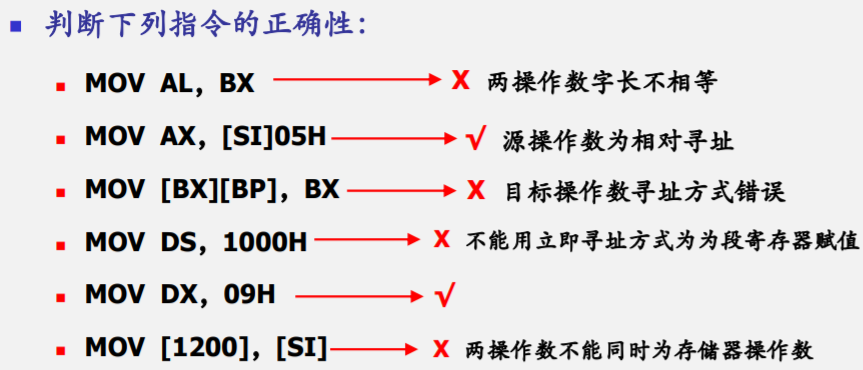

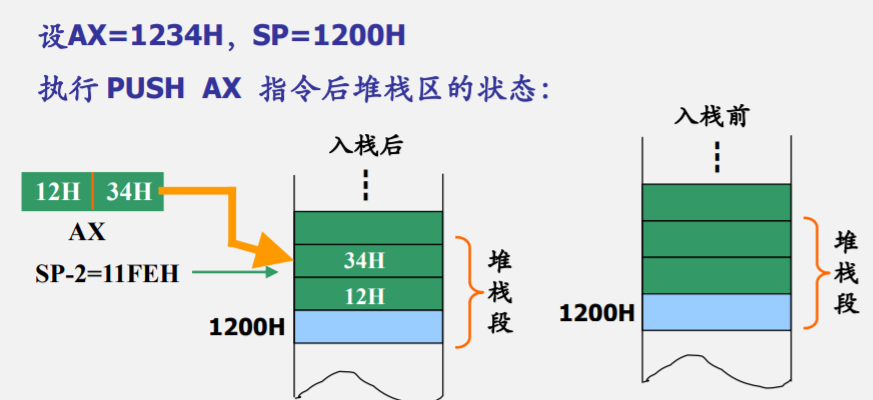

- 堆栈操作指令

- 先进后出,以字为单位

- 压栈:

PUSH OPRD16位寄存器或存储器两单元

- 出栈:

POP OPRD

- 指令的操作数必须是16位;操作数可以是寄存器或存储器两单元,但不能是立即数;不能从栈顶弹出一个字给CS;PUSH和POP指令在程序中一般成对出现;PUSH指令的操作方向是从

高地址向低地址,而POP指令的操作正好相反。 - 堆栈指针寄存器SP指向栈顶位置

- 交换指令

- 格式:

XCHG REG,MEM/REG - 注:两操作数必须有一个是寄存器操作数;不允许使用段寄存器。

- 例:

XCHG AX, BX,XCHG [2000], CL

- 格式:

- 查表转换指令

- 格式:

XLAT - 说明:用BX的内容代表表格首地址,AL内容为表内位移量,BX+AL得到要查找元素的偏移地址

- 操作:将BX+AL所指单元的内容送AL(将BX为首地址的,偏移地址为AL的内容送给AL。)

- 格式:

- 字位扩展指令

- 将符号数的符号位扩展到高位;

- 指令为零操作数指令,采用隐含寻址,隐含的操作数为AX及AX,DX

- 无符号数的扩展规则为在高位补0

- 字节到字:

CBW,将AL内容扩展到AX ,若AL最高位=1,则执行后AH=FFH,若AL最高位=0,则执行后AH=00H 。AL不变(即将AL的符号位移至AH)- CBW属符号扩展指令,它可以把8位扩展到16位,扩展前后两数的真值不变,主要用于数据类型不同时用符号扩展指令可以使得数据类型相同。

- 字到双字:

CWD,将AX内容扩展到DX AX ,若AX最高位=1,则执行后DX=FFFFH,若AX最高位=0,则执行后DX=0000H- CWD的作用是将带符号的16位整数(AX)转为32位的带符号位的整数(DX:AX),例如:AX=0xFFFE, 转为32位带符号位的整数时,DX=0xFFFF,AX=0XFFFE.又例如:AX=0x0002,转为带符号位的整数时DX=0x0000,AX=0x0002.

- 一般数据传送指令

- 2.输入输出指令

- 从端口地址读入数据到累加器/将累加器的值输出到端口中

- 指令格式:

- 输入指令:

IN acc,PORT - 输出指令 :

OUT PORT,acc

- 输入指令:

- 根据端口地址码的长度,指令具有两种不同的端口地址表现形式:直接寻址,间接寻址

- 3.地址传送指令

LEA取偏移地址指令- 将变量的16位偏移地址写入到目标寄存器

LEA REG,SRC

LDS指令LDS(Load pointer using DS)的一般格式:LDS 通用寄存器,存储器操作数(32位)

LES指令LDS和LES均用于将一个32位的远地址指针写入到目标寄存器。LES(Load pointer using ES)的一般格式:LES 通用寄存器,存储器操作数(32位)

- 4.标志传送指令

- 隐含操作数AH,将FLAGS的低8位装入AH

LAHF(Load AH from Flags)SAHF(Store AH into Flags)

- 隐含操作数FLAGS

PUSHF(Push flags onto stack)POPF(Pop flags off stack)

- 除标志传送指令外,其它指令的执行对标志位不产生影响

- 隐含操作数AH,将FLAGS的低8位装入AH

- 1.通用数据传送指令

第四章 算术运算,逻辑运算与移位操作指令

第十七讲 算术运算类指令

- 加法运算指令

- 1.

ADD加法指令- 格式:

ADD OPRD1,OPRD2 - 操作:

OPRD1+OPRD2-->OPRD1 - ADD指令的执行对全部6个状态标志位都产生影响

- 格式:

- 2.

ADC带进位的加法指令OPRD1+OPRD2+CF-->OPRD1

- 3.

INC加1指令- 格式:

INC OPRD - 操作:

OPRD+1-->OPRD - 常用于在程序中修改地址指针,OPRD不能是段寄存器,不能是立即数,除CF外,影响其他标志位

- 格式:

- 1.

- 减法运算指令

- 1.普通减法指令

SUB- 格式:

SUB OPRD1,OPRD2 - 操作:

OPRD1- OPRD2-->OPRD1 - 对标志位的影响与ADD指令同

- 格式:

- 2.考虑借位的减法指令

SBB- 操作:

OPRD1- OPRD2- CF-->OPRD1

- 操作:

- 3.减1指令

DEC- 格式:

DEC OPRD - 操作:

OPRD - 1-->OPRD - 除了不影响CF外,影响其他标志位

- 格式:

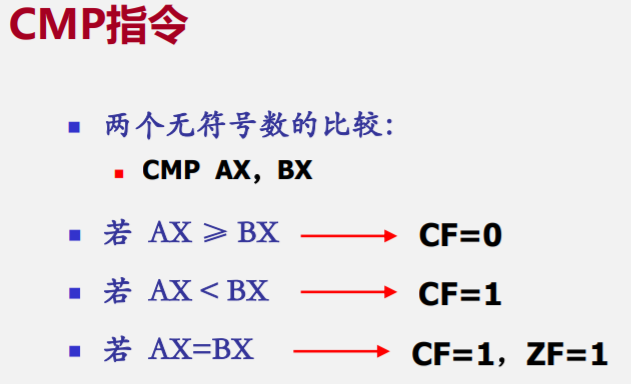

- 4.比较指令

CMP- 格式:

CMP OPRD1,OPRD2 - 操作:

OPRD1- OPRD2 - 指令执行的结果不影响目标操作数,仅影响标志位!

- 格式:

- 5.求补指令

NEGNEG OPRD- 操作:

0-OPRD-->OPRD

- 1.普通减法指令

- 乘法指令

- 乘法指令采用隐含寻址,隐含的是存放被乘数的累加器AL或AX及存放结果的AX,DX;

- 1.无符号的乘法指令MUL

MUL OPRD不能是立即数和段寄存器- 操作:

- OPRD为字节数

AL×OPRD-->AX - OPRD为16位数

AX×OPRD-->DX,AX

- OPRD为字节数

- 2.带符号的乘法指令IMUL

- 格式:

IMUL OPRD - 指令格式及对操作数的要求与MUL指令相同。

- 指令执行原理:

- ① 将两个操作数取补码(对负数按位取反加1,正数不变);

- ② 做乘法运算;

- ③ 将乘积按位取反加1。

- 格式:

- 除法指令

- 1.无符号除法指令

- 格式:

DIV OPRD - 操作:

- 操作数是字节(8位):

AX/OPRD,商–>AL,余数–>AH - 操作数是字(16位):

DX,AX/OPRD,商–>AX,余数–>DX

- 操作数是字节(8位):

- 格式:

- 2.有符号除法指令

- 格式:

IDIV OPRD - 指令格式及对操作数的要求与DIV指令相同。

- 格式:

- 注:

- 余数符号与被除数相同

- 范围

- 双字/字:商范围 -32768到+32767

- 字/字节:商范围 -128到+127

- 超过范围按除数为0处理,产生0号中断

算术运算指令的执行大多对状态标志位会产生影响

- 1.无符号除法指令

第十八讲 逻辑运算指令

- 逻辑运算指令

- 对操作数的要求:

- 大多与MOV指令相同。

- “非”运算指令要求操作数不能是立即数;

- 对标志位的影响

- 除“非”运算指令,其余指令的执行都会影响除

AF外的5个状态标志; - 无论执行结果如何,都会使标志位

OF=CF=0。 - “非”运算指令的执行不影响标志位。

- 除“非”运算指令,其余指令的执行都会影响除

- 对操作数的要求:

- 1."与"指令

- 格式:

AND OPRD1,OPRD2 - 操作:两操作数相“与”,结果送目标地址。

(OPRD1)∧(OPRD2)-->(OPRD1) - CF=0,OF=0,SF,ZF,PF有影响,对AF无影响

- 格式:

- 2."或"指令

- 格式:

OR OPRD1,OPRD2 - 操作:两操作数相“或”,结果送目标地址

- 格式:

- 3."非"指令

- 格式:

NOT OPRD - 操作:操作数按位取反再送回原地址

- 格式:

- 4."异或"指令

- 格式:

XOR OPRD1,OPRD2 - 操作:两操作数相“异或”,结果送目标地址

- 格式:

- 5."测试"指令

- 格式:

TEST OPRD1,OPRD2 - 操作:执行“与”运算,但运算的结果不送回目标地址。

- 应用:常用于测试某些位的状态

- 格式:

第十九讲 移位操作指令

- 移位操作指令

- 控制二进制位向左或向右移动的指令

- 非循环移位指令

- 循环移位指令

- 移动移动1位时由指令直接给出;移动两位及以上时,移位次数必须由CL指定

- 控制二进制位向左或向右移动的指令

- 1.非循环移位指令

- 逻辑左移

SHL- 格式:

SHL OPR,CNT - 注:

- OPR不能是立即数和段寄存器操作数

- CNT移位次数,若为1,直接写在指令中,若为几,必须先写入CL中

- 对CF,OP,PF,ZF,SF有影响,对AF无意义

- 格式:

- 算术左移

SAL- 格式:

SAL OPR,CNT - 操作同

SHL

- 格式:

- 逻辑右移

SHR- 格式:

SHR OPR,CNT

- 格式:

- 算术右移

SAR- 格式:

SAR OPR,CNT - 操作:左边补上符号位,和之前的符号一样

- 格式:

- 逻辑左移

- 2.循环移位指令

- 不带进位位的循环移位

- 左移

ROL- 格式:

ROL OPR,CNT

- 格式:

- 右移

ROR- 格式:

ROR OPR,CNT

- 格式:

- 左移

- 带进位位的循环移位

- 左移

RCL- 格式:

RCL OPR,CNT

- 格式:

- 右移

RCR- 格式:

RCR OPR,CNT

- 格式:

- 左移

- 不带进位位的循环移位

第五章 串操作指令

第二十讲 串操作指令

- 针对数据块或字符串的操作

- 可实现存储器到存储器的数据传送;

- 待操作的数据串称为源串,目标地址称为目标串。

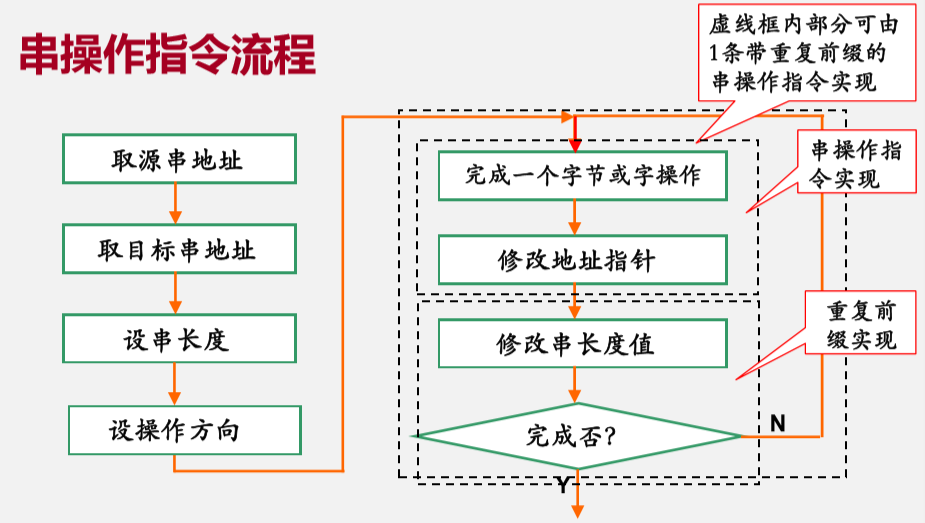

- 串操作指令的操作对象是多个字节数(一串字符或数据),因此,指令的执行需要确定:

- 串所在的区域

- 源串一般存放在数据段,偏移地址由SI指定。允许段重设。

- 目标串必须在附加段,偏移地址由DI指定

- 串的首地址(原串、目标串起始地址)

- 串长度(大小)

- 串长度值由CX指定

- 串的操作方向

- 由DF标志位决定。指令根据DF状态自动修改地址指针

- DF=0 增地址方向

- DF=1 减地址方向

- 由DF标志位决定。指令根据DF状态自动修改地址指针

- 串所在的区域

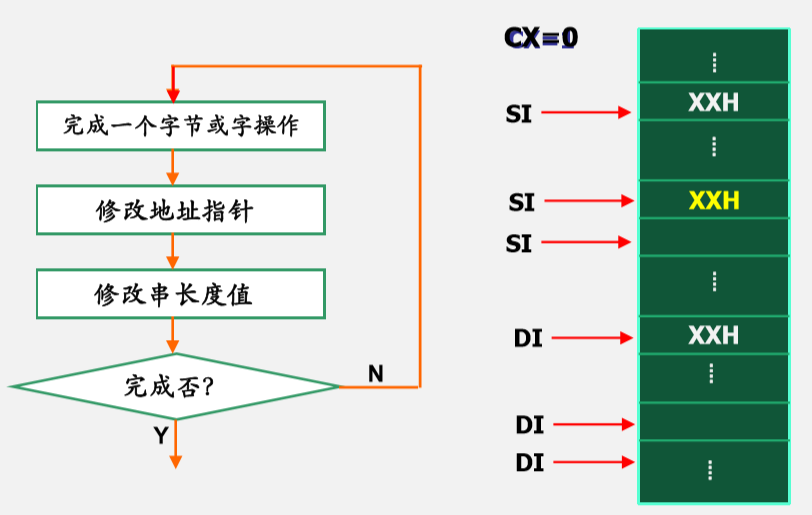

- 通过增加重复前缀, 可以实现对CX值的自动修改

- 无条件重复

- REP

- 当CX≠0时,REP后的指令将继续重复执行

- 常用于传送类指令前–》未传完则继续传送

- 条件重复

- 相等(为零)重复:REPE(REPZ)

- CX≠0 ∩ ZF=1,则前缀后的指令将继续重复执行

- 不相等(不为零)重复:REPNE( REPNZ)

- CX≠0 ∩ ZF=0,则前缀后的指令将继续重复执行

- 条件前缀常用于运算类指令前,当:

- 1)操作未结束 AND 结果=0

- 2)操作未结束 AND 结果≠0 使其后的指令继续重复执行。

- 串操作指令

- 串传送

MOVS - 串比较

CMPS - 串扫描

SCAS - 串装入

LODS - 串送存

STOS

- 串传送

第二十一讲 串传送与串比较指令

1.串传送指令

- 功能:将原数据串传送到目标地址

- 格式:

MOVS OPRD1,OPRD2MOVSB,按字节传送MOVSW,按字传送

- 串传送指令常与无条件重复前缀连用

2.串比较指令 - 功能:用于实现两个数据串的比较

- 操作:

- 目标串-源串,结果不写回目标地址

- 常与条件重复前缀连用

- 格式:

CMPS OPRD1,OPRD2CMPSBCMPSW

- 前缀的操作对标志位不影响

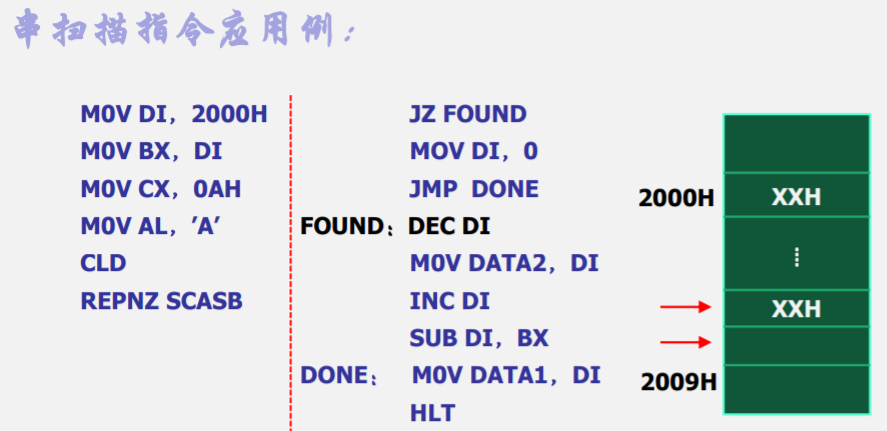

第二十二讲 串扫描指令

-

格式:

SCAS OPRDSCASBSCASW

-

执行与CMPS指令相似的操作,区别是:这里的源操作数是AX或AL

-

串扫描指令应用例:

- 在ES段中从2000H单元开始存放了10个字符,寻找其中有无字符“A”。若有则记下搜索次数,将搜索次数写入到DATA1单元,并将存放“A”的地址写入DATA2单元。

第二十三讲 串装入与串存储指令

1.串装入指令

-

格式:

LODS OPRDLODSBLODSW

-

操作:

- 对字节:AL [DS:SI]

- 对 字:AX [DS:SI]

2.串存储指令

-

格式:

STOS OPRDSTOSBSTOSW

-

操作:

- 对字节: AL [ES:DI]

- 对 字: AX [ES:DI]

-

串操作指令应用注意事项:

- 需要定义附加段

- 目标操作数必须在附加段

- 需要设置数据的操作方向

- 确定DF的状态

- 源串和目标串指针分别为SI和DI

- 串长度值必须由CX给出

- 注意重复前缀的使用方法

- 传送类指令前加无条件重复前缀

- 串比较类指令前加条件重复前缀,但前缀不影响ZF状态

- 需要定义附加段

第六章 程序与处理器控制指令

第二十四讲 程序控制指令

- 程序控制类指令

- 转移指令

- 通过修改指令的偏移地址或段地址及偏移地址实现程序的转移

- 无条件转移指令–>无条件转移到目标地址

JMP OPRD- 段内直接转移

- 当偏移量为8位时,称为段内直接短跳转

- 格式:

JMP (SHORT) 标号 - 操作:

(IP)<--disp8+(IP)

- 格式:

- 当偏移量为8位时,称为段内直接近跳转

- 格式:

JMP (NEAR PTR) 标号 - 操作:

(IP)<--disp16+(IP)

- 格式:

- 当偏移量为8位时,称为段内直接短跳转

- 段内间接转移

JMP BP- 转向(SS):(BP)

JMP BX- 转向(CS):(BX)

JMP (WORD PTR) [BX][DI]- 转向(CS):(BX)+(DI)

- 段间直接转移

JMP (FAR PTR) 标号- 执行该指令时,将把标号所在的段的值送CS,将标号在所属段内的偏移量送IP,从而形成新的转移地址CS:IP

- 段间间接转移

JMP DWORD PTR [BX]- 中间的

DWORD PTR不能省略,表示存储器双字操作数

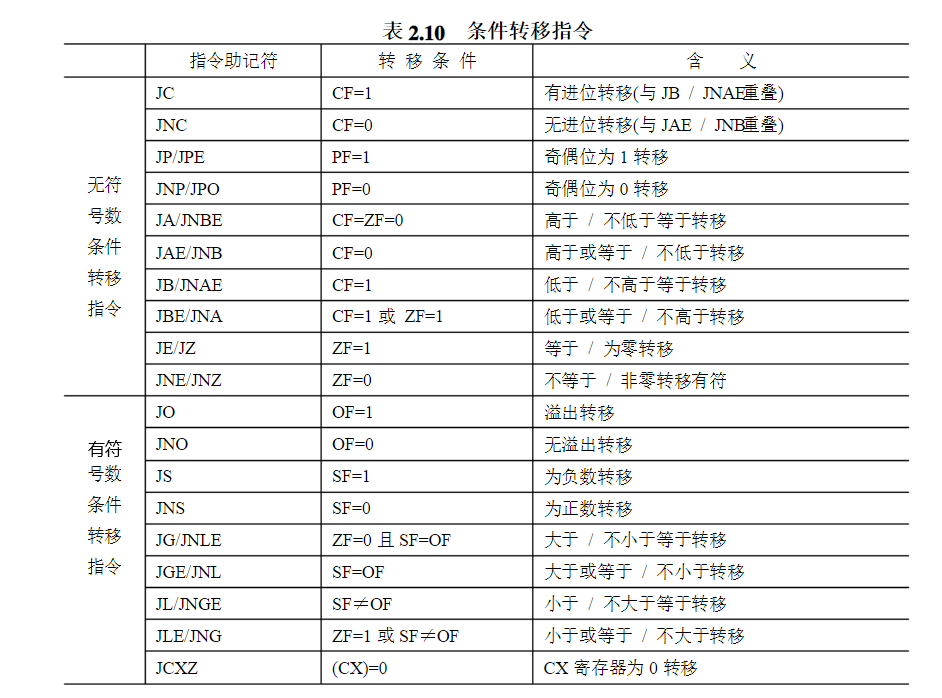

- 条件转移指令–>当具备一定条件时转移到目标地址

JC/JNC- 判断CF的状态。常用于两个无符号数大小比较

JZ/JNZ- 判断ZF的状态。常用于循环体的结束判断

JO/JNO- 判断OF的状态。常用于有符号数溢出的判断

JP/JNP- 判断PF的状态。用于判断运算结果低8位中1的个数是否为偶数

JS /JNS- 判断SF的状态。常用于判断数的性质

JA/JAE/JB/JBE- 判断CF或CF+ZF的状态。常用于无符号数大小的比较

JG/JGE/JL/JLE- 判断SF+OF或SF+OF+ZF的状态。常用于有符号数大小的比较

JCXZ- 可根据指令执行后CX的结果实现转移

- 可根据指令执行后CX的结果实现转移

- 循环控制

LOOP- 条件:CX≠0

LOOPZ- 条件:CX≠0,且ZF=1

LOOPNZ- 条件:CX≠0,且ZF=0

- 过程调用

- 用于调用一个子过程,必须保护返回地址

- 调用指令的执行过程

- ① 保护断点:将调用指令的下一条指令的地址(断点)压入堆栈

- ② 获取子过程的入口地址:子过程第1条指令的偏移地址

- ③ 执行子过程:功能实现,参数的保存及恢复

- ④ 恢复断点,返回原程序:将断点偏移地址由堆栈弹出

- 段内调用:被调用程序与调用程序在同一代码段

CALL NEAR PROCC

- 段间调用:子过程与原调用程序不在同一代码段

- 返回指令:

- 功能:从堆栈中弹出断点地址,返回原程序

- 格式:

RET - 子程序的最后一条指令必须是RET

- 中断控制

- 中断的概念:某种异常或随机事件使处理器暂时停止正在运行的程序,转去执行一段特殊处理程序,并在处理结束后返回原程序被中断处继续执行的过程。

- 中断指令:引起CPU产生一次中断的指令

- 格式:

INT n - 说明: nх4

- 格式:

- 中断指令的执行过程

- ① 将FLAGS压入堆栈;

- ② 将INT指令的下一条指令的CS、IP压栈;

- ③ 由n×4得到存放中断向量的地址;

- ④ 将中断向量(中断服务程序入口地址)送CS和IP寄存器;

- ⑤ 转入中断服务程序

- 中断返回指令:

- 格式:

IRET - 中断服务程序的最后一条指令,负责:恢复断点;恢复标志寄存器内容

- 格式:

- 转移指令

第二十五讲 处理器控制指令

- 这类指令用来对CPU进行控制,如修改标志寄存器,使CPU暂停,使CPU与外部设备同步等。

第七章 汇编语言

第二十六讲 汇编语言程序设计

- 汇编语言源程序与汇编程序

(1)汇编语言源程序:用助记符编写

(2)汇编程序:源程序的编译程序 - 汇编语言程序设计与执行过程

(1)输入汇编语言源程序:源文件.ASM

(2)汇编MASM:目标文件.OBJ

(3)链接LINK:可执行文件.EXE

(4)调试TD:最终程序 - 汇编语言语句类型和格式

(1)语句类型:指令性语句,指示性语句

(2)语句格式:

指令性语句:[标号:] [前缀] 助记符 [操作数],[操作数] [ ;注释]

指示性语句格式:[名字] 伪指令助记符 操作数 [,操作数,…] [ ;注释] - 汇编语言语句中的操作数

(1)寄存器

(2)存储器单元

(3)常量:(数字/字符串)

(4)变量或标号

(5)表达式 :算术运算;逻辑运算;关系运算;取值运算(OFFSET,SEG)和属性运算(PTR);其它运算

第二十七讲 数据定义伪代码

- 数据定义伪指令

(1)用于定义数据区中变量的类型及其所占内存空间大小

(2)DB(Define Byte):定义的变量为字节型

(3)DW (Define Word) :定义的变量为字类型

(4)DD (Define Double Word) :定义的变量为双字型

(5)DQ (Define Quadword) :定义的变量为4字型

(6)DT (Define Tenbytes) :定义的变量为10字节型 - 重复操作符

(1)当同样的操作数重复多次时,可以使用重复操作符

(2)作用:为一个数据区的各单元设置相同的初值

(3)格式:[变量名] 伪指令助记符 n DUP(初值 [,初值,… ] )

(4)例:M1 DB 10 DUP(0) - “?”的作用

(1)表示随机值,用于预留存储空间

(2)例:MEM1 DB 34H,’A’,?,例:DW 20 DUP(?) - 调整偏移量伪指令

(1)规定程序或变量在逻辑段中的起始地址

(2)格式:ORG 表达式

(3)例:

DATA SEGMENT

ORG 1200H

BUFF DB 1,2

DATA ENDS

第二十八讲 符号与段定义相关伪指令

- 符号定义伪指令

(1)将表达式的值赋给一个名字。当源程序中需多次引用某一表达式时,可以利用EQU伪指令,用一个符号代替表达式,以便于程序维护。

(2)格式:符号名 EQU 表达式

(3)操作:用符号名取代后边的表达式,不可重新定义

(4)例:CONSTANT EQU 100 - 段定义伪指令

(1)在汇编语言源程序中定义逻辑段

说明逻辑段的起始和结束

说明不同程序模块中同类逻辑段之间的联系形态

(2)格式:段名 SEGMENT [定位类型] [组合类型] [’类别’] - 设定段寄存器伪指令

(1)说明所定义逻辑段的性质

(2)格式:ASSUME 段寄存器名:段名[,段寄存器名:段名,…] - 结束伪指令

(1)表示源程序结束

(2)格式:END [标号]

第二十九讲 其他伪指令

- 过程定义伪指令

(1)用于定义一个过程体

(2)格式:

过程名 PROC [ NEAR / FAR ]

┇

RET

过程名 ENDP

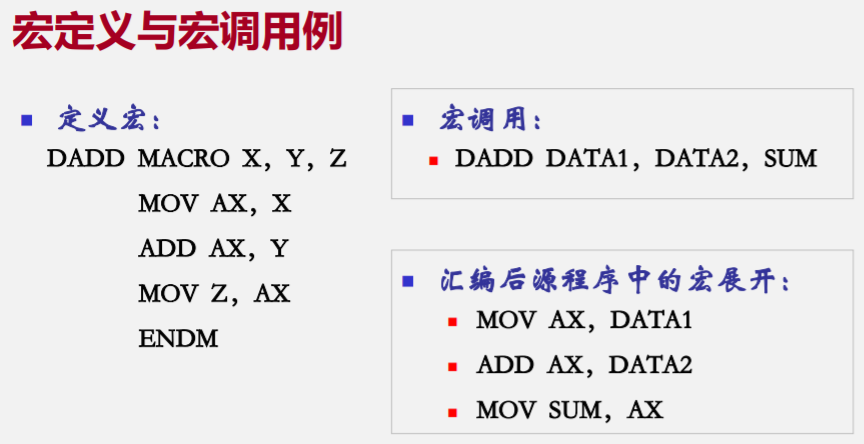

(3)

2. 宏命令伪指令

(1)宏:源程序中由汇编程序识别的具有独立功能的一段程序代码

(2)当源程序中需要多次使用同一个程序段时,可以将该程序段定义为一个宏

(3)格式:宏命令名 MACRO <形式参数>

(4)

第三十讲 系统功能调用

- BIOS、DOS功能调用

(1)BIOS:驻留在ROM中的基本输入/输出系统

加电自检,装入引导,主要I/O设备处理程序及接口控制

(2)DOS:磁盘操作系统

DOS功能/BIOS功能调用是调用系统内核子程序

(3)BIOS、DOS功能调用:DOS功能与BIOS功能均通过中断方式调用,DOS和BIOS中断均可能影响AX - DOS软中断

(1)DOS中断包括:设备管理,目录管理,文件管理,其它用中断类型码区分

(2)DOS软中断:类型码为21H - 单字符输入

(1)调用方法:

MOV AH,01

INT 21H

(2)输入的字符在AL中

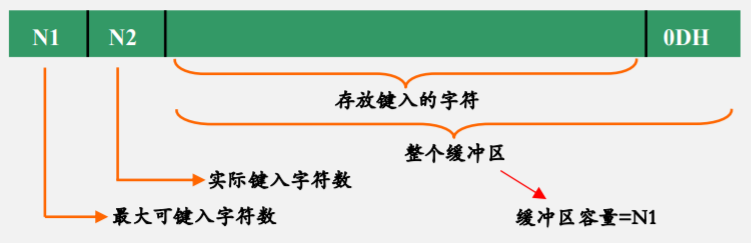

4. 字符串输入

(1)接收由键盘输入一串字符

(2)输入的字符串存储在内存指导区域中

(3)用户自定义缓冲区格式:

5. 单字符显示输出

6. 字符串显示输出

AH 功能号09H

DS:DX 待输出字符串的偏移地址

INT 21H

7. 返回操作系统(DOS)功能

(1)功能号:4CH

(2)调用格式:

MOV AH,4CH

INT 21H

(3)功能:程序执行完该2条语句后能正常返回OS;常位于程序结尾处

第八章 半导体存储器

第三十一讲 半导体存储器概述

- 半导体存储器

(1)由能够表示二进制数“0”和“1”的,具有记忆功能的半导体器件组成

(2)能存放一位二进制数的半导体器件称为一个存储元

(3)若干存储元构成一个存储单元 - 半导体存储器的分类

- 内存储器:

- 随机存取存储器(RAM)

- 静态存储器(SRAM)

- 动态存储器(DRAM)

- 只读存储器(ROM)

- 掩模ROM

- 一次性可写ROM

- 可读写ROM

- EPROM

- EEPROM

- PROM

- 随机存取存储器(RAM)

- 半导体存储器的主要技术指标

(1)存储容量:存储单元个数×每单元的二进制数位数

存储容量=2^m×N

(m:芯片地址线根数)

(N:芯片数据线根数)

(2)存取时间:实现一次读/写所需要的时间

(3)存取周期:连续启动两次独立的存储器操作所需间隔的最小时间

(4)可靠性,功耗

第三十二讲 微机中的存储器

- 微机中的存储器

(1)内存储器

主内存

高速缓冲存储器

(2)外存储器

联机外存

脱机外存

(3)虚拟存储器

| 内存 | 外存 | |

|---|---|---|

| 速度 | 快 | 慢 |

| 容量 | 小 | 大 |

| 单位容量价格 | 高 | 低 |

| 制造材料 | 半导体 | 磁性材料 |

-

微机中的存储系统主要有:

(1)Cache存储器系统

(2)虚拟存储器系统 -

随机存取存储器

(1)特点:可以随机读或写操作;掉电后存储内容即丢失

(2)类型:静态随机存取存储器(SRAM);动态随机存取存储器(DRAM)

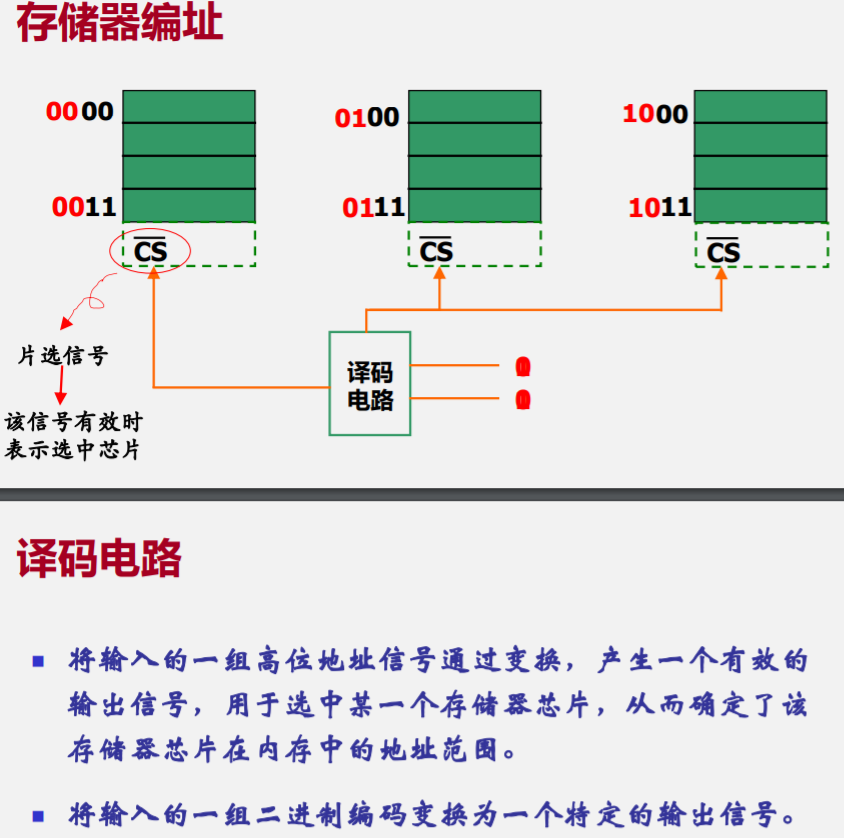

第三十三讲 存储单元的编址

- 地址译码电路

(1)单译码结构

(2)双译码结构

(3)3-8译码器(741S138)

第三十四讲 存储器扩展技术

- 存储器扩展:用已有的存储器芯片构造一个需要的存储空间

(1)用多片存储芯片构成一个需要的内存空间;

(2)各存储器芯片在整个内存中占据不同的地址范围;

(3)任一时刻仅有一片(或一组)被选中。

(4)存储器芯片的存储容量等于:单元数×每单元的位数 - 存储器扩展方法

(1)位扩展–》扩展字长

(2)字扩展–》扩展单元数

(3)字位扩展–》既扩展字长也扩展单元数

第九章 输入输出与中断技术

第三十五讲 输入输出技术概述

- I/O接口

(1)接口要解决的问题

速度匹配????数据的缓冲与暂存

信号的驱动能力????信号驱动

信号形式和电平的匹配????信号类型转换

信息格式????信号格式转换

时序匹配(定时关系)

总线隔离????三态门 - I/O端口及其编址

(1)端口:接口电路中用于缓存数据及控制信息的部件

(2)分类:数据端口,控制端口,状态端口

(3)I/0端口编址:为确保CPU能够访问到每个不同的端口

(4)寻址端口的方法:

- 先找到端口所在的接口电路芯片

- 再在该芯片上找具体访问的端口

- 若接口中仅有一个端口,则找到芯片即找到端口

- 若接口中有多个端口,则找到芯片后需再找端口

(5)每个端口地址=片选地址(高位地址)+片内地址

- I/O地址译码

(1)目的:确定端口的地址

(2)参加译码的信号:

#IOR,#IOW,高位地址信号

(3)对端口读/写信号的产生条件

- IO/#M=1

- #RD=0 #IOR=0

- #WR=0 #IOW=0

(4)当接口只有一个端口时:无片内地址,全部地址信号均为高位地址(可全部参与译码),译码输出直接选择该端口;

(5)当接口具有多个端口时:则16位地址线的高位参与译码(决定接口的基地址),而低位则用于确定要访问哪一个端口

第三十六讲 简单接口芯片

- 接口的分类及特点

(1)按传输信息的方向分类:

输入接口

输出接口

(2)按传输信息的类型分类:

数字接口

模拟接口

(3)按传输信息的方式分类:

并行接口

串行接口 - 接口特点

(1)输入接口:

要求对数据具有控制能力

常用三态门实现

(2)输出接口:

要求对数据具有锁存能力

常用锁存器实现

第三十七讲 基本输入输出方法

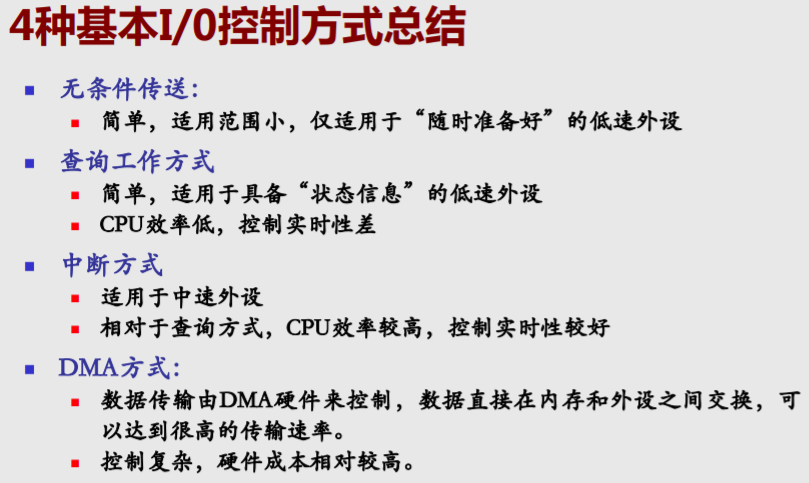

- 基本输入/输出方法

(1)无条件传送:要求外设总是处于准备好状态

优点:软件及接口硬件简单

缺点:只适用于简单外设,适应范围较窄

(2)查询式传送:仅当条件满足时才能进行数据传送;每满足一次条件只能进行一次数据传送。

适用场合:外设并不总是准备好;对传送速率和效率要求不高

工作条件:外设应提供设备状态信息;接口应具备状态端口

(3)中断方式传送

特点:外设在需要时向CPU提出请求,CPU再去为它服务。服务结束后或在外设不需要时,CPU可执行自己的程序。

优点:CPU效率高,实时性好,速度快。

缺点:程序编制相对较为复杂。

(4)直接存储器存取(DMA) :

特点:

①外设直接与存储器进行数据交换 ,CPU不再担当数据传输的中介者;

②总线由DMA控制器(DMAC)进行控制(CPU要放弃总线控制权),内存/外设的地址和读写控制信号均由DMAC提供。

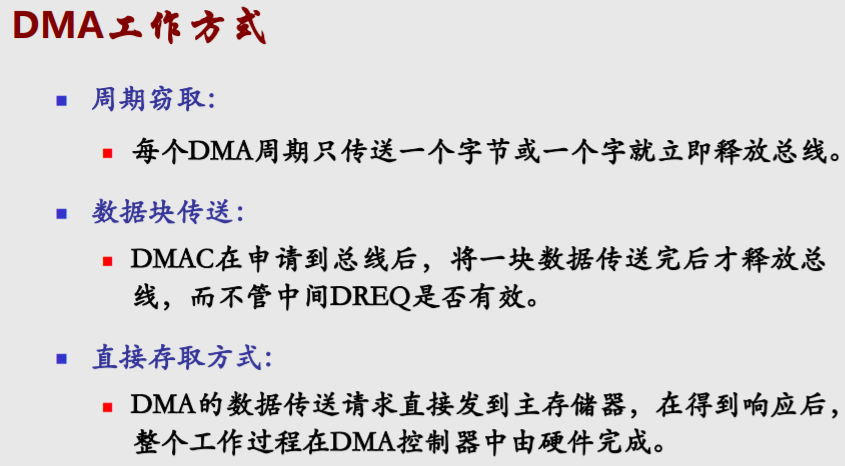

③DMA传送方式有单元传送方式,快传送方式,请求传送方式

DMA控制器8237A

第三十八讲 中断技术

- 中断的基本概念

(1)CPU执行程序时,由于发生了某种随机的事件(外部或内部),

引起CPU暂时中断正在运行的程序,转去执行一段特殊的服务

程序,以处理该事件,该事件处理完后又返回被中断的程序

继续执行,这一过程称为中断。

(2)引入中断的原因

提高对外设请求的响应实时性。

提高了CPU的利用率

避免了CPU不断检测外设状态的过程

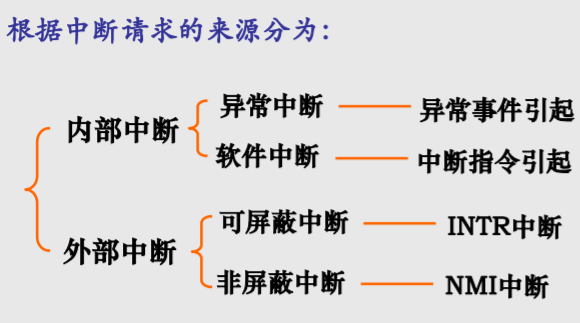

(3)中断类型

第十章 可编程数字接口电路

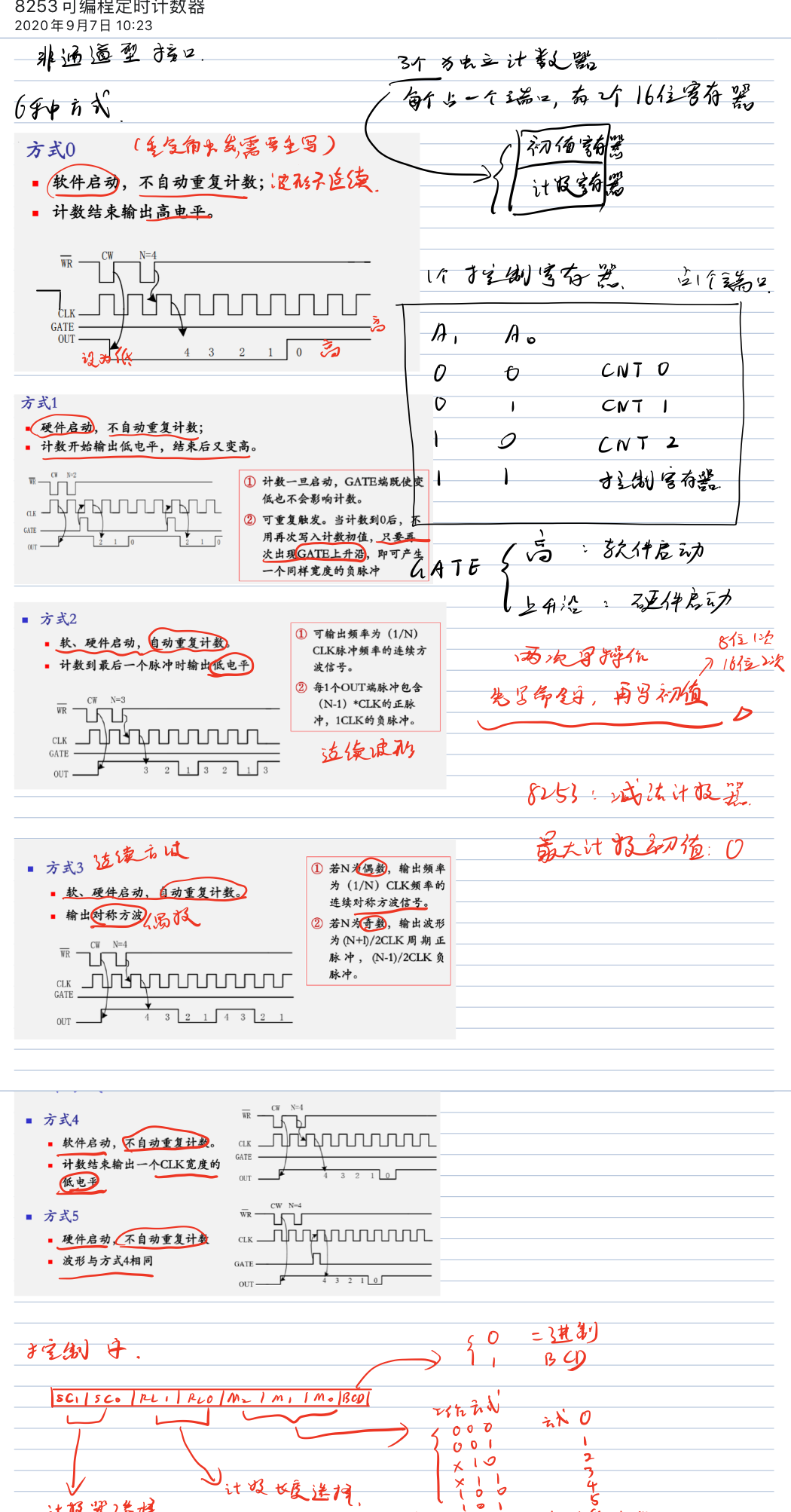

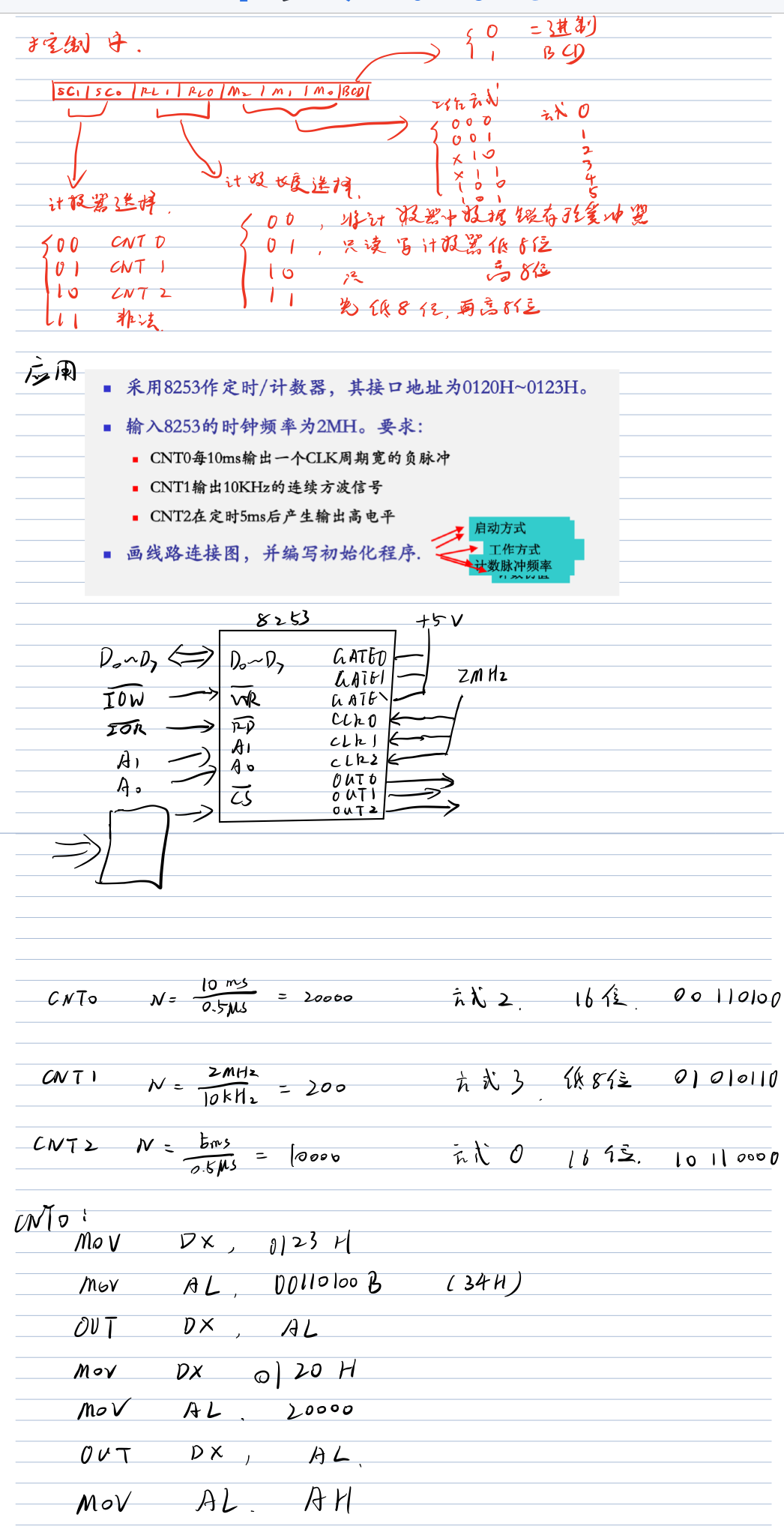

可编程定时计数器8253

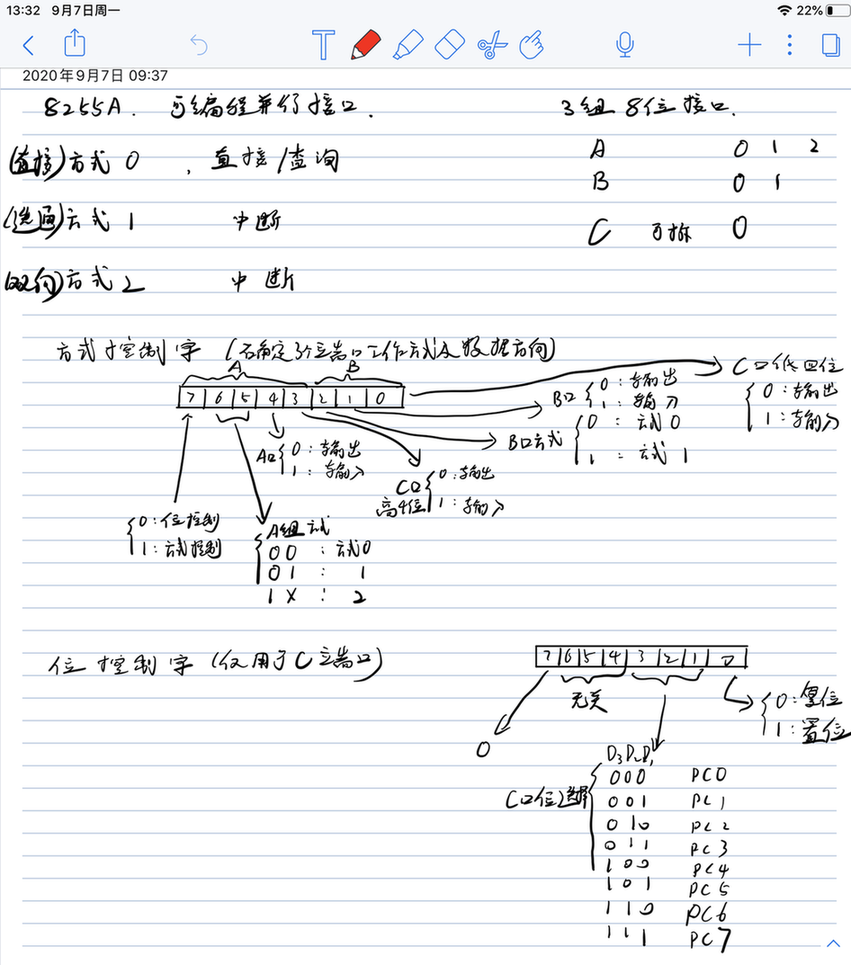

可编程并行接口8255

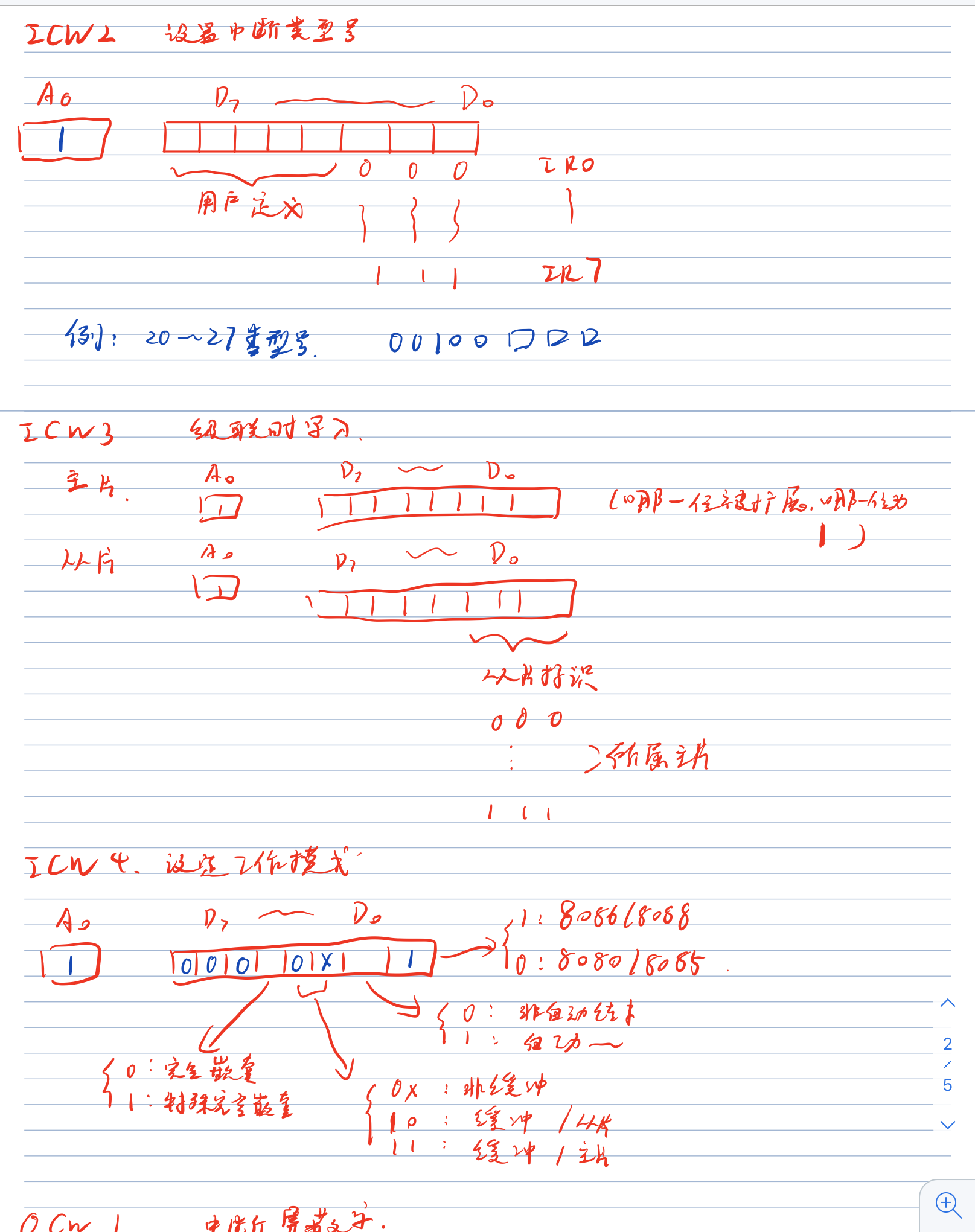

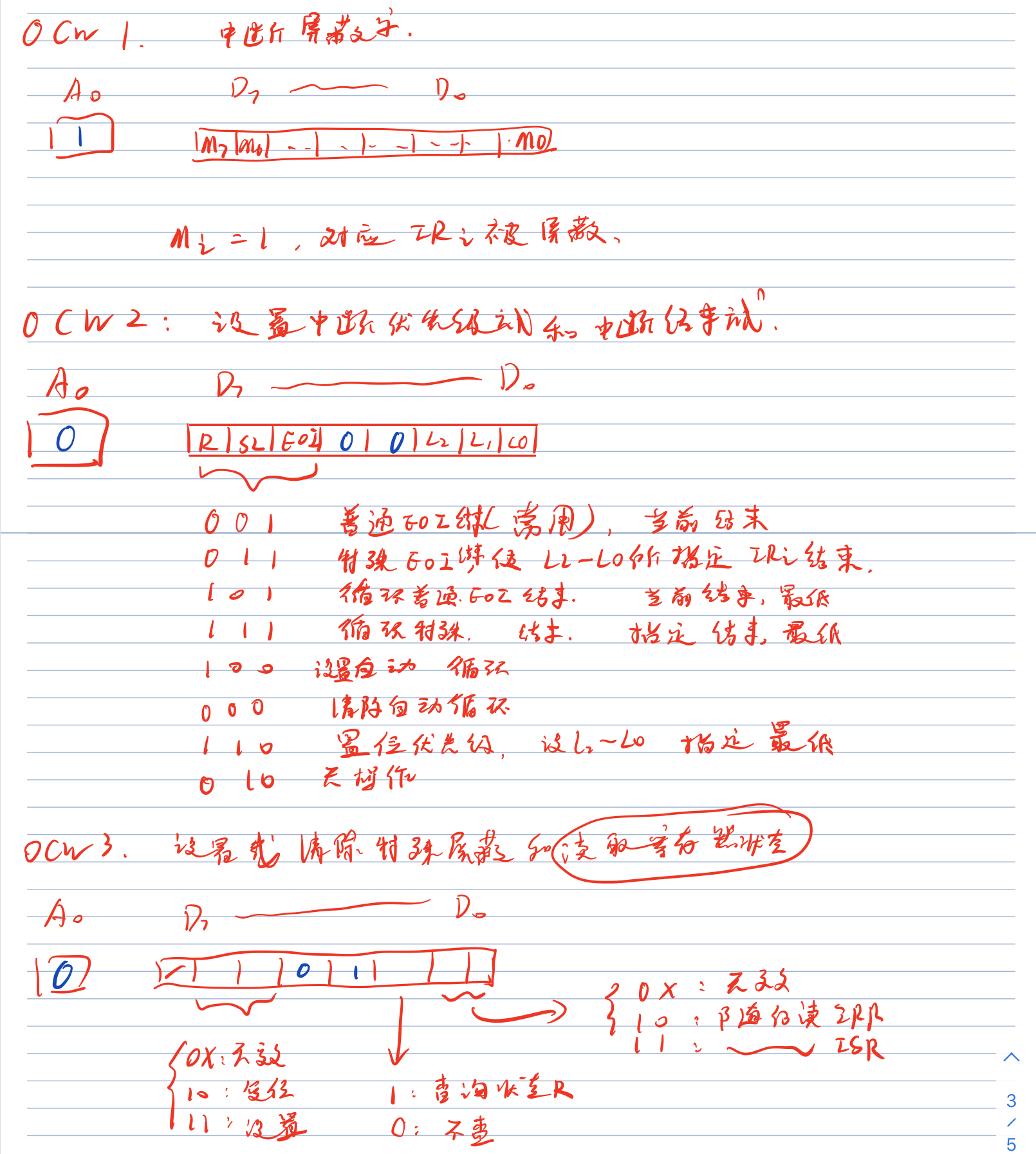

可编程中断控制器8259

第十一章 模拟接口电路

模拟量的输入输出

D: (Digital) 数字量

A: (Analog) 模拟量

采样和量化

D/A转换器和A/D转换器

- 主要参数

(1)分辨率

输入的二进制数每+1/-1个最低有效位LSB,使输出变化的程度 , 1LSB = 1/(2^n-1)

[n:D/A转换器的字长]

(2)转换时间

(3)精度

(4)线性度 - D/A转换器与微处理器的接口方法

(1)接口任务:解决数据锁存,缓冲问题

(2)特点:控制信号,无专门数据传送间隔时间,调节数据宽度

(3)接口电路结构:通用并行接口或直连

(4)D/A:数字量转换为模拟量

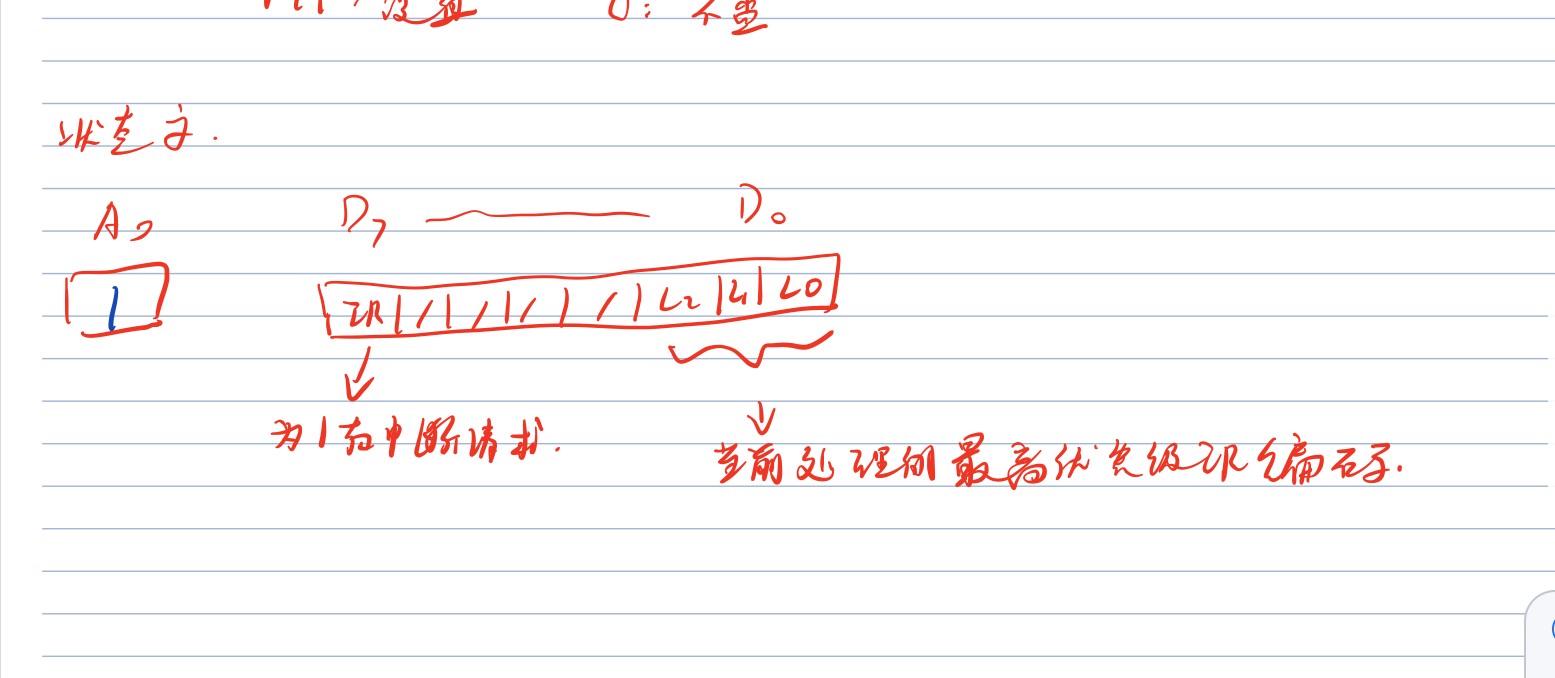

D/A转换器(DAC0832)NS

- 三种工作方式:直通方式,单缓冲方式,双缓冲方式

- 8位寄存器,T型电阻网络,电流型输出,不可编程

- 主要引脚功能:D7-D0,ILE,CS,WR1,WR2,XFER(低电平有效)

- 内部结构:

(1)8位输入寄存器

(2)8位DAC寄存器

(3)8位D/A转换器

A/D转换器(ADC0809)

1.特点

- 8通道(8路)输入

- 8位字长

- 逐位逼近型

- 转换时间100us

- 内置三态输出缓冲器

2.主要引脚功能 - D7-D0:输出数据线,三态

- IN0-IN7:8通道模拟输入

- ADDC,ADDB,ADDA通道地址选择

- Start:启动变换

- ALE:通道地址锁存

- EOC:转换结束状态输出

- OE:输出允许

- CLK:工作时钟

补充

- 控制信号

(1)M/IO=1,CPU对存储器操作,M/IO=0,CPU对I/O操作

(2)DT/R=1,CPU→【内存/(I/O)】,DT/R=0,外部→CPU

(3)8086,RD,WR低电平有效 - ADC0809

(1)EOC发出中断请求

(2)CPU查询EOC状态 - D/A和A/D

(1)主要参数:分辨率,转换时间,精度 - 数据传输方式(输入输出控制方式)

(1)程序控制方式

(1.1)无条件传送

(1.2)有条件传送(查询)

(2)中断控制方式

(3)DMA

(3.1)DMA传送方式:单元传送,块传送,请求传送

(3.2)DMAC,8237A

(3.3)DMA方式写,外设到存储器

(3.4)8237占用8个输入输出端口

(3.5)DMA控制方式中需要用到的一对联络信号是HLDA/HRQ - 串行接口

(1)串行接口中,并行数据和串行数据的转换通过移位寄存器实现

(2)RS-232是串行通信标准 - 片选控制方式,全译码,部分译码,线译码

- I/O接口有独立编址和统一编址方式

- 复位后段寄存器的初值为:CS=FFFFH,DS=0000H,SS=0000H,ES=0000H,其他寄存器的初值都是0,特别是CS=FFFFH,IP=0000H,因此复位后CPU从FFFF0H开始执行程序

- 奇地址存储体和系统数据总线高8位相连,用BHE=0作为选通信号;偶地址存储体和系统数据总线低8位相连,用A0=0作为连通信号

- 对准字,从偶地址开始存放字数据的存放方式(传一次,A0和BHE都有效),非对准字,从奇地址开始存放字数据的存放方式(传两次,先奇BHE后偶A0)

- 寻址隐含约定:

(1)直接寻址,DS

(2)寄存器寻址:DS←BX/SI/DI;SS←BP

(3)基址变址寻址:DS←BX+SI/DI ; SS:BP+SI/DI

(4)堆栈:SS←SP

(5)取指令:CS←IP

最后

以上就是动听香水最近收集整理的关于大学课程 | 《微机原理与接口技术》知识点总结第一章 微型计算机基础概论第二章 微处理器与总线第三章 指令系统概述第四章 算术运算,逻辑运算与移位操作指令第五章 串操作指令第六章 程序与处理器控制指令第七章 汇编语言第八章 半导体存储器第九章 输入输出与中断技术第十章 可编程数字接口电路第十一章 模拟接口电路补充的全部内容,更多相关大学课程内容请搜索靠谱客的其他文章。

发表评论 取消回复