DSP与CEVA芯片

dsp芯片的特点

通常来说dsp芯片的程序和数据是分开存放的,内部存在快速的RAM,可以通过数据总线同时访问指令和数据。Dsp芯片支持无开销循环及跳转的硬件,能够并行执行多个操作,像取指、译码等,可以重复操作,具有稳定性好、精度高、大规模集成性等多个优点。不过功率消耗大,成本高。

dsp芯片和通用微处理器有什么区别

1、通用微处理器有被让人们称为单片机,将计算机系统集成到了一块芯片中。通用微处理器是以某中微处理内核为核心,拥有A/D、Flash RAM等各种功能和外设。一个单片机能够延生多种产品,最大限度与应用需求相匹配,减小了功耗和成本。

2、dsp芯片是为了快速处理数字信号,在结构上和数据、地址总线是分开的,没有像微处理器一样将计算机系统集成在一起,主要处理带有智能逻辑的消费类产品,生物信息识别终端, ADSL 接入、虚拟现实显示等,运算量大,功率消耗也比较大。与单片机相比,通用功能会相对比较弱一些。

CEVA DSP 架构

• 第四代 CEVA-XC架构可提供1,600 GOPS动态多线程和流水线,并且在7nm下实现1.8GHz主频

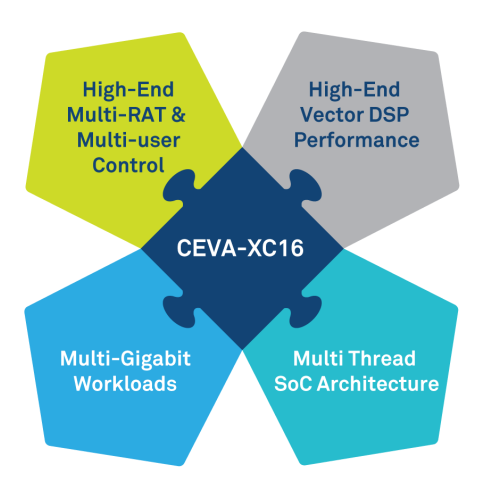

• CEVA-XC16 DSP是首个基于第四代 CEVA-XC架构的处理器,瞄准5G智能无线电接入网络(RAN)和企业接入点应用,将峰值性能提高2.5倍

CEVA,人工智能处理器 IP 的授权许可厂商 (纳斯达克股票交易所代码:CEVA) ,推出DSP架构Gen4 CEVA-XC。架构瞄准5G端点和无线接入网络(RAN),企业接入点,以及其它数千兆数据处理,且低延迟应用,并行处理工作负载的性能。

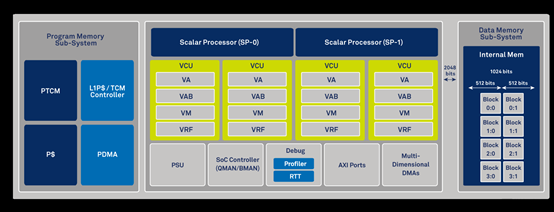

第四代CEVA-XC统一了标量和矢量运算处理,可实现两次8路VLIW和前所未有的14,000位数据级并行。采用流水线架构,在7nm工艺节点,可实现1.8 GHz主频,使用了物理设计架构,实现综合的设计流程,以及创新的多线程设计,允许处理器动态地配置为宽SIMD机,或划分为较小的同时SIMD线程。第四代CEVA-XC架构,使用2048位内存带宽的新颖内存子系统,具有紧耦合的内存,以支持并发多线程和内存接入。

第四代CEVA-XC架构是CEVA,进行DSP并行处理的创新。这款架构具有动态可重配置的多线程和高速设计,用于控制和运算处理的全面功能,为用于5G基础架构和端点的ASIC,ASSP器件奠定了基础。

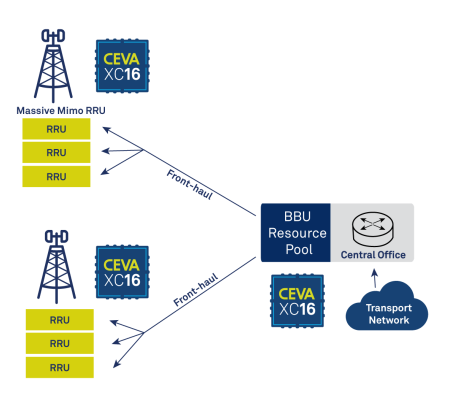

基于第四代CEVA-XC架构的处理器是多核CEVA-XC16,运行DSP内核,瞄准5G RAN体系结构部署,包括开放式RAN(O-RAN)、基带单元(BBU)聚合以及Wi-Fi和5G企业接入点。CEVA-XC16还适用于与基站运作信号处理和AI工作负载。

CEVA-XC16在设计时考虑了3GPP规范,基于CEVA无线基础架构供应商合作开发,蜂窝基础架构ASIC经验。CEVA前代CEVA-XC4500和CEVA-XC12 DSP,现在助力4G和5G蜂窝网络,一家无线设备供应商已将新型CEVA-XC16用于其下一代5G ASIC设计。

CEVA-XC16提供每秒1600 GOPS并行性能,重新配置为两个单独的并行线程,两者可以同时运行,共享具有高速一致性缓存的L1数据存储器,提升PHY控制处理的延迟和性能效率,无需使用额外的CPU。相比在拥挤区域连接大量用户的单核/单线程架构,将每平方毫米的性能提高了50%。这对于定制5G基站芯片普遍采用的大型内核集群,可节省35%的芯片面积。

CEVA-XC16的其它主要功能包括:

• 最新一代双CEVA-BX标量处理器单元——支持真正的并发多线程运行

• 可将矢量单位资源动态分配给处理线程——利用矢量单位资源,并减少复杂流程的开销

• 先进的标量控制架构和工具,通过使用最新的动态分支预测和循环优化,以及基于LLVM的编译器,相比前代产品,可将代码大小减少30%

• 用于FFT和FIR的全新指令集架构——可将性能提高两倍

• 增强的多用户功能,支持大带宽分配给单一用户,支持精细的用户分配

• 上代CEVA-XC4500和CEVA-XC12 DSP的软件可简单迁移

5G是一项具有跨越消费者、工业、电信和AI领域的多种增长矢量的技术,应对这些零散而复杂的用例需要全新的处理器,而第四代CEVA-XC架构采用了这一全新方法,设计实现了DSP内核性能。CEVA-XC16 DSP是这项成就的例证,为希望从不断增长的5G 资产开支,Open RAN网络架构中获益的OEM厂商,半导体供应商大幅降低了进入门槛。

关于CEVA公司

CEVA是无线连接和智能传感技术的领先授权公司。提供数字信号处理器、AI处理器、无线平台以及用于传感器融合、图像增强、计算机视觉、语音输入和人工智能的配套软件,所有这些都是支持智能互联世界的关键技术。与全球的半导体公司和OEM合作,为移动、消费、汽车、机器人、工业和物联网的各种终端市场,创建高效和智能的连接设备。超低功耗IP包括面向移动设备和基础设施中的5G基带处理,基于DSP的全面平台,适用于任意相机设备的高级成像和计算机视觉,适用于多个物联网市场的音频/话音/语音以及超低功耗Always-On/感应应用。对于传感器融合,Hillcrest Labs传感器处理技术为AR / VR、机器人、遥控器和IoT提供了广泛的传感器融合软件和IMU解决方案。对于人工智能,提供一系列AI处理器,能够在设备上处理完整的神经网络工作负载。对于无线物联网,提供蓝牙IP(低功耗和双模)、Wi-Fi 4/5/6 (802.11n / ac / ax)和NB-IoT。

深度学习芯片之争:CPU、GPU、DSP、NPU

CPU、GPU:用轿车运货

Intel的众核芯片也在一定程度上吸取了GPU的优势,性能不俗,但短时间看还是GPU有优势。不过,无论是针对人工智能的众核芯片还是定制版的GPU,本质上都不是专用处理器。

其实,Intel和英伟达是在使用现有的比较成熟的技术去满足深度学习的需求,众核芯片和定制版GPU在本质上来说依旧是CPU和GPU,并非专门针对深度学习的专业芯片。用众核芯片和GPU跑深度学习,就类似于用轿车去拉货,受轿车自身特点的限制,货物运输能力与真正大马力、高负载的货车有一定差距。同理,即便是因为技术相对更加成熟,Intel和英伟达的芯片在集成度和制造工艺上具有优势,但由于CPU、GPU并非针对深度学习的专业芯片,相对于专业芯片,其运行效率必然受到一定影响。

DSP:和真正神经网络芯片有差距

共包含四个NPU核,每个NPU核包含4个内核,每个内核有两个流处理器(Dataflow Processor),每个流处理器具有8个长位宽或16位宽的SIMD运算单元。每个NPU核的峰值性能为38Gops(16位定点)或者76Gops(8位定点)。除了多核流处理器本身用于完成卷积运算外,集成了一个超长指令字(VLIW)处理器用于完成神经网络中的超越函数等运算。另有256KB的L2Cache以及DMA模块用于大块数据的搬移。

从其低位宽的定点运算器推断,仅可支持神经网络正向运算,无法支持神经网络的训练。从片上存储结构看,基于传统的片上缓存(Cache),而非像最近流行的神经芯片或FPGA方案一样使用便签式存储。因此,在技术上看星光智能一号是典型的“旧瓶装新酒”方案,将传统的面向数字信号处理的DSP处理器架构用于处理神经网络,主要在运算器方面作了相应修改,例如低位宽和超越函数,而并非是“狭义的”神经网络专用处理器,如IBM的“真北”芯片。

因此,DSP,而非NPU,能够适用于卷积神经网路(CNN),而对循环神经网络(RNN)和长短期记忆网络(LSTM)等处理语音和自然语言的网络有可能就无能为力了。

用传统SIMD/DSP架构来适配神经网络的技术思想在国际上已有不少先例,甚至有成熟的产品,例如CEVA公司的XM4处理器、Cadence公司的Tensilica Vision P5处理器、Synopsys公司的EV处理器等。

NPU

由于深度学习的基本操作是神经元和突触的处理,而传统的处理器指令集(包括x86和ARM等)是为了进行通用计算发展起来的,其基本操作为算术操作(加减乘除)和逻辑操作(与或非),往往需要数百甚至上千条指令才能完成一个神经元的处理,深度学习的处理效率不高。因此谷歌甚至需要使用上万个x86 CPU核运行7天来训练一个识别猫脸的深度学习神经网络。因此,传统的处理器(包括x86和ARM芯片等)用于深度学习的处理效率不高,这时就必须另辟蹊径——突破经典的冯·诺伊曼结构。

以中国的寒武纪为例,DianNaoYu指令直接面对大规模神经元和突触的处理,一条指令即可完成一组神经元的处理,并对神经元和突触数据在芯片上的传输提供了一系列专门的支持。

另外,神经网络中存储和处理是一体化的,都是通过突触权重来体现。 而冯·诺伊曼结构中,存储和处理是分离的,分别由存储器和运算器来实现,二者之间存在巨大的差异。当用现有的基于冯·诺伊曼结构的经典计算机(如X86处理器和英伟达GPU)来跑神经网络应用时,就不可避免地受到存储和处理分离式结构的制约,因而影响效率。这也就是专门针对人工智能的专业芯片能够对传统芯片有一定先天优势的原因之一。

用数字来说话,CPU、GPU与NPU相比,会有百倍以上的性能或能耗比差距——以寒武纪团队过去和Inria联合发表的DianNao论文为例——DianNao为单核处理器,主频为0.98GHz,峰值性能达每秒4520亿次神经网络基本运算,65nm工艺下功耗为0.485W,面积3.02平方毫米mm。

在若干代表性神经网络上的实验结果表明——

DianNao的平均性能超过主流CPU核的100倍,但是面积和功耗仅为1/10,效能提升可达三个数量级; DianNao的平均性能与主流GPGPU相当,但面积和功耗仅为主流GPGPU百分之一量级。

就现阶段而言,传统芯片厂商(如CPU、GPU和DSP)对于深度学习市场非常重视,因此利用他们巨大体量和市场推广、销售能力,大力推广用这些传统芯片来进行深度学习处理,其本质上也是对现有的技术进行微调,用传统SIMD架构来适配神经网络。

然而,由于传统CPU、GPU和DSP本质上并非以硬件神经元和突触为基本处理单元,相对于NPU在深度学习方面天生会有一定劣势,在芯片集成度和制造工艺水平相当的情况下,其表现必然逊色于NPU。

最后

以上就是愉快水杯最近收集整理的关于DSP与CEVA芯片的全部内容,更多相关DSP与CEVA芯片内容请搜索靠谱客的其他文章。

发表评论 取消回复