本文谨用于记录调试SPI LCD 时遇到的问题,中间有很多基础概念搬运自其他网页,部分内容结合实际项目进行对比验证,如有错误,请沟通交流。

1. SPI 协议

SPI是英语Serial Peripheral interface的缩写,顾名思义就是串行外围设备接口。是Motorola首先在其MC68HCXX系列处理器上定义的。

SPI接口主要应用在 EEPROM,FLASH,实时时钟,AD转换器,还有数字信号处理器和数字信号解码器之间,是一种高速的,全双工,同步的通信总线,并且在芯片的管脚上只占用四根线,节约了芯片的管脚,同时为PCB的布局上节省空间,提供方便。

1.1 特点(默认指4线标准SPI)

同步

全双工

通信简单

数据传输速率快

1.2 缺点

没有指定的流控制,没有应答机制确认是否接收到数据,所以跟IIC总线协议比较在数据可靠性上有一定的缺陷。

1.3 控制方式

采用主-从模式(Master-Slave) 的控制方式SPI 规定了两个 SPI 设备之间通信必须由主设备 (Master) 来控制从设备 (Slave)。

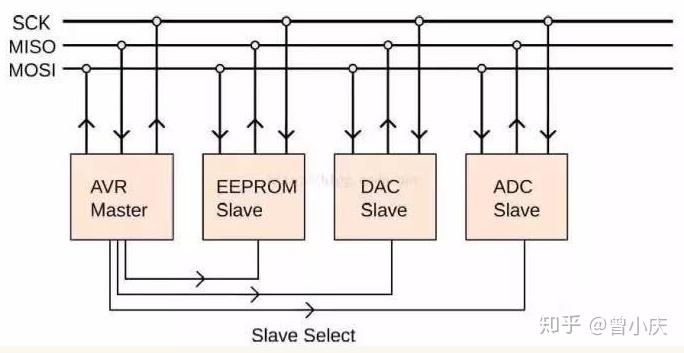

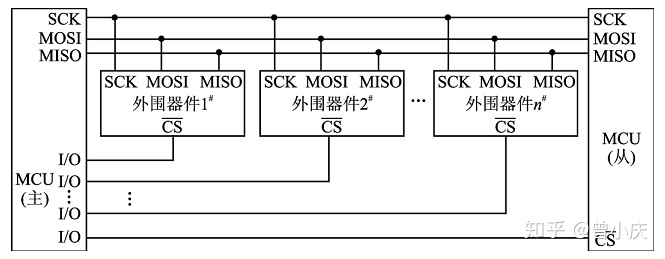

一个 Master 设备可以通过提供 Clock 以及对 Slave 设备进行片选 (Slave Select) 来控制多个 Slave 设备,SPI 协议还规定 Slave 设备的 Clock 由 Master 设备通过 SCK 管脚提供给 Slave 设备, Slave 设备本身不能产生或控制 Clock,没有 Clock 则 Slave 设备不能正常工作。

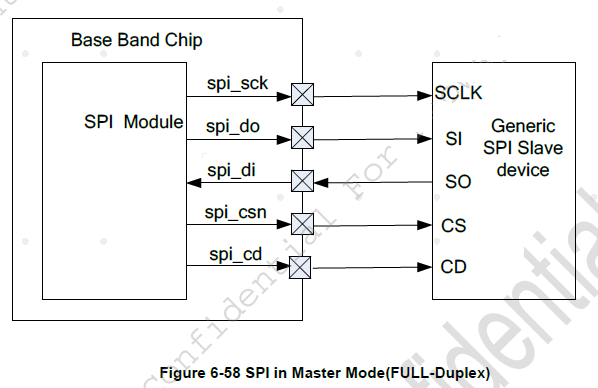

1.3.1 主机模式

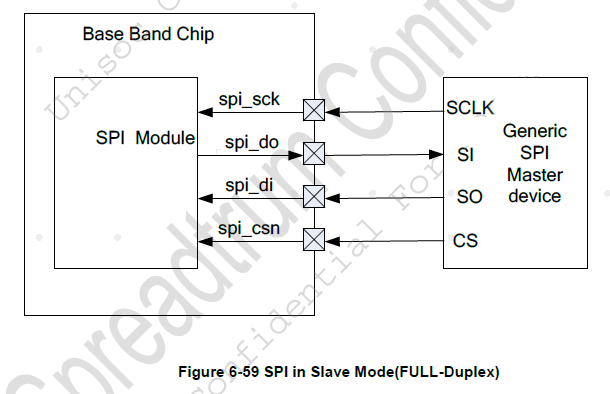

1.3.2 从机模式

1.4 传输数据

采用同步方式(Synchronous)传输数据。Master 设备会根据将要交换的数据来产生相应的时钟脉冲(Clock Pulse),时钟脉冲组成了时钟信号(Clock Signal) ,时钟信号通过时钟极性 (CPOL) 和 时钟相位 (CPHA) 控制着两个 SPI 设备间何时数据交换以及何时对接收到的数据进行采样,来保证数据在两个设备之间是同步传输的。

1.5 SPI引脚

SDI(数据输入)、SDO(数据输出)、SCK(时钟)、CS/SS(片选)、(RS、CD、D/CX)-(数据命令指示脚)

- SDO/MOSI – 主设备数据输出,从设备数据输入;

- SDI/MISO – 主设备数据输入,从设备数据输出;

- SCK – 时钟信号,由主设备产生;

- CS/SS – 从设备使能信号,由主设备控制。当有多个从设备的时候,因为每个从设备上都有一个片选引脚接入到主设备机中,当我们的主设备和某个从设备通信时将需要将从设备对应的片选引脚电平拉低或者是拉高。

- DCX、RS、CD – 数据、命令切换脚,由主设备控制。当向从机发送信号的时候,用此引脚标识发送的是数据还是命令。

1.6 极性和相位

SPI的极性Polarity和相位Phase,最常见的写法是CPOL和CPHA。

CPOL配置SPI总线的极性,CPHA配置SPI总线的相位。

CKPOL (Clock Polarity) = CPOL = POL = Polarity = (时钟)极性。

CKPHA (Clock Phase) = CPHA = PHA = Phase = (时钟)相位。

SCK=SCLK=SPI的时钟。

Edge=边沿,即时钟电平变化的时刻,即上升沿(rising edge)或者下降沿(falling edge)对于一个时钟周期内,有两个edge,分别称为:

Leading edge=前一个边沿=第一个边沿,对于开始电压是1,那么就是1变成0的时候,对于开始电压是0,那么就是0变成1的时候;

Trailing edge=后一个边沿=第二个边沿,对于开始电压是1,那么就是0变成1的时候(即在第一次1变成0之后,才可能有后面的0变成1),对于开始电压是0,那么就是1变成0的时候;

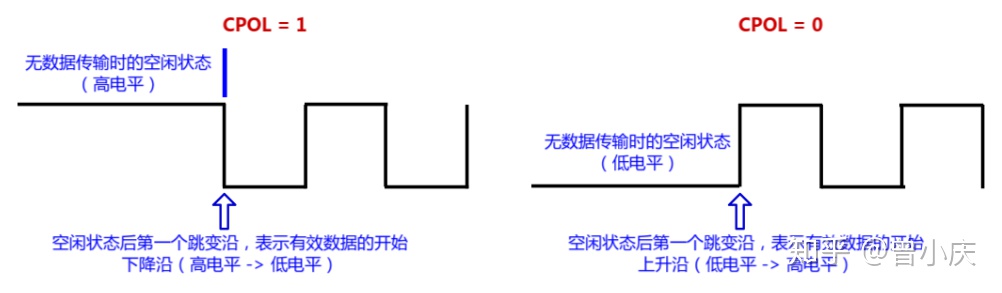

1.7 极性

极性,会直接影响SPI总线空闲时的时钟信号是高电平还是低电平。

CPOL = 1:表示空闲时是高电平;

CPOL = 0:表示空闲时是低电平;

由于数据传输往往是从跳变沿开始的,也就表示开始传输数据的时候,是下降沿还是上升沿。如下图:

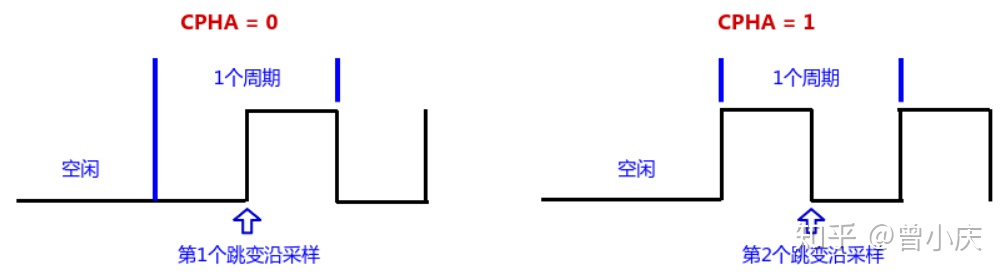

1.8 相位

一个时钟周期会有2个跳变沿。而相位,直接决定SPI总线从那个跳变沿开始采样数据。

CPHA = 0:表示从第一个跳变沿开始采样;

CPHA = 1:表示从第二个跳变沿开始采样。

1.9 四种模式

由于有不同的极性和相位组合,因此标准SPI以后4种不同的模式。

时钟极性CPOL是用来配置SCLK的电平出于哪种状态时是空闲态或者有效态,时钟相位CPHA

是用来配置数据采样是在第几个边沿:

CPOL=0,表示当SCLK=0时处于空闲态,所以有效状态就是SCLK处于高电平时。

CPOL=1,表示当SCLK=1时处于空闲态,所以有效状态就是SCLK处于低电平时。

CPHA=0,表示数据采样是在第1个边沿,数据发送在第2个边沿。

CPHA=1,表示数据采样是在第2个边沿,数据发送在第1个边沿。

例如:

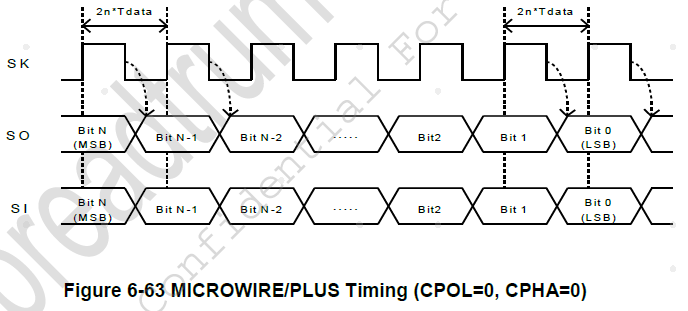

CPOL=0,CPHA=0:此时空闲态时,SCLK处于低电平,数据采样是在第1个边沿,也就是

SCLK由低电平到高电平的跳变,所以数据采样是在上升沿,数据发送是在下降沿。

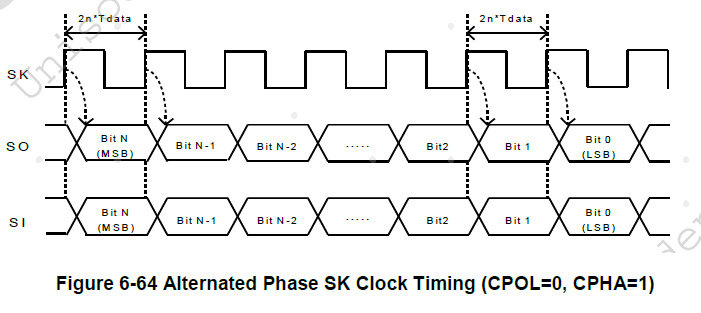

CPOL=0,CPHA=1:此时空闲态时,SCLK处于低电平,数据发送是在第1个边沿,也就是

SCLK由低电平到高电平的跳变,所以数据采样是在下降沿,数据发送是在上升沿。

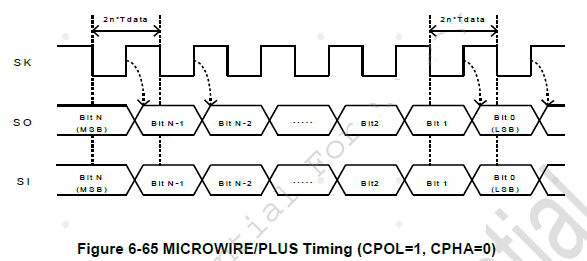

CPOL=1,CPHA=0:此时空闲态时,SCLK处于高电平,数据采集是在第1个边沿,也就是

SCLK由高电平到低电平的跳变,所以数据采集是在下降沿,数据发送是在上升沿。

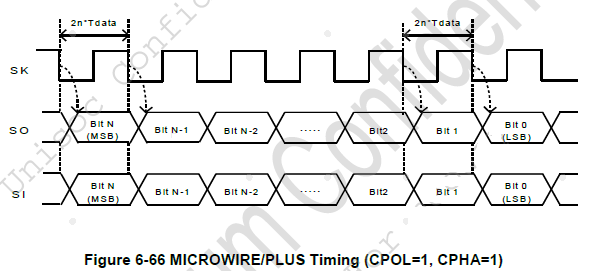

CPOL=1,CPHA=1:此时空闲态时,SCLK处于高电平,数据发送是在第1个边沿,也就是

SCLK由高电平到低电平的跳变,所以数据采集是在上升沿,数据发送是在下降沿。

Note:没有专门的起始、结束、应答信号,需要注意的是:我们的主设备能够控制时钟,因为SPI通信并不像UART或者IIC通信那样有专门的通信周期,有专门的通信起始信号,有专门的通信结束信号;所以SPI协议能够通过控制时钟信号线,当没有数据交流的时候我们的时钟线要么是保持高电平要么是保持低电平。

2 变种SPI

SPI总线是一种事实标准,并没有被任何的国际委员会承认。在实际的应用中,会根据实际需要去修改扩展。

如半双工:分时,用一根数据线进行收和发;

只发不收:去掉MISO,保留MOSI;

只收不发:去掉MOSI,保留MISO;

去掉RS/DCX/CD数据信号选择线:在传输数据的时候,多加一位bit8用来指示这条参数是命令还是数据。(这就是9data的来源);这种用于没有DCX的3线SPI,3线SPI也可以称为3线9data SPI。(有的3线是指去掉了一个数据线,这种不是严格意义上的3线,暂不讨论)。

在3线和4线的SPI类型上,每种又分为I型和II型。

所以至少有4种类型的变种SPI:

3线I型 – SCL、CS、SDA - 3线1data 9bit SPI – 半双工,只有一根双向的数据线

3线II型 –SCL、CS、SDI、SDO - 3线2data 9bit SPI – 全双工,有独立的MOSI、MISO

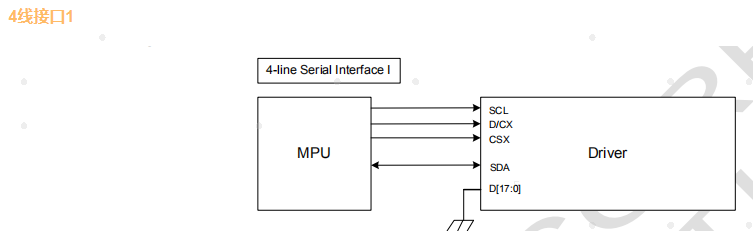

4线I型 – SCL、DCX、CS、SDA - 4线1data 8bit SPI – 半双工,只有一根双向的数据线

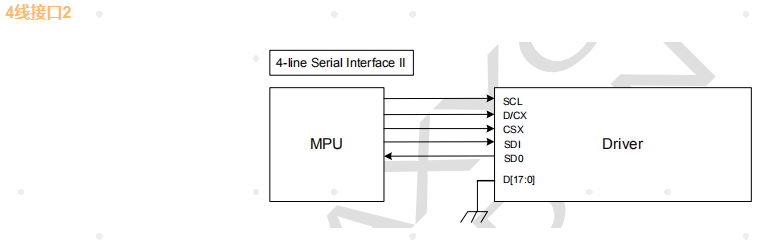

4线II型 – SCL、DCX、CS、SDI、SDO - 4线2data 8bit SPI –全双工,有独立的MOSI、MISO

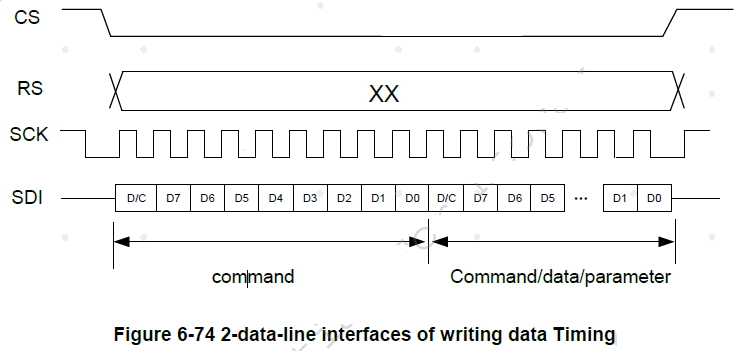

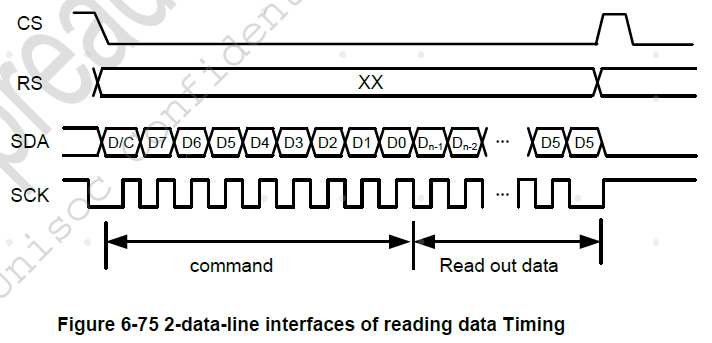

2.1 四线接口I型

2.2 四线接口II型

2.3 三线接口I型

略

2.4 三线接口II型

3 各模式下的信号定义

3线9bit I型 接口信号:SCL/CSX/SDA

3线9bit II型接口信号:SCL/CSX /SDO/SDI

4线8bit I型接口信号:SCL/CSX /DCX/SDA

4线8bit II型接口信号:SCL/CSX/DCX/SDO/SDI

3线9bit 2 data Lane 接口信号:SCL/CSX/D0/D1 //D1 由 DCX(RS)PIN 转换

三线、四线:三线都没有DCX,用发送信号时的bit8来表示数据和命令,因此三线都是9bit的。

I型、II型:I型只有一条双向的数据线,半双工模式。II型有两条单向的数据线,全双工模式。

4 SPI和LCD

在大多数的SPI接口的LCD上,不必使用标准SPI,常常缩减为3线。

对LCD的控制不需要反馈,只发不收,且为了节约pin连同DCX一并省略,用bit8来表示data/cmd。

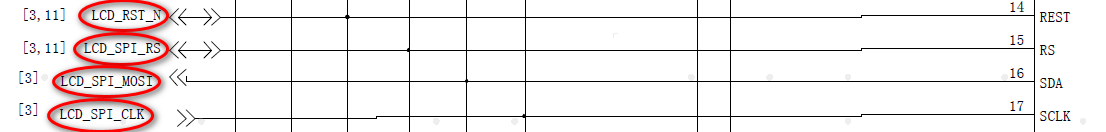

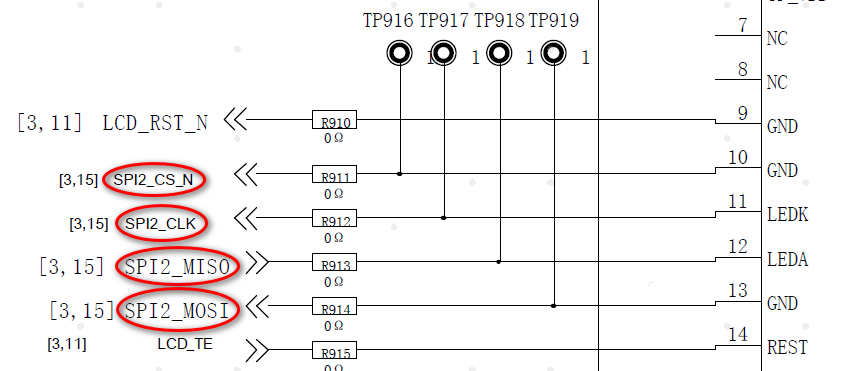

如SC9820E的LCD设计:

四线I型(1data 8bits):

三线II型(2data 9bits)兼容设计:

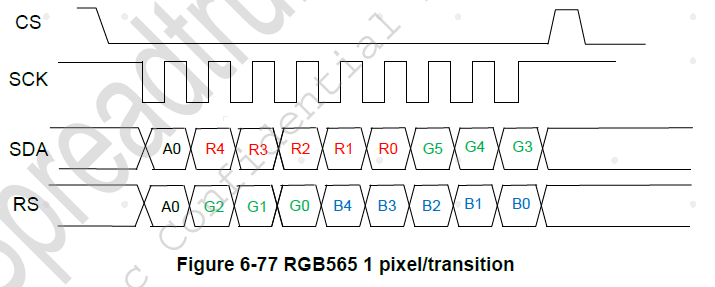

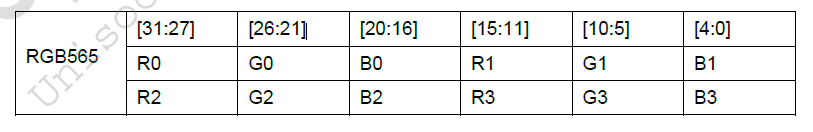

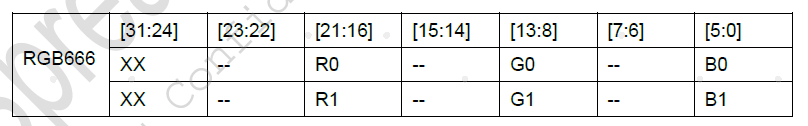

4.1 RGB565 字节对齐

参考文献:

https://zhuanlan.zhihu.com/p/150121520

https://blog.csdn.net/q1075355798/article/details/108507904

SL8521E_Device_Specification_V1.0.pdf

清风至,白露生~

最后

以上就是傲娇战斗机最近收集整理的关于SPI - 相关类型及其扩展1. SPI 协议2 变种SPI3 各模式下的信号定义4 SPI和LCD4.1 RGB565 字节对齐参考文献:清风至,白露生~的全部内容,更多相关SPI内容请搜索靠谱客的其他文章。

发表评论 取消回复