我是靠谱客的博主 缥缈镜子,这篇文章主要介绍AHB-SRAMC网课设计与验证-1课程内容backgroudfeaturesspecarchitectureAHB operation timing平台编写,现在分享给大家,希望可以做个参考。

文章目录

- 课程内容

- backgroud

- features

- spec

- architecture

- AHB operation timing

- 一个简单的测试案例建模

- 平台编写

课程内容

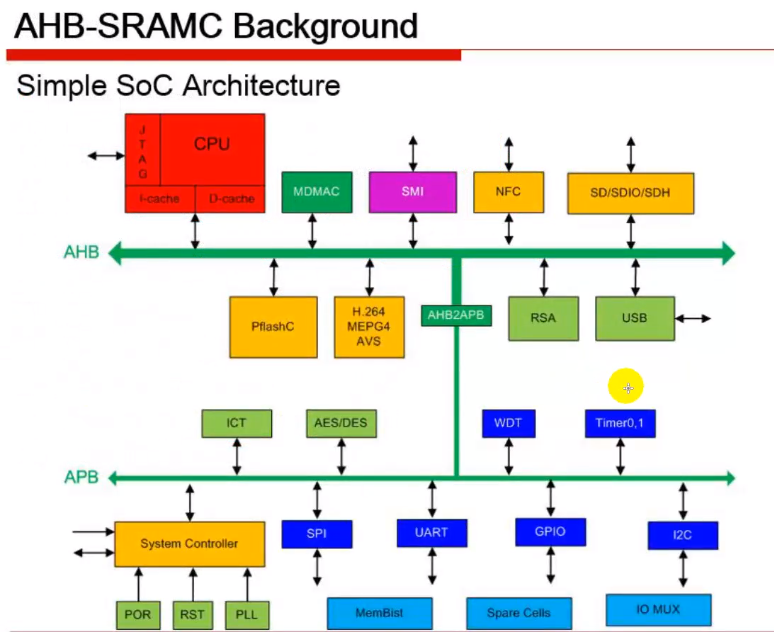

backgroud

- 在一个SOC系统里面,SRAMC是很常见的一部分(图中SMI,system memery)

- 作用是跑程序,数据的数据处理器

features

- AMBA 2.0 AHB spec;

- SRAM seoc

- 系统需求:

32/64/128/256空间;

支持8/16/32位位宽读写操作;

单周期读写(一个周期出现读写两种操作,实际上是pipeline,两个周期完成一个读写,一个周期发地址,另一个周期发数据);

低功耗设计;

实质上这是一个控制器,memory compiler(MC)可以自动生成RTL代码

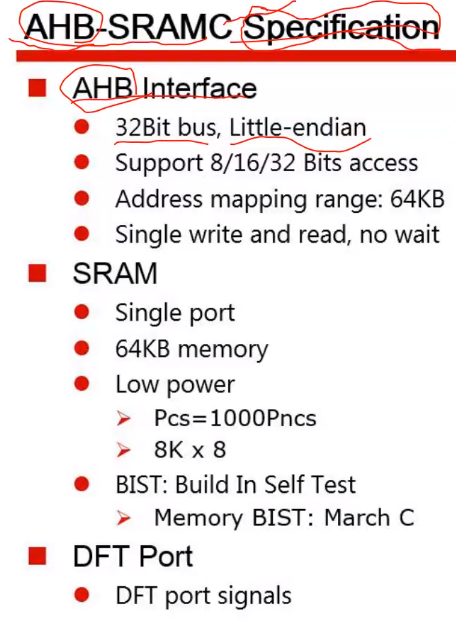

spec

- cs:chip select;

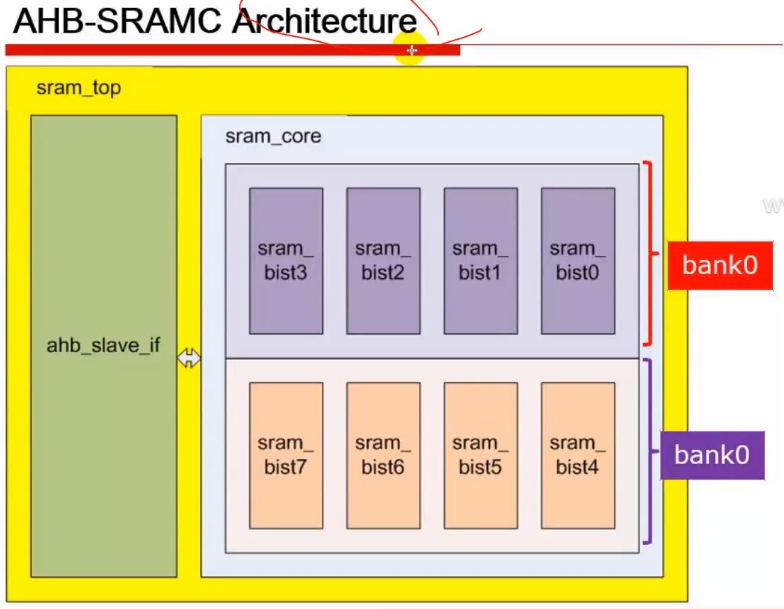

architecture

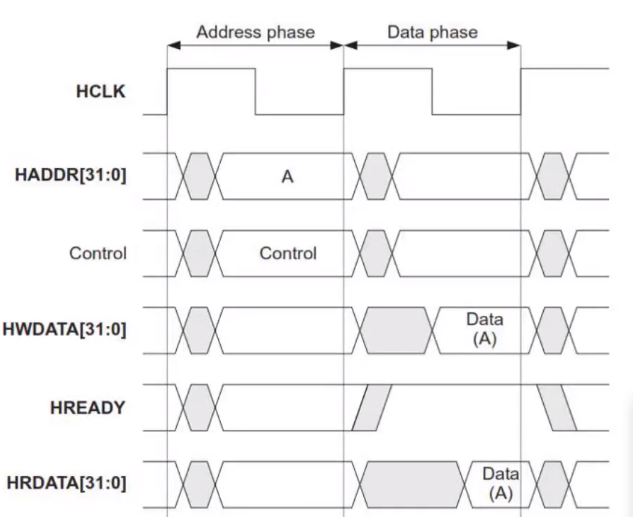

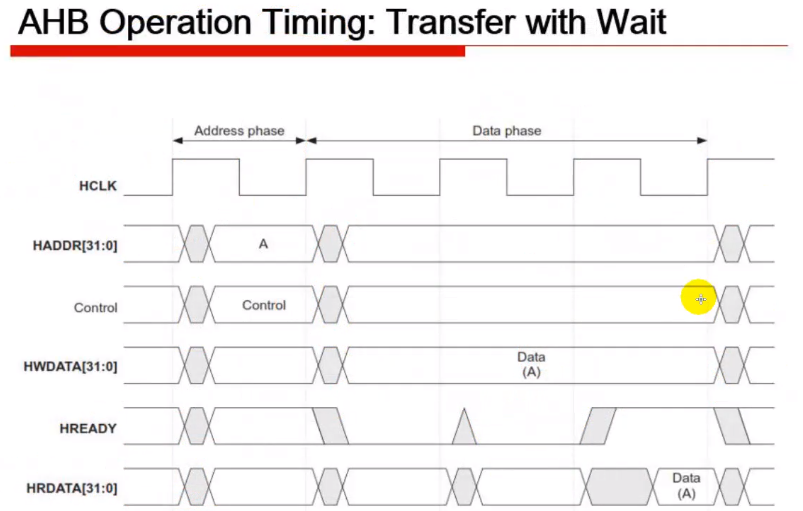

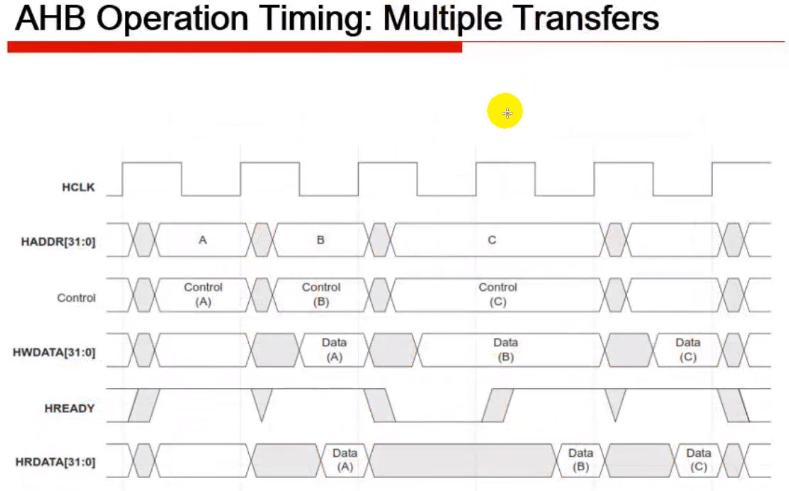

AHB operation timing

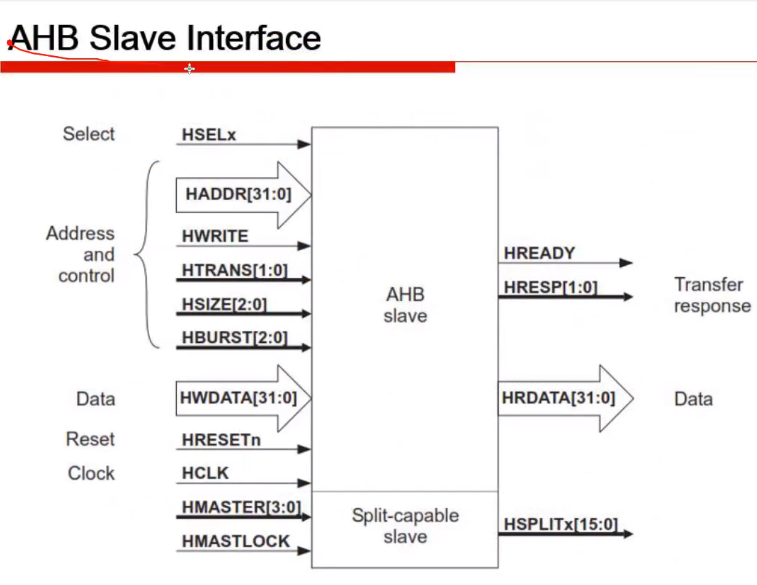

- 地址与数据是相邻的两拍;

- hready包含两个信号:

hready_in与hready_out

- 单周期读写不允许有wait,wait存在表示hready持续拉低,读数据持续无效,使得写数据与读数据相隔数个周期;

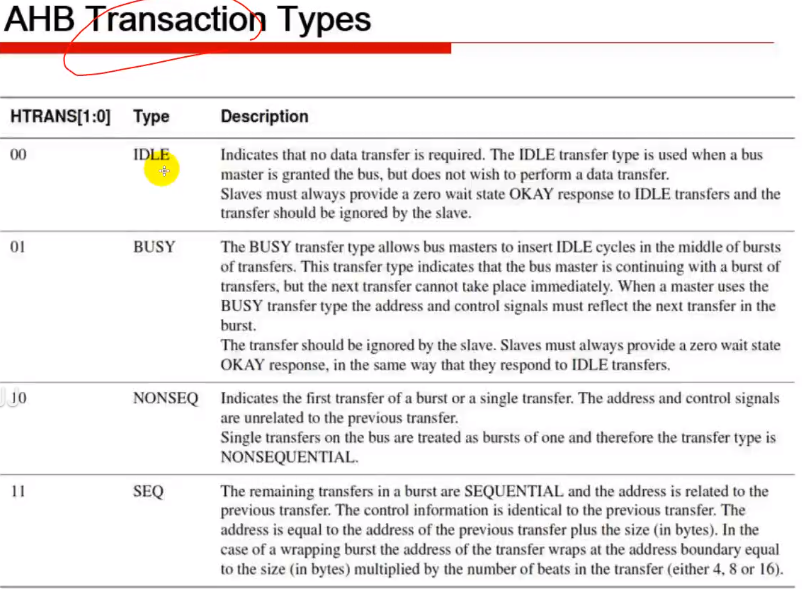

- busy是master发出的,表示总线暂时没有空间进行传输;

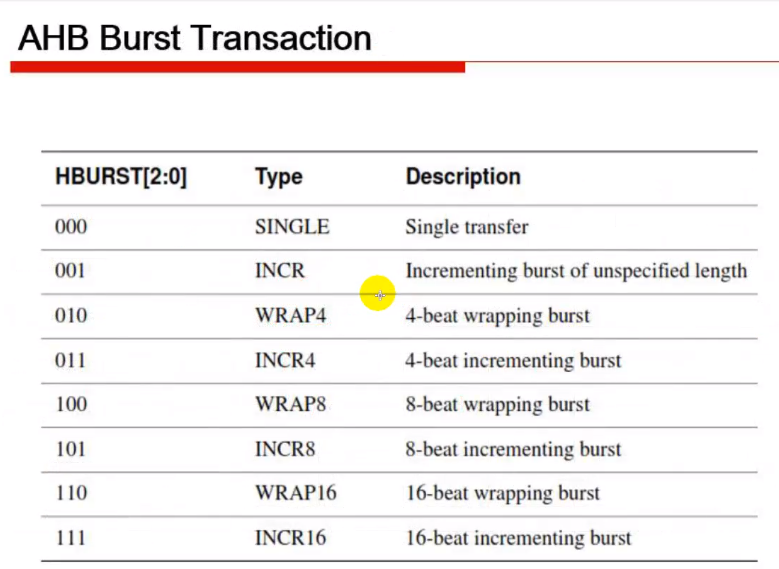

- AHB的burst不是真正的burst,AXI才是;

- 这是因为master会计算每一步的地址;

- beat,拍,一打数据;

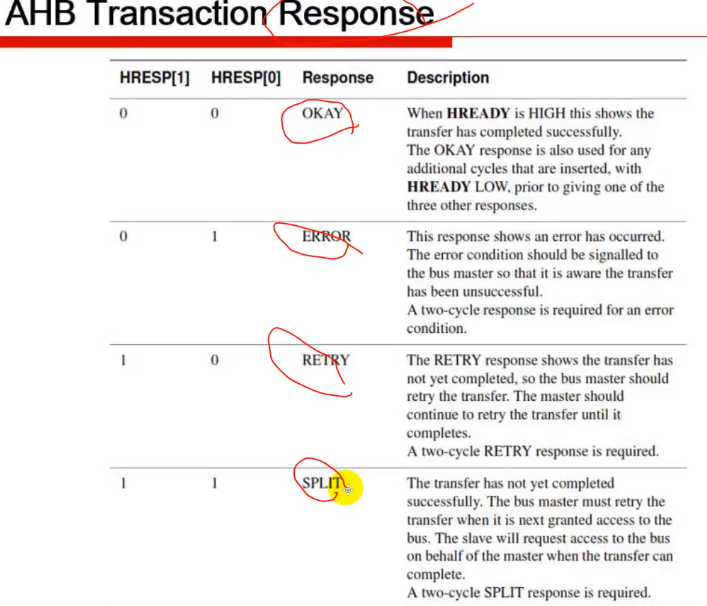

- 只有okey可以单周期实现,error、split,retry需要扩展位实现;

- split一般很少实现

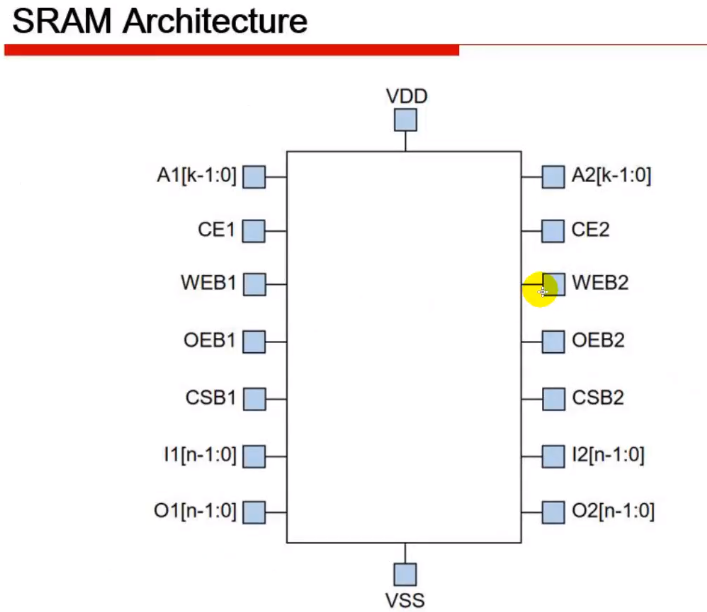

- 上面是一个双端口的,只看一边就可;

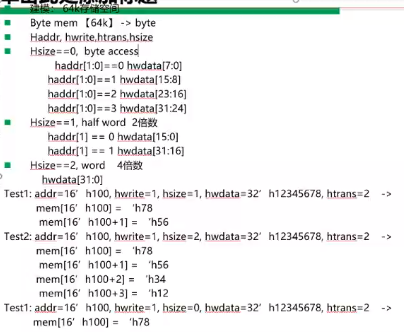

一个简单的测试案例建模

原则:写,存数据;读比数据;

byte写,地址随便;

half word 写,地址是2的倍数;

word 写,地址是4的倍数;

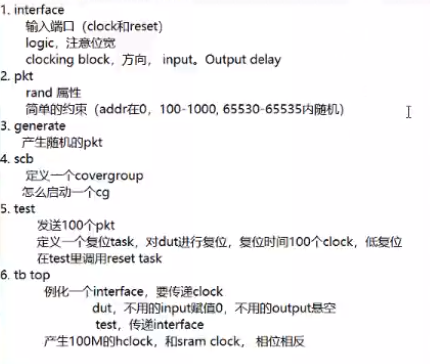

平台编写

注意

最后

以上就是缥缈镜子最近收集整理的关于AHB-SRAMC网课设计与验证-1课程内容backgroudfeaturesspecarchitectureAHB operation timing平台编写的全部内容,更多相关AHB-SRAMC网课设计与验证-1课程内容backgroudfeaturesspecarchitectureAHB内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复