vivado中FFT IP核的基本使用

最近用vivado仿真时需要用到FFT IPCore,调通程序的过程中也遇到一些麻烦,在此将一些问题进行总结,希望可以帮到有需要的人。

- 配置阶段

在IP Catalog中搜索FFT,然后双击即可进入配置页面。

- 第一栏为Configuration,其中的通道数量和变换长度等参数根据自己的需求选择即可;

- 第二栏为Implementation,我的设置为:

| Data Format | Fixed Point |

|---|---|

| Scaling Options | Unscaled |

| Rounding Modes | Convergent Rounding |

其中需要说明的是 Scaling Options ,我要完成的是256点的IFFT,初期以为需要使用scaled模式,然后查阅官方资料,发现写的并不是很清晰,我看完后并不能明确的知道如果选择了scaled模式后应该如何配置s_axis_config_tdata端口。之后了解到,我选择Unscaled模式即可,系统会根据你选择的FFT点数对输出位数进行扩展。比如我的输入位宽为16位,FFT点数为256点,选用Unscaled模式后,系统自动将输出位宽变为25位。但是由于vivado中要求数据宽度均为8的倍数,因此实际端口有64位宽,你只需心里明白[63:0]中[56:32]代表虚部、[24:0]代表实部即可。关于各端口的各位说明,可以在配置页左侧的 Implementation Details 一栏中了解(该栏中内容非常重要,可以让你了解每个端口的详细信息)。

- 第三栏为Detailed Implementation,默认即可,一般无需变动。

- 代码部分

配置完成后,在例化该模块时,建议调用系统生成的代码,在IP Sources→xfft_0→Instantiation Template中打开xfft_0.veo即可,此为verilog语言版本。其代码如下:

xfft_0 your_instance_name (

.aclk(aclk), // input wire aclk

.s_axis_config_tdata(s_axis_config_tdata), // input wire [7 : 0] s_axis_config_tdata

.s_axis_config_tvalid(s_axis_config_tvalid), // input wire s_axis_config_tvalid

.s_axis_config_tready(s_axis_config_tready), // output wire s_axis_config_tready

.s_axis_data_tdata(s_axis_data_tdata), // input wire [31 : 0] s_axis_data_tdata

.s_axis_data_tvalid(s_axis_data_tvalid), // input wire s_axis_data_tvalid

.s_axis_data_tready(s_axis_data_tready), // output wire s_axis_data_tready

.s_axis_data_tlast(s_axis_data_tlast), // input wire s_axis_data_tlast

.m_axis_data_tdata(m_axis_data_tdata), // output wire [63 : 0] m_axis_data_tdata

.m_axis_data_tuser(m_axis_data_tuser), // output wire [7 : 0] m_axis_data_tuser

.m_axis_data_tvalid(m_axis_data_tvalid), // output wire m_axis_data_tvalid

.m_axis_data_tready(m_axis_data_tready), // input wire m_axis_data_tready

.m_axis_data_tlast(m_axis_data_tlast), // output wire m_axis_data_tlast

.event_frame_started(event_frame_started), // output wire event_frame_started

.event_tlast_unexpected(event_tlast_unexpected), // output wire event_tlast_unexpected

.event_tlast_missing(event_tlast_missing), // output wire event_tlast_missing

.event_status_channel_halt(event_status_channel_halt), // output wire event_status_channel_halt

.event_data_in_channel_halt(event_data_in_channel_halt), // output wire event_data_in_channel_halt

.event_data_out_channel_halt(event_data_out_channel_halt) // output wire event_data_out_channel_halt

);

对于输出端口,直接命名一相同位宽的变量与之连接即可。对于输入端口,则需要根据其作用予以适当的激励信号,官方文档中的说明有助于对端口的了解。下面对其中几个端口稍作说明

- s_axis_config_tdata,Unscaled模式下,该端口只有最低为有效,0为FFT,1为IFFT,其余为置0即可;

- s_axis_data_tlast,该端口应在每一帧的最后一个数据输入时拉高,我并没有这样做,且不影响结果;

- m_axis_data_tuser,该端口指明每一输出数据在该帧中的序号,是重要的参考信号,配置时需要勾选XK_INDEX。

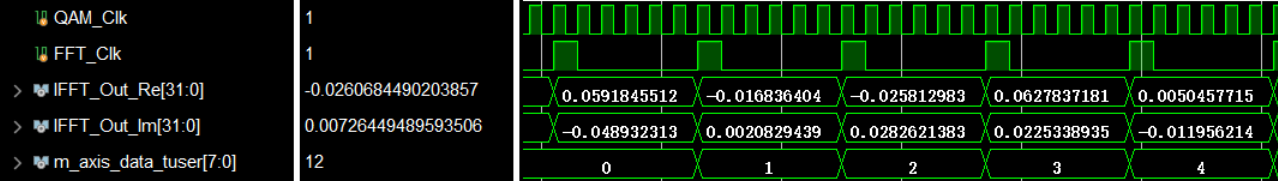

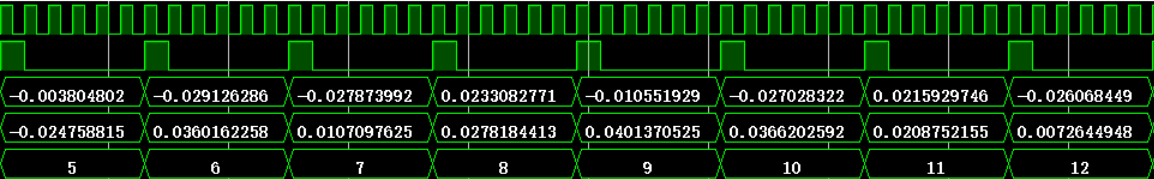

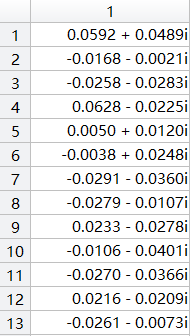

其余输入端口只要阅读官方文档即可很容易理解,端口配置正确程序就很容易跑通,如下是我的运行结果:

- 结果说明

可以看出,vivado和matlab对同一组数据进行IFFT运算后结果相同。还需要说明一点的是,对于定点数,在做FTT时会扩展整数部分,做IFFT时,会扩展小数部分。对于2的N次方点IFFT,小数部分的扩展位数为N。比如在我的程序中,输入数据位宽为16,其中最高位为符号位,其余15位为小数位。经过256点IFFT之后,小数位扩展为23位,在真实数值设定时需加注意。真实数值设置方法如下:在仿真结果界面中的Objects一栏中,右击你想要设置的端口名,然后Radix→Real Settings,选择Fixed Point,其中Binary point即为小数位宽。

由于我还不是很熟悉CSDN编辑方式,上传图片后画面过大,影响观感,因此对于一些更适合用图片解释的步骤并没有使用图片。欢迎大家一起讨论该IP核中的其他功能。

这个视频给了我很大帮助,建议还不会使用该IP核的人认真观看,感谢小鱼同学制作的视频

https://mp.weixin.qq.com/s/1TeuQuBGIEbSB-X_0KKnbg

最后

以上就是老实钢笔最近收集整理的关于XILINX FFT IP核的基本使用的全部内容,更多相关XILINX内容请搜索靠谱客的其他文章。

发表评论 取消回复