原文链接:https://pediaa.com/what-is-the-difference-between-behavioral-and-structural-model-in-verilog/

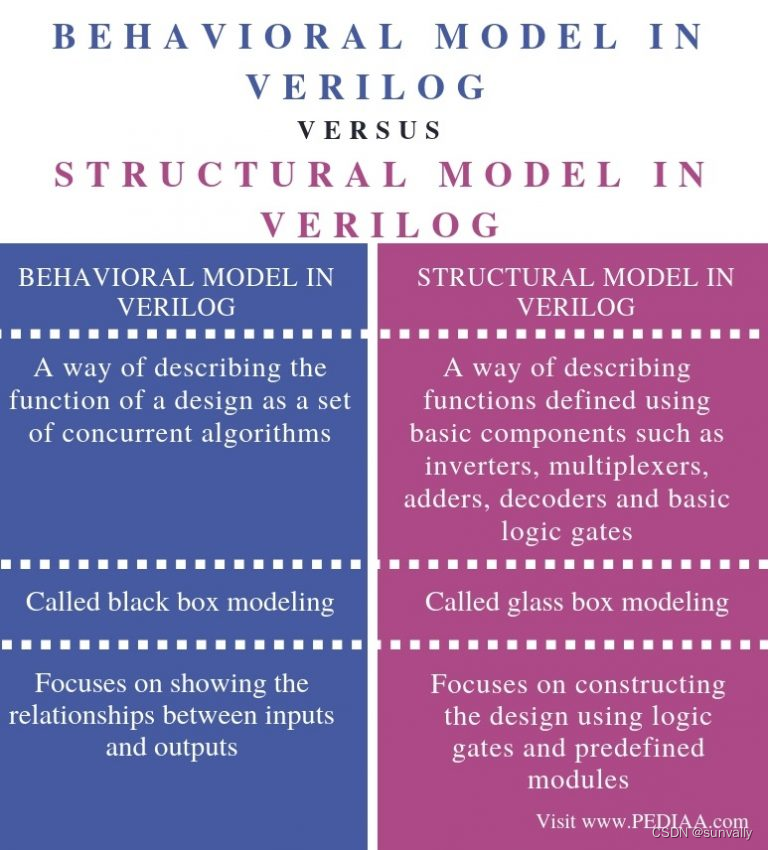

The main difference between behavioral and structural model in Verilog is that behavioral model describes the system in an algorithmic manner, while structural model describes the system using basic components such as logic gates.

Generally, a computer program is a set of instructions that allows the CPU to perform a task. There are various programming languages such as high-level and low-level languages. Moreover, there is a special type of software called Hardware Description Language (HDL). HDL is useful in describing the structure and the behaviours of electronic circuits. Verilog is a common HDL.

Key Areas Covered

- What is Behavioral Model in Verilog

- Definition, Functionality

- What is Structural Model in Verilog

- Definition, Functionality - Difference Between Behavioral and Structural Model in Verilog

- Comparison of Key Differences

Key Terms

Behavioral Model, Black Box Modeling, Glass Box Modeling, HDL, Structural Model, Verilog

What is Behavioral Model in Verilog

The behavioral model describes a system in an algorithmic way. Here, each algorithm is sequential. In other words, each algorithm consists of a set of instructions that execute one after the other. Furthermore, the behavioral model helps in controlling the simulation and manipulate variables of the data types.

Moreover, procedural statements are common behavioral models in Verilog. Each procedure has its own activity flow. Also, procedural assignments are useful for updating reg, integer, time and memory variables. Besides, a blocking procedural assignment statement should execute before executing the statements that follow it in a sequential block. However, these blocking procedural assignments do not prevent the execution of statements that follow it in a parallel block.

What is Structural Model in Verilog

The structural model describes a system using basic components such as digital gates and adders. In structural modeling, the programmer or the designer thinks about the circuit as a box or a module. It is encapsulated from the outer environment. In other words, it communicates with the outer environment through inputs and outputs.

Moreover, it is possible to describe the structure inside a module using gates and submodules. Also, it defines how these modules are connected to each other and to the module ports. Furthermore, the structural model helps to draw a schematic diagram for the circuit.

Difference Between Behavioral and Structural Model in Verilog

Definition

The behavioral model is a way of describing the function of a design as a set of concurrent algorithms. On the other hand, Structural model is a way of describing functions defined using basic components such as inverters, multiplexers, adders, decoders and basic logic gates. Thus, this describes the main difference between behavioral and structural model in Verilog.

Synonyms

Black box modeling is another name for behavioral modeling, while glass box modeling is another name for structural modeling.

Main Focus

Moreover, another difference between behavioral and structural model in Verilog is that the behavioral model focuses on showing the relationships between inputs and outputs, while the structural model focuses on constructing the design using logic gates and predefined modules.

Conclusion

In brief, there are two types of design models in Verilog; they are the behavioral and structural model. The main difference between behavioral and structural model in Verilog is that the behavioral model describes the system in an algorithmic manner, while the structural model describes the system using basis components such as logic gates.

References:

- Tala, Deepak Kumar. Introduction, 1 Feb. 1970, Available here.

Image Courtesy:

- ”Hitachi J100″ By C J Cowie at the English language Wikipedia (CC BY-SA 3.0) via Commons Wikimedia

最后

以上就是虚幻世界最近收集整理的关于What is the Difference Between Behavioral and Structural Model in Verilog的全部内容,更多相关What内容请搜索靠谱客的其他文章。

![assert all(tensors[0].size(0) == tensor.size(0) for tensor in tensors) AssertionError](https://www.shuijiaxian.com/files_image/reation/bcimg14.png)

发表评论 取消回复