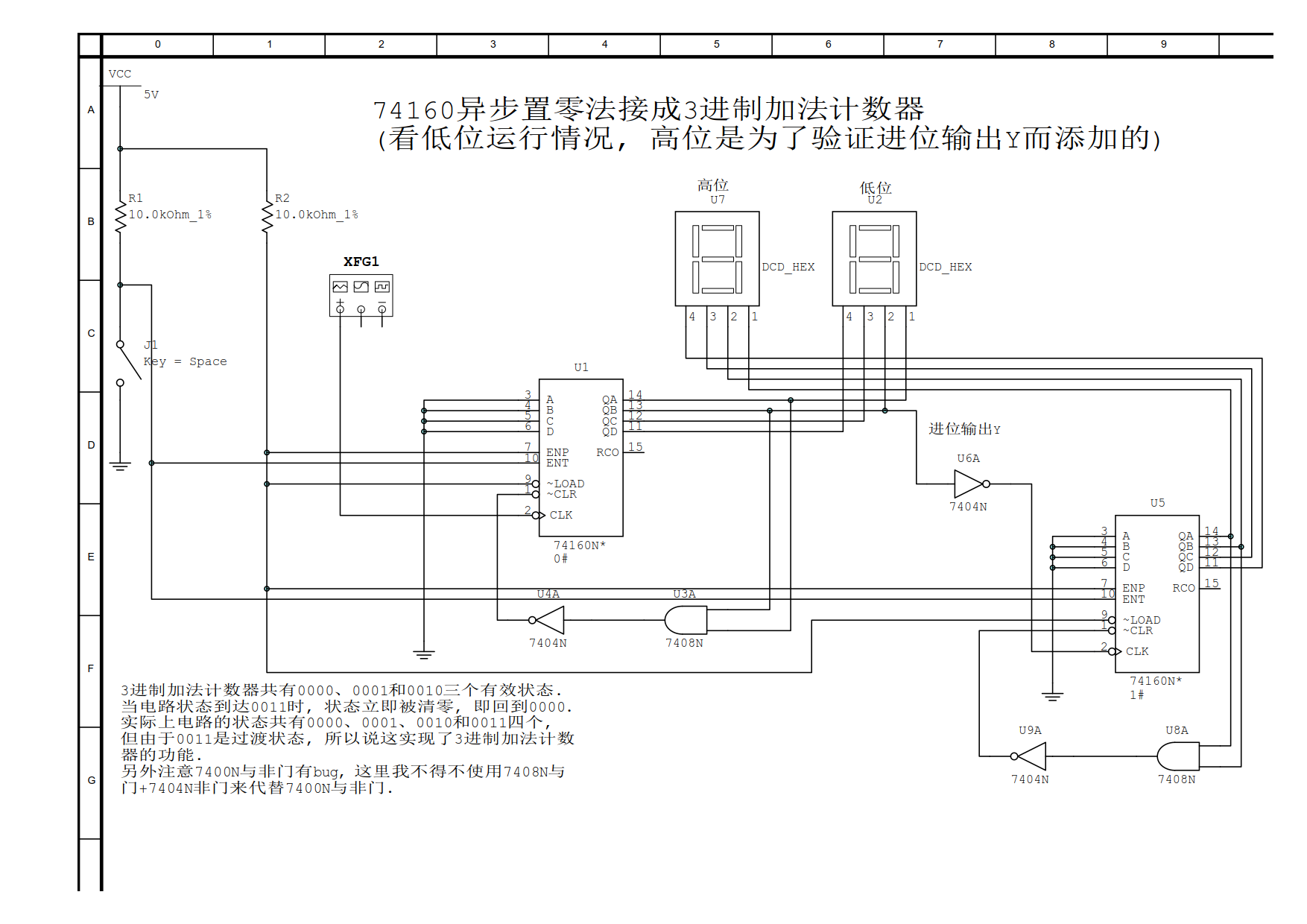

我们先来看一下电路图, 从中提取核心信息:

①QB、QA通过一级与门后再通过一级非门接到CLR引脚.

3进制加法计数器共有3个有效状态0000、0001和0010, 而电路状态到达0011时, CLR引脚立即变为低电平, 电路状态清零, 即变为0000, 而后CLR引脚又恢复高电平, 计数器继续计数. 0011其实是一个过渡状态, 不算在有效状态之类. 故接成的电路实现了3进制加法计数器的功能.

②电路的状态是如何变化的.

0000 —> 0001 —> 0010 ---> 0011(一闪而过) ---> 0000.

③进位输出Y为何这样设计.

(对比⑧来学习)

直接将QB作为进位输出Y即可. 如此一来, 电路状态和进位输出Y的关系为 0000(Y=0) —> 0001(Y=0) —> 0010(Y=1) ---> 0011(Y=1) ---> 0000(Y=0): 通过一级非门接到高位74160的CLK引脚后, 在0011->0000时实现了一次上升沿的过程.

值得说明一下的是, multisim7中74160芯片的触发方式为上升沿触发: 虽然CLK引脚处有小圆圈, 理论上应该为下降沿触发, 但经过大量实验后验证, 其触发方式的确为上升沿触发. multisim7中有一些芯片的触发方式确实和直观表达(是否带小圆圈)的不同, 这一点不必过多纠结.

④低位对高位的进位是如何实现的.

我们先来看一下电路的状态和进位输出Y的关系: 0000(Y=0) —> 0001(Y=0) —> 0010(Y=0) ---> 0011(Y=1) ---> 0000(Y=0): 可以看出, 电路状态从0011变化到0000时, Y实现了一次下降沿, 与74160的触发方式相反, 所以在进位输出后加入一级非门, 再连接到高一位74160的CLK引脚即可.

⑤A、B、C、D四个引脚为什么都接地.

在异步清零法中, 其实对A、B、C、D四个引脚没有使用. 但为了视觉上的平衡, 我才将它们全部接地.

⑥在电路中为什么不直接使用与非门, 而是使用一级与门和一级非门.

multisim7中的二输入与非门7400N在功能上可能存在bug, 无法正常表达逻辑含义, 所以我用一级与门和一级非门代替一级与非门的功能.

⑦异步清零法有用到74160的LOAD引脚吗.

在异步清零过程中没有用到LOAD引脚. 但为了使74160正常计数, 才将LOAD引脚置为1.

⑧进位输出Y还有别的设计方法吗.

有别的设计方法: 根据之前设计N进制加法计数器(上升沿触发)的经验, 当电路状态到达最大状态时, 进位输出Y=1(其他时刻=0), 故这里当电路状态到达0011时, Y=1(其余状态下Y=0). 即将QA、QB接到二输入与门后, 其输出即为进位输出Y.

⑨感觉74160的应用设计变化莫测, 有时不能考虑周全.

这说明你对于同步时序逻辑电路基础设计部分的内容掌握得不够扎实, 需回过头去, 仔细研读该部分内容, 并再设计一定数量的同步时序逻辑电路. 除了需要熟练的设计外, 还需要对二进制数字间的逻辑关系有着较敏锐的洞察力(也可以说是一种找规律并简化过程的能力).

最后

以上就是负责烤鸡最近收集整理的关于74160异步清零法解析(以接成三进制加法计数器为例)的全部内容,更多相关74160异步清零法解析(以接成三进制加法计数器为例)内容请搜索靠谱客的其他文章。

发表评论 取消回复