Verilog 2选1选择器及其综合结果vivado

本篇文章是我本人的理解,我也还是在学习中,有不对的地方欢迎指出。

使用的工具为vivado,首先说一下 FPGA 内部的三大主要资源,分别为 (1)可编程IO资源、(2)布线资源、(3)可编程逻辑单元CLB,(注意:这是三大主要资源,还有别的资源,具体上网查找,有很多资料)。

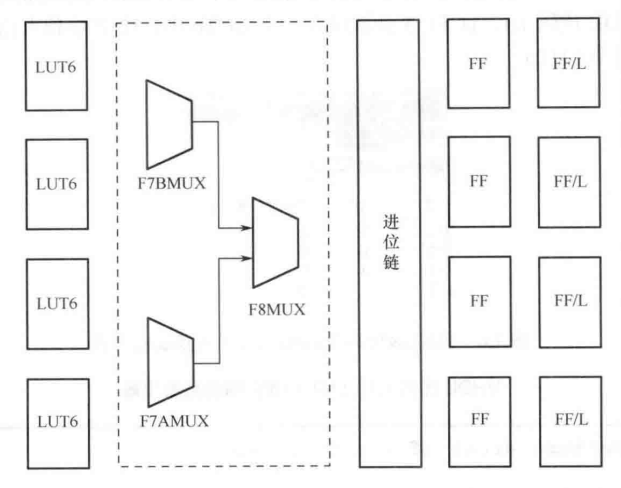

其中,可编程逻辑单元CLB最丰富,由两个SLICE构成,SLICE有SLICEL(L:Logic)和SLICEM(M:Memory)之分,具体的就去网上找找吧,很多资料说明结构,我就不说了,SLICEL和SLICEM内部都包含4个6输入查找表(LUT6)、3个数据选择器(MUX)、1个进位链(Carry Chain)和8个触发器(Flip-Flop)。

下面上CLB单元的结构图如下:

注意:三个MUX的作用是为了组合4个LUT6的,这对于接下来的综合结果很重要

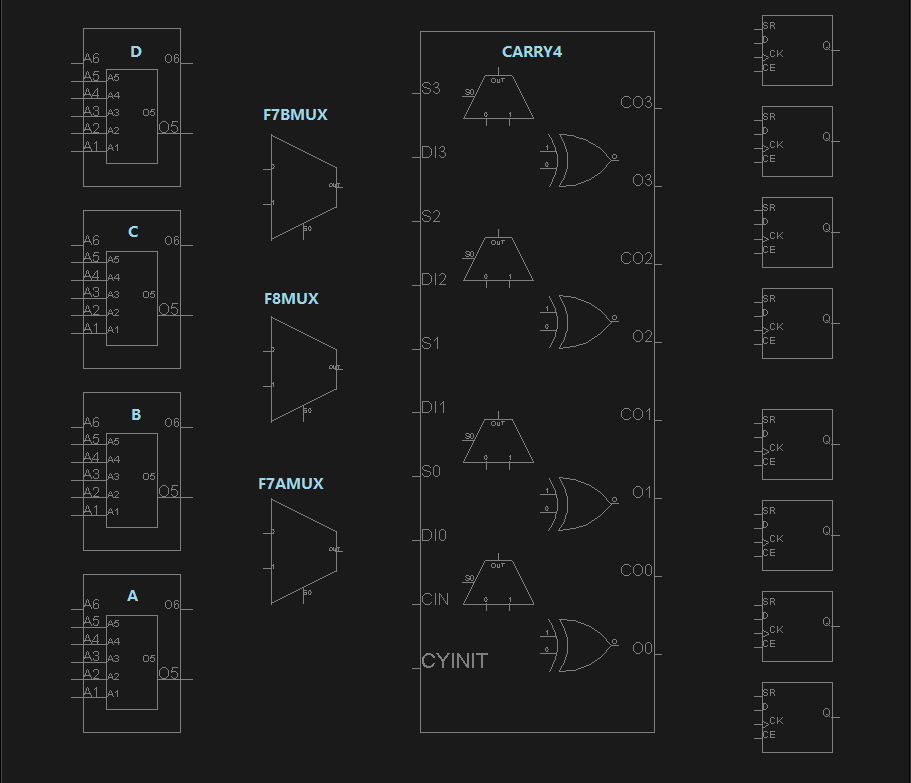

具体在vivado中的显示如图:

因为FPGA的大部分功能是基于查找表来实现的,所以选择器也是基于查找表来实现的,综合出来的结果是LUT,而不是MUX,MUX的作用是用来组合4个LUT的(目前知道是这个作用)

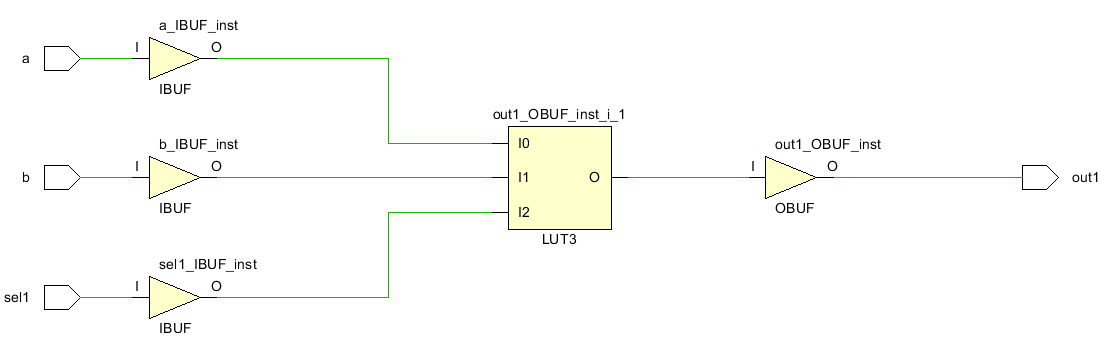

下面是一个2输入选择器,代码如下:

module multiplexer(

input a,

input b,

input sel1,

output out1

);

assign out1 = sel1?a:b;

endmodule

综合出来的结果如图:

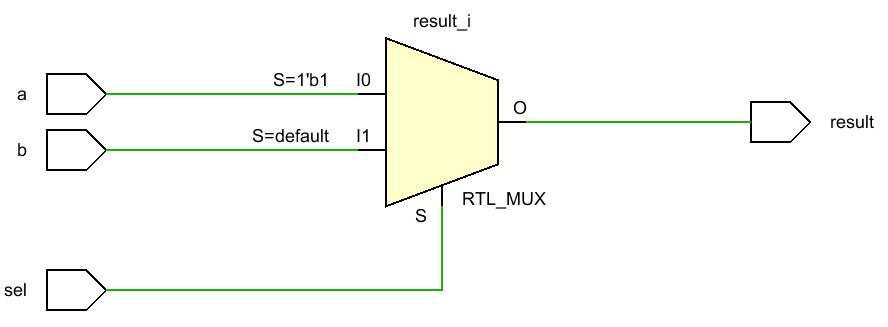

而不是下面这样的图(如果用原语可以综合成下面这张图),

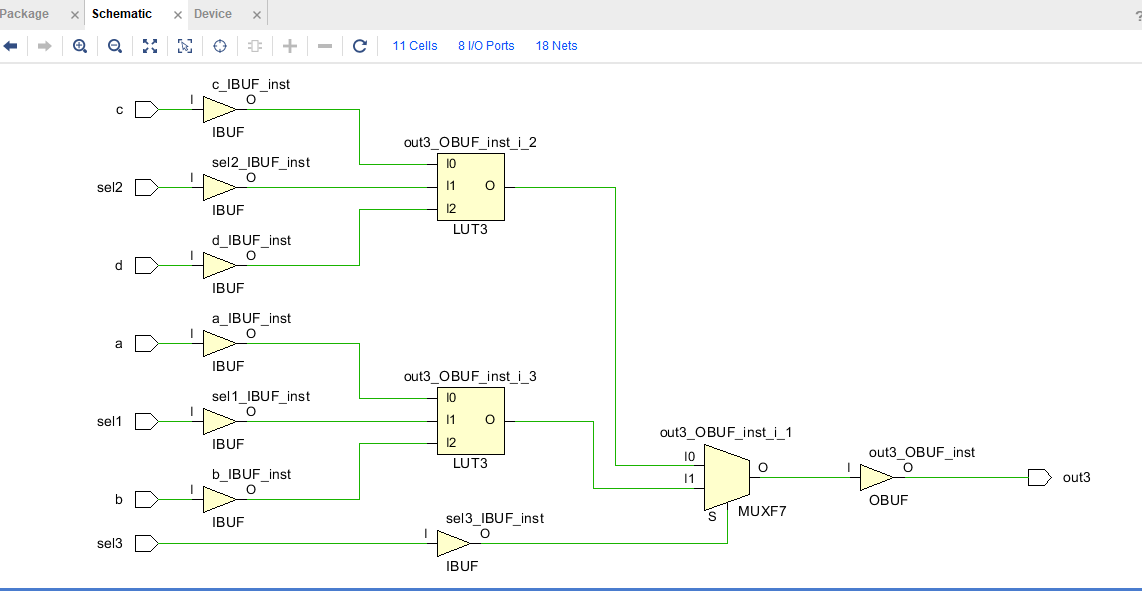

下面来两个2选1选择器组合起来再看综合后的图:

module multiplexer(

input a,

input b,

input c,

input d,

input sel1,

input sel2,

input sel3,

output out3

);

wire out1;

wire out2;

assign out1 = sel1?a:b;

assign out2 = sel2?c:d;

assign out3 = sel3?out1:out2;

endmodule

所以,MUX单元是用来组合LUT单元的,当然,还有别的MUX单元的用法。

最后

以上就是大气冬日最近收集整理的关于Verilog 2选1选择器及其综合结果 基于vidado的全部内容,更多相关Verilog内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复