异步时序逻辑电路分析步骤:

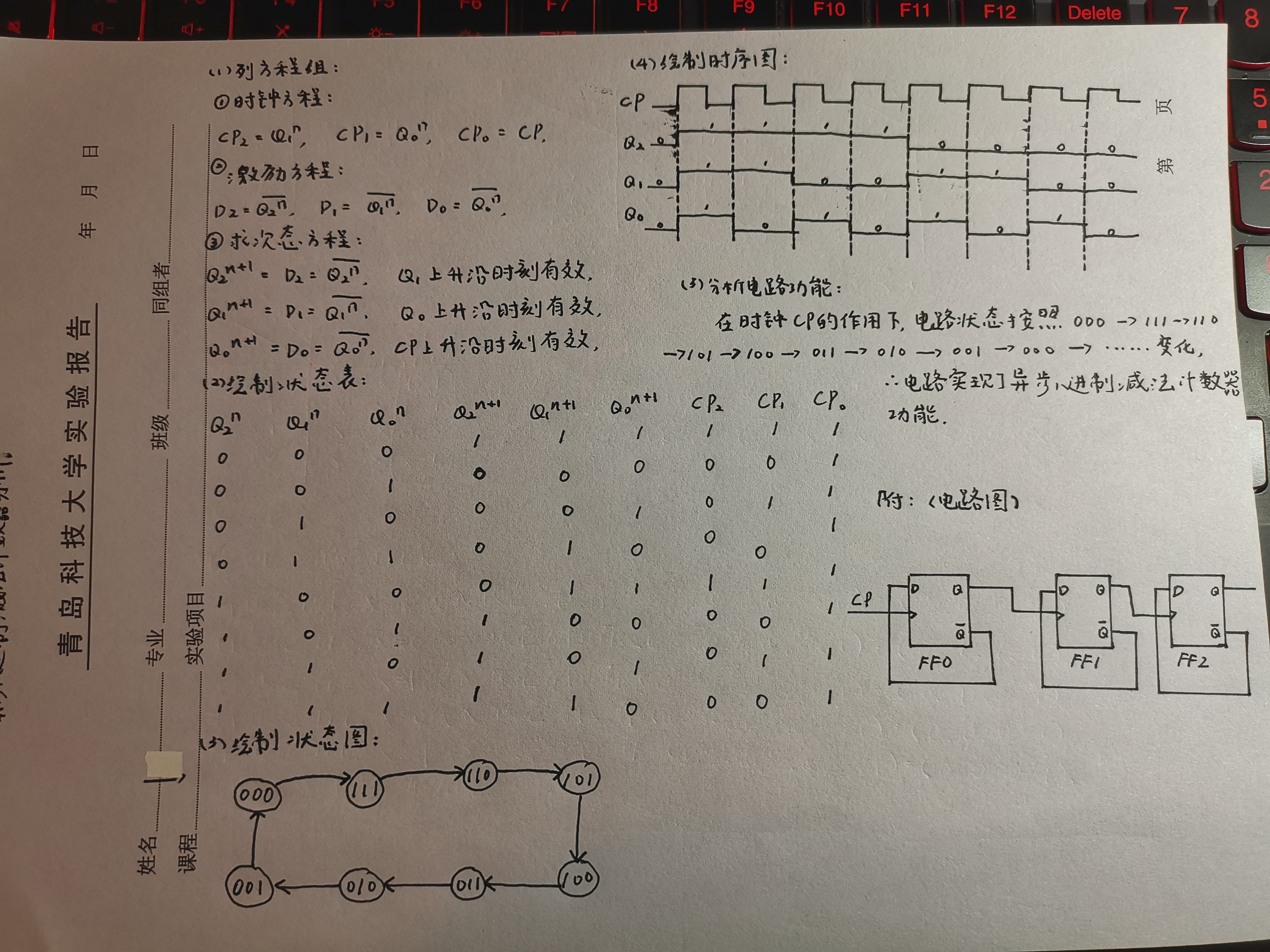

(1)列方程组:

①时钟方程, ②激励方程, ③次态方程.

(2)绘制状态表.

绘制状态表时的思路与同步时序逻辑电路有些许不同: 要根据每个触发器的时钟方程来填充状态表. 以这里的分析过程举例. 、

、

= 1时, 表示时钟有效; 否则时钟无效. 由于0#触发器的时钟信号引脚直接接到系统的时钟信号线上, 故0#触发器和系统时钟CP保持一致: 这是求次态的突破口. 这样一来, 系统

有效时,

也有效, 所以

. 既然

一直有效(当系统时钟CP有效时), 那么就按照次态方程求出所有的

. 之后, 根据

, 得知只有在

上升沿时,

才按照触发器次态方程进行状态转换: 其他时刻数据保持不变. 如此一来, 就可以求出所有的

. 再根据

, 得知只有在

上升沿时,

才按照触发器次态方程进行状态转换: 其他时刻数据保持不变. 综上所述, 状态表填充完毕. 值得一提的是, 对于状态表中的某一行, 现态到次态的变化时刻为系统时钟的有效时刻(这里

的变化时刻和系统时钟有效时刻吻合, 但

、

的变化会相应滞后): 若三个触发器的状态都要发生改变 ,则状态改变的先后顺序为

, 这期间会有一定的时间消耗.

异步电路的各个触发器时序转换存在一定的延迟, 也就是说, 从现态到次态的转换过程中有一段不稳定的时间. 在此期间, 电路的状态是不确定的. 因此, 异步时序电路的输入信号(包括时钟信号)必须等待电路进入稳定状态后才允许发生改变, 否则电路会处于不确定状态.

对于状态表中的某一行来说, 总会有一个CP信号是和系统时钟信号同步的, 所以当系统有效时刻到来时, 这个触发器也迎来有效时刻. 那么, 这个和系统时钟同步的触发器的CP在状态表中的任何一行都为1, 即只要系统时钟有效, 该触发器的时钟也有效.

(3)绘制状态图.

(4)绘制时序图.

(5)分析电路功能.

最后

以上就是诚心小甜瓜最近收集整理的关于异步八进制减法计数器分析的全部内容,更多相关异步八进制减法计数器分析内容请搜索靠谱客的其他文章。

发表评论 取消回复