实验:用modelsim完成主从D触发器的门级建模

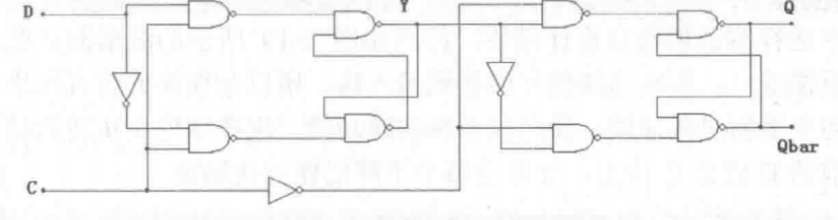

主从D触发器的电路图

实验步骤:

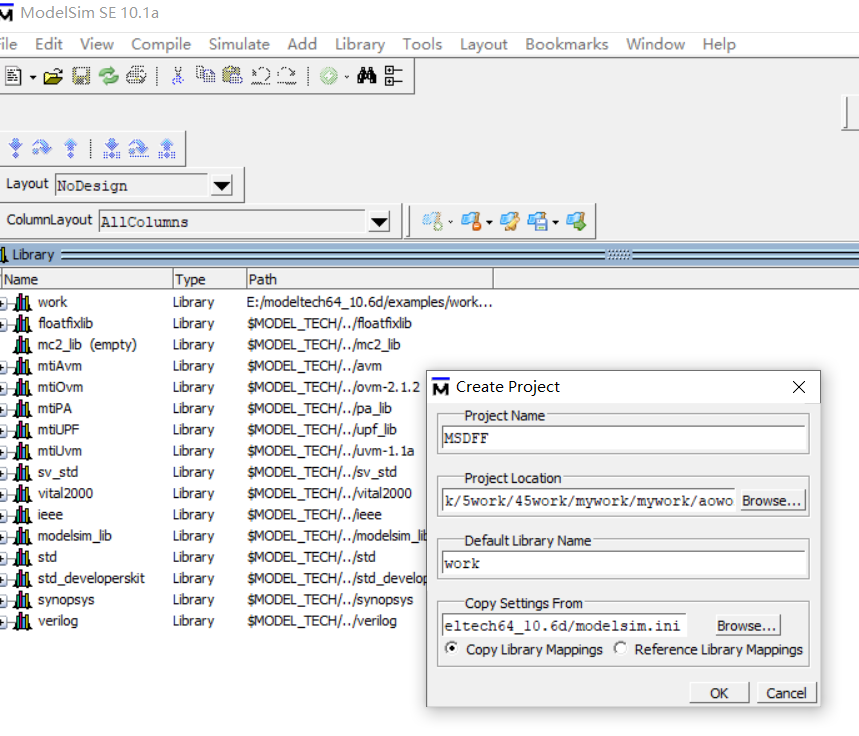

一、打开modelsim新建一个project MSDFF

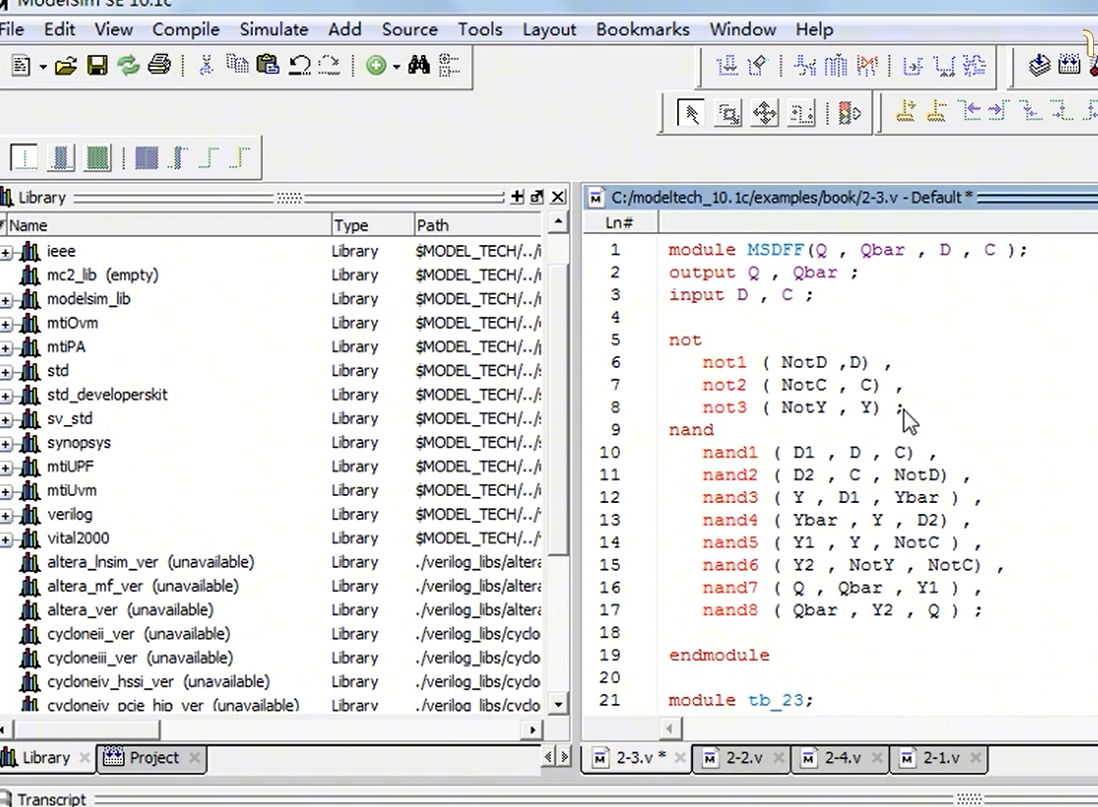

2、新建一个文件名为MSDFF的Verilog的文件名,建好后打开文件输入代码,进行编译

代码1

module tb_23;

reg d;

reg clk;

wire q, qbar;

initial clk=0;

always #5 clk=~clk;

initial

begin

d=0 ;

#7 d=1;

#4 d=0;

#9 d=1;

#11 d=0;

#20 $stop;

end

MSDFF ms_dff(q,qbar,d,clk);

endmodule

代码2

module MSDFF(Q,Qbar,D,C);

output Q,Qbar;

input D , C;

not

not1 ( NotD ,D) ,

not2 ( Notc , C) ,

not3 ( NotY , Y);

nand

nand1 ( D1 , D ,C ) ,

nand2 ( D2 , c , NotD) ,

nand3 ( y , D1 , Ybar ) ,

nand4 ( ybar , Y , D2) ,

nand5 ( y1 , r , NotC) ,

nand6 ( Y2 , NotY , NotC) ,

nana7 (Q, Qbar, Y1) ,

nand8 (Qbar , Y2 , Q) ;

endmodule

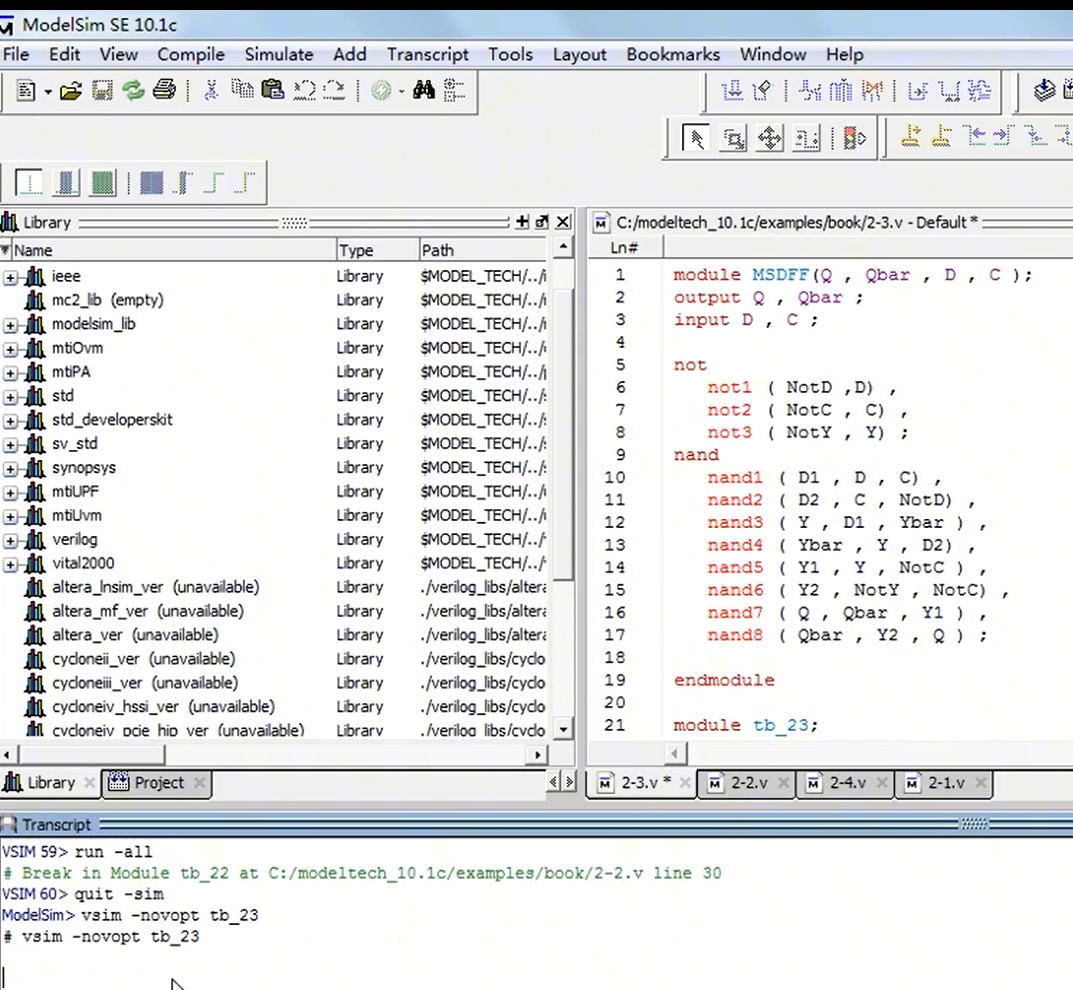

3、编译成功

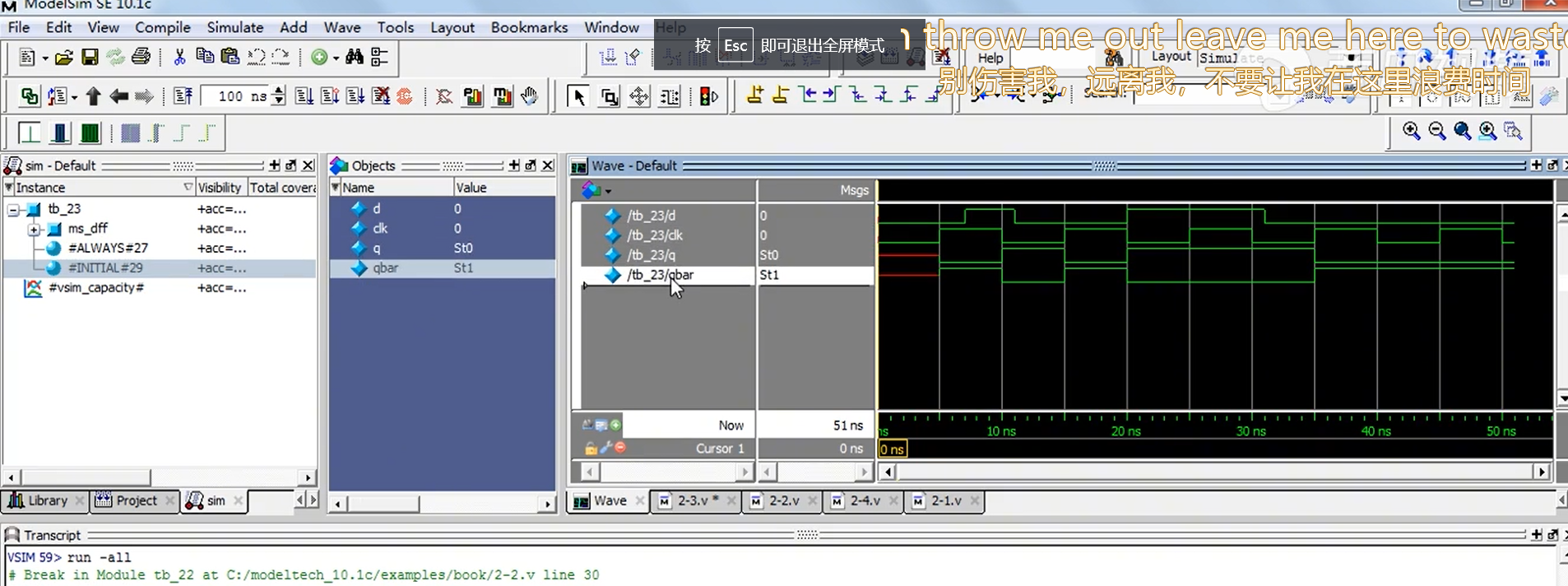

4、进行运行仿真成功

最后

以上就是顺利小松鼠最近收集整理的关于主从D触发器的门级建模的全部内容,更多相关主从D触发器内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复