P1 时序分析基本概念

1. 时序分析的分类

静态时序分析分为片内时序分析(寄存器与寄存器之间的时序关系)和片外时序分析(IO时序分析)。

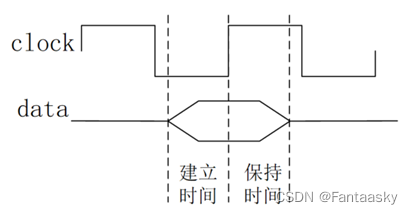

2. 建立时间和保持时间

(1)建立时间 setup time

在时钟事件(上升沿/下降沿)发生之前数据信号应保持稳定的时间。

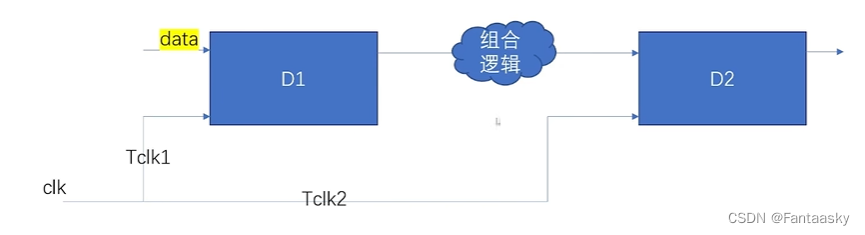

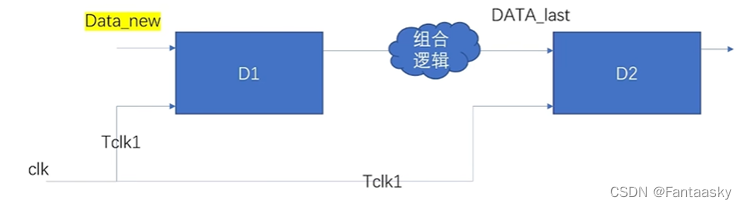

把实际电路抽象成前级D触发器+组合逻辑+后级D触发器。

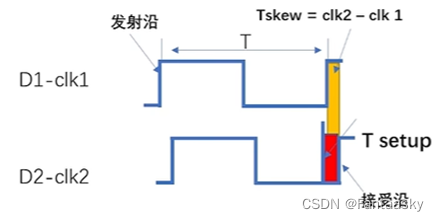

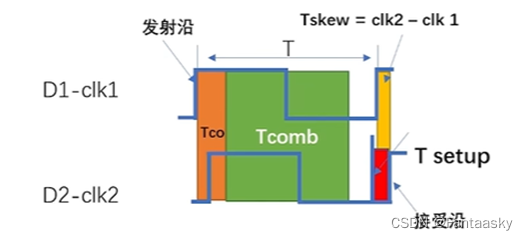

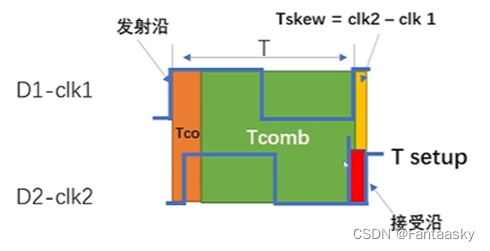

系统时钟通过wire和除法器D1和D2相连,线传输延时分别为Tclk1和Tclk2,这里为了计算方便,归一化为时间偏斜Tskew = Tclk2 – Tclk1。// 也就是下图的橙色部分

当clk1上升沿时,data从前级D1进入。首先在D1寄存器内存在延时Tco,然后经过组合逻辑产生延迟Tcomb,然后到达D2。如果在经过那么多延时之后,数据在可接受的建立时间之前已经进入稳定状态,那么就满足了建立时间。如下图:

不满足建立时间导致时序违例的情况如下:

这样就很直观了。可以通过公式表达,当满足建立时间时:

![]()

优化建立时间的途径:

①降低时钟频率(增加T,但是对于频率有要求的情况不合适)

②通过优化代码和电路结构来降低Tcomb(前端需要做的事情)

③通过布局布线来控制Tskew(后端需要做的事情)

④控制Tco和Tsetup(厂家决定)

(2)保持时间 hold time

在时钟事件(上升沿/下降沿)发生之后数据信号保持稳定的时间。

保持时间时序检查确保新数据不会在触发器稳定输出初始数据之前过早到达D端而覆盖其初始数据。

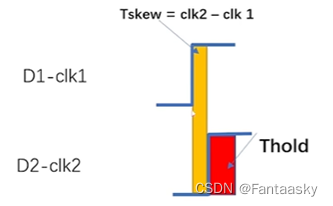

对同样的模型进行分析:

一段data刚出D1,经过一定延时到达D2的门口,然后基于clk2的上升沿完成了输出。这段旧的data被称为data_last。在不考虑Tskew的情况下,前一个触发器D1的触发信号clk1在clk2上升沿的同时也进入了上升沿。如果data_last没有保持稳定足够多的时间,那么data_new就会在很快的时间内把data_last给冲刷掉,然后成为新的输出。

考虑到Tskew的情况,时序图如下:

如果要满足保持时间足够不违例,需要满足以下式子:

![]()

转化成裕量的表达式:

![]()

优化保持时间的途径:

①保持时间和时钟频率无关,不能改变时钟频率

②通过优化代码和电路结构来增加Tcomb

③通过布局布线来控制Tskew(后端需要做的事情)

④控制Tco和Tsetup(厂家决定)

(3)建立/保持松弛(裕量)setup slack/hold slack

综合以上式子,可以得到用来描述建立时间和保持时间满足违例与否程度的参数:

![]()

![]()

建立裕量setup slack和保持裕量hold slack必须维持在正数才能保证没有出现时序冲突。

P2 寄存器间时序分析建立时间分析

1. 建立时间例题

Tcycle = 10ns; Pin2Pll = 2ns; Pll2clk1 = 3ns; Pll2clk2 = 2ns;

Tdata = 3ns; Tsu = 0.5ns; Tco = 1ns;

求(1)setup slack;(2)Fmax

(1)首先注意,Pin2Pll由于是clk1和clk2的共同路径,所以与setup slack无关。

Tskew = Pll2clk2 – Pll2clk1 = -1 ns

T_slack_setup = 10 – 1 – 3 – 0.5 – 1 = 4.5 ns

(2)Fmax = 1 / ( Tcycle – T_slack_setup ) = 1 / 5.5

// 这会是十分常见的面试题

2. 时序分析建立时间实例

(1)部署时序约束

没有pll的需要部署时序约束,有pll的因为输入端一定自动部署了,所以就不需要。

Edit Timing Constraints-Create Clock-Source Objects-Waveform

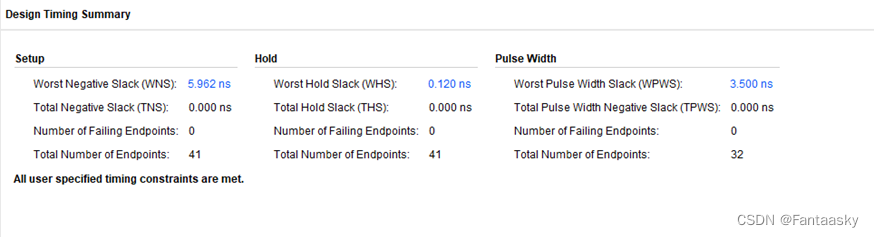

(2)Report Timing Summary

在这里可以看到一些总结性指标,用于判断是否出现了时序违例。

①Setup

Worst Negative Slack:最坏负松弛,正数表示没有冲突。

Total Negative Slack:总负松弛,当满足所有时序约束时,为0ns,有冲突时,为负数。

Number of Failing Endpoints:失败断点的个数。

②Hold

Worst Hold Slack:最坏保持松弛,正数表示没有时序冲突。

Total Hold Slack:总保持松弛,正常为0ns。

③Pulse Width

Worst Pulse Width Slack:最坏脉冲宽度松弛。

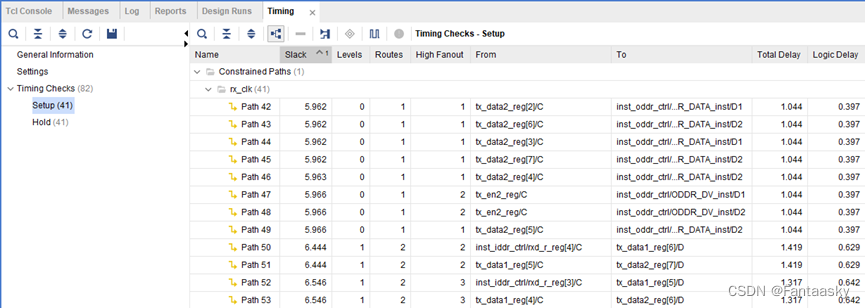

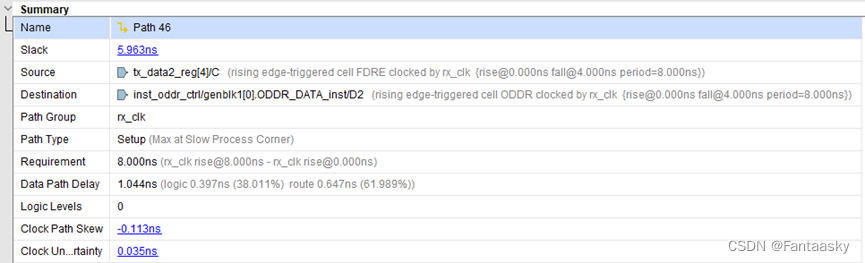

(3)Report Timing

在这里可以看到每条路径的各种时序信息。

选择一条路径,就可以看到这条路径在经过每个节点的时序信息。

可以看到:

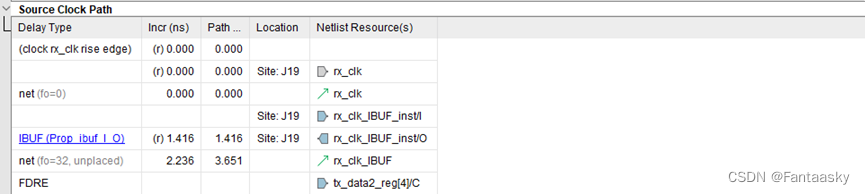

①Source Clock Path

在Source Clock Path中,可以看到源端的时延特征。同步时钟网络在系统前级需要有一个IBUF,即输入缓冲。

其中,第一个net和IBUF的延迟是寄存器前分支时钟网络再前面的主干时钟网络(与目的端的共同路径)。

后面第二个net就是Tclk1。

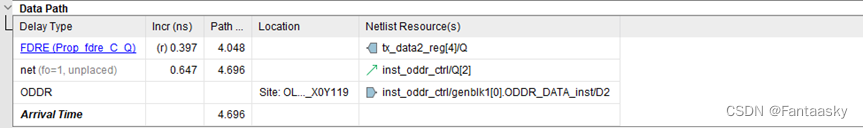

②Data Path

中间组合逻辑的路径时序特征。

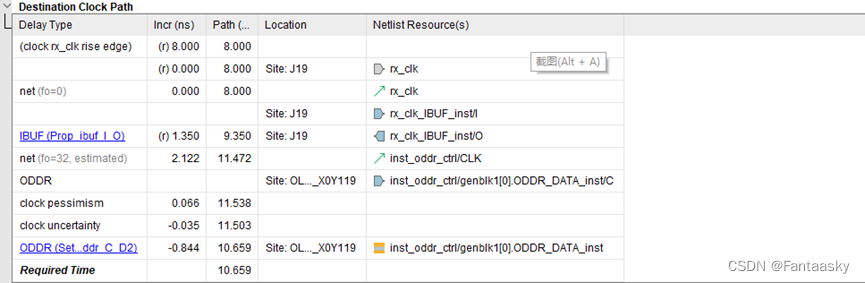

③Destination Clock Path

目的端时延特征。可以看到前面有和源端时延特征一样的几项:第一个net和IBUF,这几项就是共同路径的延迟。

后面第二个net就是Tclk2。

Clock permission代表时钟悲观度,代表源端和目的端的共同路径时延之差,用于在时差最大的条件下分析最悲观情况的时延特征。

// Clock permission = 目的端共同路径时延 – 源端共同路径时延

Clock uncertainty代表时钟不确定度,由芯片工艺啥的决定。

④相关计算

Clock path skew(时钟偏斜) = Tclk2 – Tclk1

// 也可以用如下式子:

Clock path skew = 目的端总时延 – 源端总时延 + 时钟悲观度

Slack = Required Time – Arrival Time

最后

以上就是笨笨歌曲最近收集整理的关于Vivado静态时序分析学习笔记(1)P1 时序分析基本概念P2 寄存器间时序分析建立时间分析的全部内容,更多相关Vivado静态时序分析学习笔记(1)P1内容请搜索靠谱客的其他文章。

发表评论 取消回复