不说具体应用,仅仅说说如果自己的FPGA开发板是高电平复位有效,而自己又需要使用低电平有效的复位操作怎么办呢?

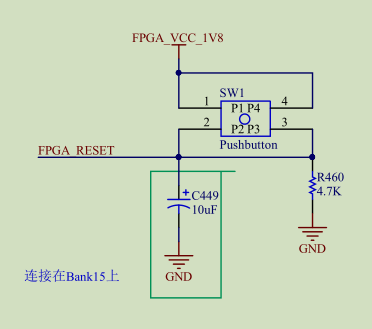

FPGA的高电平复位实例:

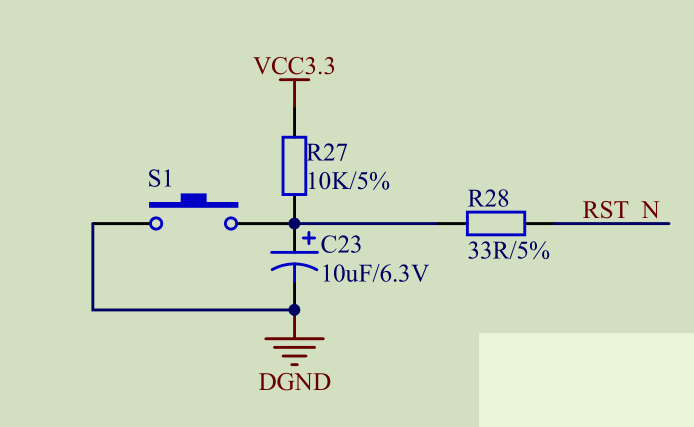

FPGA低电平复位实例:

一定要对自己所用的FPGA复位是高电平还是低电平弄清楚,否则会出现问题,而自己又胡乱找原因,最后还怀疑自己。

一般来说,对于高电平复位的fpga,我们在编写Verilog代码时,如果要复位,就是这样:

always@(posedge clk or posedge reset) begin

if(reset) begin

......

end

......

......

end

但是如果我们需要这种形式的复位行不行呢?如下:

always@(posedge clk or negedge rst_n) begin

if(!rst_n) begin

...

end

......

......

end

当然也不是不行,在上述代码加上一句:

assign rst_n = ~reset;即可

前提也是要定义一个wire rst_n;

当然,reset依然是输入复位端口,只不过转换了一下逻辑而已。

最后

以上就是含糊红牛最近收集整理的关于高电平复位还是低电平复位?的全部内容,更多相关高电平复位还是低电平复位内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复