实战PCB电磁兼容之布局篇

- 一、PCB叠层

- 二、PCB布局

首先我们需要知道,原理图设计后,针对PCB设计技巧,有什么是比较重要的:

- 好的叠层结构

- 布线前有好的电气架构设计

小小编觉得可能大部分layout工程师并不会特意的说是针对电磁兼容设计去布局布线,首要肯定是功能上的需求:有质量的布通。

整体上来说是从三点来看电气架构设计:

电源完整性:

- 滤波处理(噪声的扩散–串扰)

- 去耦处理、压差、谐振分析(避免噪声的过大)

信号完整性:

- 匹配(避免噪声过大)

- 串扰抑制、时序分析、损耗分析

电磁兼容性:

- 防护滤波(噪声的扩散–串扰)

- 保护敏感体(隔离、屏蔽、避免串扰过大)

一、PCB叠层

好的叠层在PCB的回路上(差模发射)以及连接板的电缆上(共模发射)产生的辐射都最小。

关于电路板的叠层,有以下四个因素:

- 层数

- 平面的类型和数量(电源/地)

- 层的次序

- 层间距

因此,设计使用多层板时,应注意以下几点:

- 信号层应与参考平面相邻,且与相邻平面紧密耦合;

- 电源层应与接地平面紧密耦合(即层间距小),且一般内缩20H;

如果实在空间紧张,可以在板边打两排地孔,电源平面内缩到两排地孔之内。特殊情况也要保证内缩到第一排地孔之内。

- 多层接地平面有利于降低参考平面的阻抗,减小共模辐射;

- 当在多层同时布局布线关键信号时,它们应该被限制在与同一平面相邻的两层上;

- 实际设计时,还要考虑成本、布线难易、信号回流、系统频率、屏蔽和开发进度时间等实际情况。

二、PCB布局

关于PCB布局布线三个目的:

- 控制噪声(抑制噪声源)

- 控制串扰的发生或者过大(抑制耦合路径)

- 保护敏感体(防止被干扰引发性能降级)

根据三个目的,有布局三原则:

第一个优先顺序原则

- 芯片的去耦优先级高于串阻及外围控制配置器件

- 先防护后滤波

- 强噪声高于低噪声

第二个布局方向原则

- 板内以芯片为中心,以外围电路为郊区(距离芯片越近的靠近芯片放置)

- 接口侧以接口为中心,以外围器件为郊区(距离接口越近的靠近接口放置)

第三个同类相吸,异类分开

- 属于同类元器件最好放置在一起,减小电流环路面积

- 不属于同类的元器件,最好拉大距离(强弱噪声电路之间)

那么我们有什么实际PCB设计技巧呢?

- 高频信号远离IO口;

- PCB叠层设计

- 去耦电容布局近

- 防护滤波原则:先防护后滤波隔离 等

- 产品的电源端口的防护滤波布局,如果空间允许,建议一字型排布局

- TVS管、高频电容远离内电路

- 针对控制信号的防护滤波处理方法(防止静电设计,滤波来自驱动信号的噪声)等

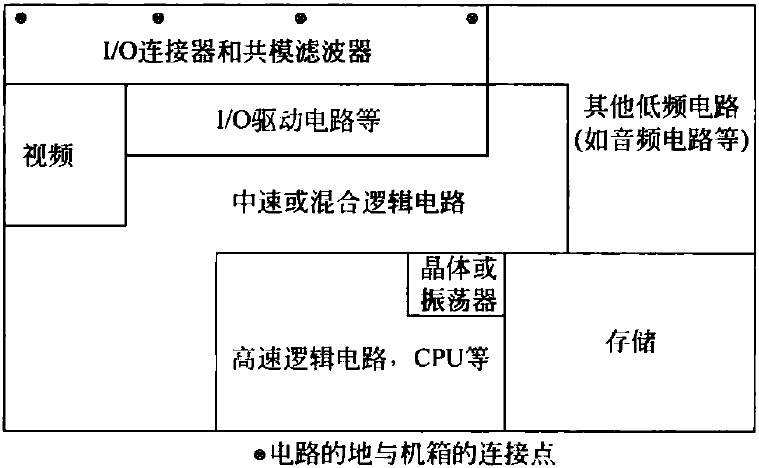

对于PCB来说,首要的就是器件布局,合理的布局可以最小化布线长度,提高信号质量,最小化寄生耦合,并且减少PCB的发射和敏感性。关于布局的注意点如下,也可参考下图的例图:

- 高速逻辑和存储器IC不应位于I/O区附近;

- 晶体或高速振荡器应位于使用它们的IC附近;

- I/O驱动器应靠近连接器;

- 低频模拟电路或音视频电路应接近I/O区而不必通过电路板的高频数字区。

高频电路产生的高频电磁场很容易耦合到I/O连接器。因此,如果电路板的尺寸允许,那么至少这两部分电路应尽量分开布局,且关键信号应远离电路板的边缘。

分享微信公众号『设计至纯』,查看更多原创内容,O(∩_∩)O一键三连????、分享????、收藏、点赞、支持????????。 ^ o ^ 您的点赞、评论和关注,是小小编继续创作的不懈动力。 ????

最后

以上就是忧郁树叶最近收集整理的关于【EMC电磁兼容】02.05——PCB图的实战落地细节之布局的全部内容,更多相关【EMC电磁兼容】02.05——PCB图内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复