关注、星标公众号,直达精彩内容

整理:技术让梦想更伟大 | 李肖遥

链接:https://itexp.blog.csdn.net/article/details/85029696

问题

最近在使用 STM32F3 芯片的时候,遇到这样一个问题:如果外部中断来的频率足够快,上一个中断没有处理完成,新来的中断如何处理?

在调试时,发现有中断有 挂起、激活、失能等状态,考虑这些状态都是干啥用的呢!他们是 Cortex-M 核所共有的,因此,这里不针对与具体用的 STM32 MCU,直接上升到 Cortex-M 内核来了解一下!

简介

中断(也称为“异常”)是微控制器一个很常见的特性。中断一般是由硬件(例如外设、外部引脚)产生,当中断产生以后 CPU 就会中断当前的程序执行流程转而去处理中断服务中指定的操作。

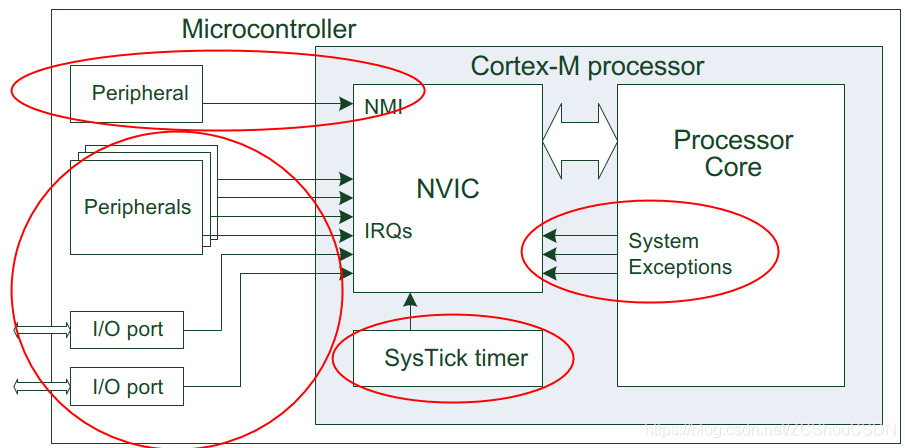

所有的 Cortex-M 内核都会包含一个用于中断处理的组件:NVIC(Nested Vectored Interrupt Controller,嵌套向量中断控制器)。它处理处理中断,还处理其他需要服务的事件(例如 SVC 指令),通常称为异常(按照 ARM 的说法,中断也是一种异常)。

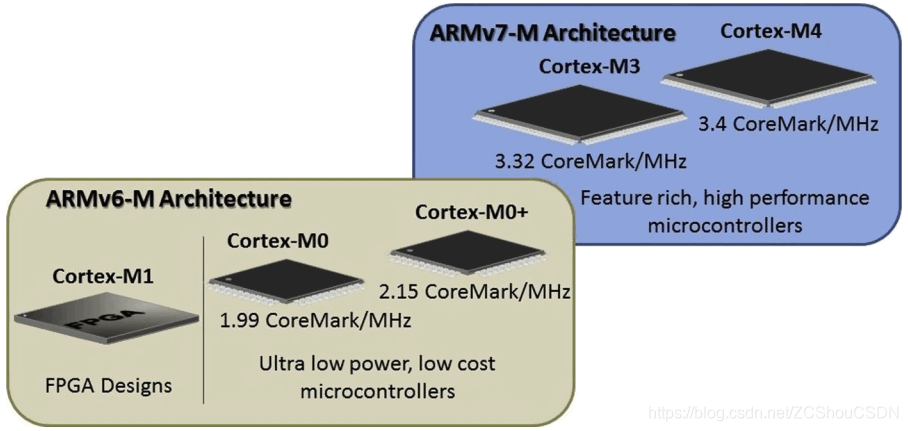

Cortex-M3 和 Cotex-M4 的 NVIC 最多支持 240 个 IRQ(中断请求)、1 个不可屏蔽中断(NMI)、1 个 Systick(滴答定时器)定时器中断和多个系统异常。而 Cortex-M0 最多支持 32 个 IRQ、1 个不可屏蔽中断(NMI)、1 个 Systick(滴答定时器)定时器中断和多个系统异常。

IRQ: 多数由定时器、IO 端口、通信接口等外设产生

NMI: 通常由看门狗定时器或者掉电检测器等外设产生

其他: 主要来自系统内核

注意,本文所说的 Cortex-M 主要指定是 Cotex-M3 和 Cotex-M4。

Cortex-M0、Cortex-M0+、Cortex-M1 基于 ARMv6-M。与 Cotex-M3 和 Cotex-M4 相比,他们的指令集较小。而且,Cortex-M1 是专门为FPGA 应用设计的,没有独立 MCU。

异常类型

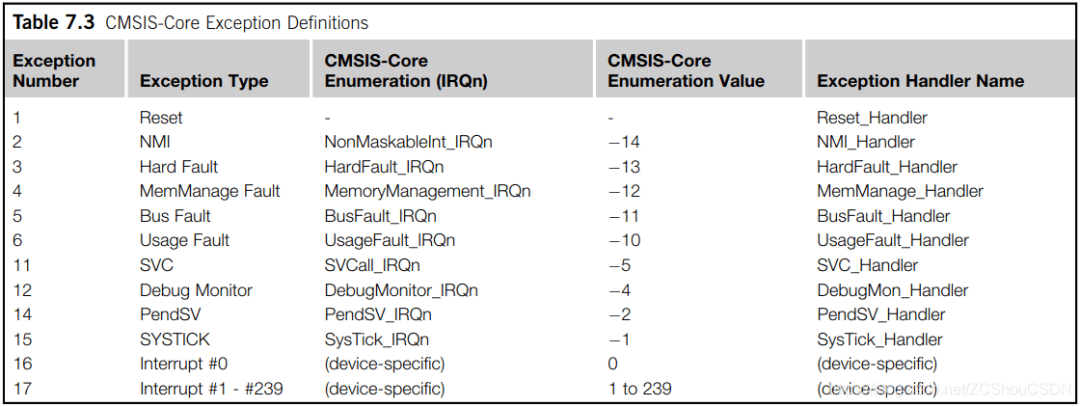

Cortex-M 处理器的异常中,编号 1~15 的为系统异常,16 及以上的则为中断输入。所有中断级别的异常都具有可编程的优先级。部分系统异常具有固定优先级。ARM 给出了以下一张表:

| 类型 | 位置 | 优先级 | 描述 |

|---|---|---|---|

| - | 0 | - | 在复位时栈顶从向量表的第一个入口加载 |

| Reset 复位 | 1 | -3(最高) | 在上电和热复位(warm reset)时调用,在第一条指令上优先级降到最低(线程模式),异步的 |

| Non-maskable Interrupt 不可屏蔽中断(NMI) | 2 | -2 | 不能被除复位之外的任何异常停止或占先。异步的。 |

| Hard Fault 硬故障 | 3 | -1 | 由于优先级的原因或可配置的故障处理被禁止而导致不能将故障激活时的所有类型故障,同步的 |

| Memory Management 存储器管理 | 4 | 可配置 | MPU 不匹配,包括违反访问规范以及不匹配,是同步的,即使MPU 被禁止或不存在,也可以用它来支持默认的存储器映射的XN 区域 |

| Bus Fault 总线故障 | 5 | 可配置 | 预取指故障,存储器故障,以及其它相关的地址/存储故障,精确时是同步,不精确时时异步 |

| Usage Fault 使用故障 | 6 | 可配置 | 使用故障,例如,执行未定义的指令或尝试不合法的状态转换,是同步的 |

| - | 7~10 | - | 保留 |

| SVCall 系统服务调用 | 11 | 可配置 | 利用 SVC 指令调用系统服务,是同步的 |

| Debug Monitor 调试监控 | 12 | 可配置 | 调试监控,在处理器没有停止时出现,是同步的,但只有在使能时是有效的,如果它的优先级比当前有效的异常的优先级低,则不能被激活 |

| - | 13 | - | 保留 |

| PendSV 可挂起的系统服务请求 | 14 | 可配置 | 可挂起的系统服务请求,是异步的,只能由软件来实现挂起 |

| SysTick 系统节拍定时器 | 15 | 可配置 | 系统节拍定时器(System tick timer)已启动,是异步的 |

| External Interrupt 外部中断 | 16 及以上 | 可配置 | 在内核的外部产生(外部设备),INTISR[239:0],通过 NVIC(设置优先级)输入,都是异步的 |

针对 Cortex-M 系列的内核,ARM 提供了一套叫做 CMSIS 的东西。目前,所有的 MCU 均使用 CMSIS 作为编程基础。在 CMSIS-Core 中,中断标识有中断枚举实现,从数值 0 开始(代表中断 #0)。其中,系统异常的编号为负数。具体如下:

CMSIS-Core 之所以使用另外一种编号系统,是因为这样可以稍微提高部分 API 的效率。中断的编号和枚举定义是同设备相关的,他们位于微控制器供应商提供的头文件中,在一个名为 IRQn 的 typedef 段中。

中断处理(异常处理)

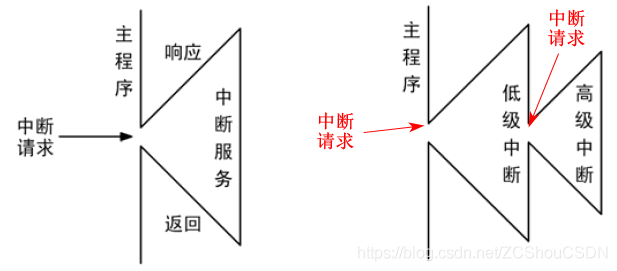

当某种内部或外部事件发生时,MCU 的中断系统将迫使 CPU 暂停正在执行的程序,转而去进行中断事件的处理,中断处理完毕后,又返回被中断的程序处,继续执行下去。

主程序正在执行,当遇到中断请求(Interrupt Request)时,暂停主程序的执行转而去执行中断服务例程(Interrupt Service Routine,ISR),称为响应,中断服务例程执行完毕后返回到主程序断点处并继续执行主程序。多个中断是可以进行嵌套的。正在执行的较低优先级中断可以被较高优先级的中断所打断,在执行完高级中断后返回到低级中断里继续执行。

中断管理

管理中断所使用的大部分寄存器都位于 NVIC(Nested Vectored Interrupt Controller,嵌套向量中断控制器)和 SCB(System Control Block,系统控制块)中。实际上,SCB 是作为 NVIC 的一部分来实现的,不过在 CMSIS-Core 中,将其定义在了独立的结构体中。除此之外,处理器内核中还有用于中断屏蔽寄存器:PRIMASK、FAULTMASK、BASEPRI。

NVIC 和 SCB 位于系统控制空间,地址从 0xE000E00 开始,大小 4KB。SCB 中还有 SysTick 定时器,存储器保护单元等。

优先级

这部分暂且不说!

中断输入和挂起

在 Cortex-M 内核中,每个中断都具有多个属性:

每个中断都可以被禁止(默认)或者使能

每个中断都可以别挂起或者解除挂起

每个中断都可以处于活跃或者非活跃

这些状态属性具有多种可能的组合。例如,在处理中断时,可以将其禁止,若在中断退出前产生了同一个中断的新请求,由于该活跃中断被禁止了,那就会处于挂起状态。

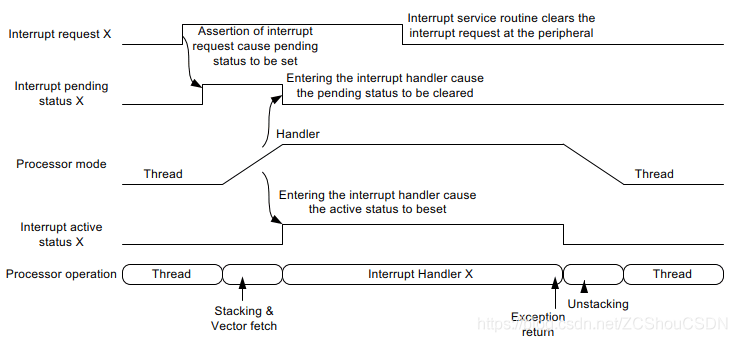

NVIC 在设计上既支持产生 脉冲中断请求 的外设,也支持产生 高电平中断请求 的外设。无需配置任何一个 NVIC 寄存器以选择其中一种中断类型。对于脉冲中断请求,脉冲宽度至少要为一个时钟周期;而对于电平触发的请求,在 ISR 中的操作清除请求之前,请求服务的外设要一直保持电平信号(如写入寄存器以清除中断请求) 。尽管外部中断请求在 I/O 引脚上的电平可能是低电平有效,但是 NVIC 收到的请求信号为高有效!

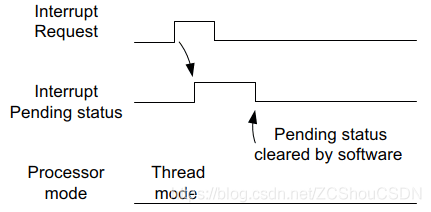

中断的挂起状态被存储在 NVIC 的可编程寄存器中,当 NVIC 的中断输入被确认后,它就会引发该中断的挂状态。即便中断请求被取消,挂起状态仍会为高。这样,NVIC 就可以处理脉冲中断请求了。

挂起状态的意思是,中断被置于一种等待处理器处理的状态。有些情况下,处理器在中断挂起时就会进行处理。不过,若处理器已经在处理另外一个更高或同优先级的中断,或者中断被某个中断屏蔽寄存器给屏蔽掉了,那么在其他的中断处理结束前或者中断屏蔽被清除前,挂起请求会一直保持。

在传统 ARM 处理器中,如果外设产生了中断,那么它们得到处理前必须一直保持中断请求信号。

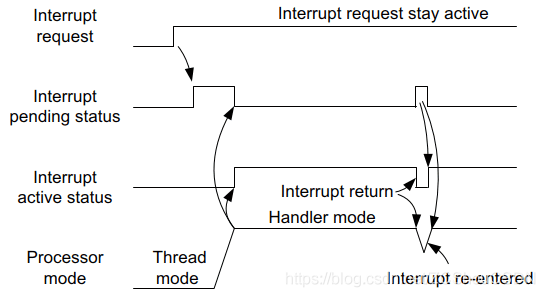

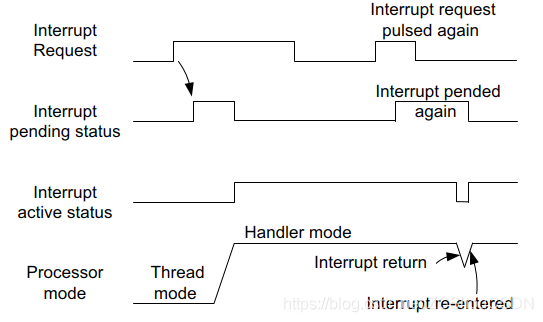

当中断开始处理中断请求时,中断的请求信号会被自动清除。当中断正在被处理时,它就会处于活跃状态。

当中断处于活跃状态时,处理器无法再中断完成和异常返回前再次处理同一个中断请求。

中断的挂起状态位于中断挂起状态寄存器中,软件可以复位这些寄存器。因此,可以手动清除或者设置中断的挂起状态。若中断请求产生时处理器正在处理另一个具有更高优先级的中断,而在处理器对该中断请求做出响应之前,挂起状态被清除掉了,则该中断会被取消且不会再得到处理。

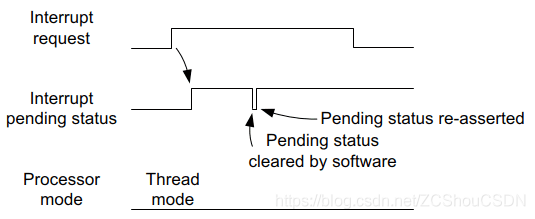

若持续保持某个中断请求,那么及时软件尝试清除该挂起状态,挂起状态还是会再次被置位的。

若中断已经得到了处理,中断源仍然在继续保持中断请求,那么这个中断就会再一次进入挂起状态且再次得到处理

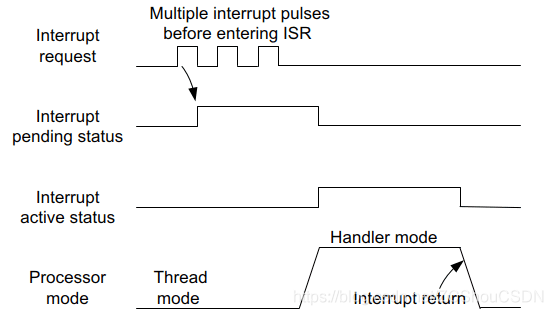

对于脉冲中断请求,若在处理器开始处理前,中断请求信号产生了多次,他们会被当做一次中断请求处理

中断挂起状态可以在其正在被处理时再次置位。之前的中断请求正在被处理时产生了新的请求,这样机会引发新的挂起状态。处理器在前一个 ISR 结束后需要再次处理这个中断。

即使中断被禁止了,他的挂起状态仍然可置位。 这种情况下,若中断稍后被使能了,它仍然可以被触发并被得到处理。这种情况可能不是我们需要的,因此需要在使能 NVIC 中断前手动清除挂起状态。

总结

NVIC 中对于每个中断需要设置 抢占优先级 和 响应优先级(又称子优先级)。多个中断会先比较 抢占优先级,抢占优先级相同的比较响应优先级。高抢占优先级能够打断低抢占优先级的,但是相同抢占优先级的高响应优先级不能打断低响应优先级。

高优先级的抢占优先级是可以打断正在进行的低抢占优先级中断的。

抢占优先级相同的中断,高响应优先级不可以打断低响应优先级的中断。

抢占优先级相同的中断,当两个中断同时发生的情况下,哪个响应优先级高,哪个先执行。

如果两个中断的抢占优先级和响应优先级都是一样的话,则看哪个中断先发生就先执行。

参考

The Definitive Guide to ARM Cortex-M3 and Cortex-M4 Processors, 3rd Edition

The De?nitive Guide to the Cortex-M0

版权声明:本文来源网络,免费传达知识,版权归原作者所有。如涉及作品版权问题,请联系我进行删除。

‧‧‧‧‧‧‧‧‧‧‧‧‧‧‧‧ END ‧‧‧‧‧‧‧‧‧‧‧‧‧‧‧

关注我的微信公众号,回复“加群”按规则加入技术交流群。点击“阅读原文”查看更多分享,欢迎点分享、收藏、点赞、在看。最后

以上就是复杂书本最近收集整理的关于Cortex-M 内核中断/异常系统、中断优先级/嵌套 详解问题简介异常类型中断处理(异常处理)中断管理优先级中断输入和挂起总结参考的全部内容,更多相关Cortex-M内容请搜索靠谱客的其他文章。

发表评论 取消回复