文章目录

- Logisim基本组件介绍

- 前言

- 功能菜单

- 自动生成电路

- 毛刺现象

- 震荡现象

- logisim自带组件介绍

- 基本器件介绍

- 复用器库主要组件

- 运算器库常用组件介绍

- 存储库

- 输入输出库

- 一些概念问题

- 高低电频有效的概念

Logisim基本组件介绍

前言

简介:本文只是对logisim自带的组件做了一个介绍,并不设计基本组合逻辑部件以及时序逻辑部件的设计

教程推荐:华中科大logisim教程

Tips

- alt+数字键可以方便的改变引脚位宽

- 左下角可以改变视图显示大小和选择消除点阵(用于截图)

- ‘三态’和‘未定义处理’是指是否添加高阻态和高阻态下状态是上拉还是下拉

- 选中元件,再使用快捷键ctrl+D可以快速创建一个元件副本

- 直接选中门再按下数字键可以快速更改门的数量

- 可以全选所有元件一起修改数据位宽

- 可以在线路中添加探针来实时观察

- 要向已经完成的电路在其他电路中调用,直接将电路从左侧拖入主界面即可,会自动生成一个封装了内部结构的元件

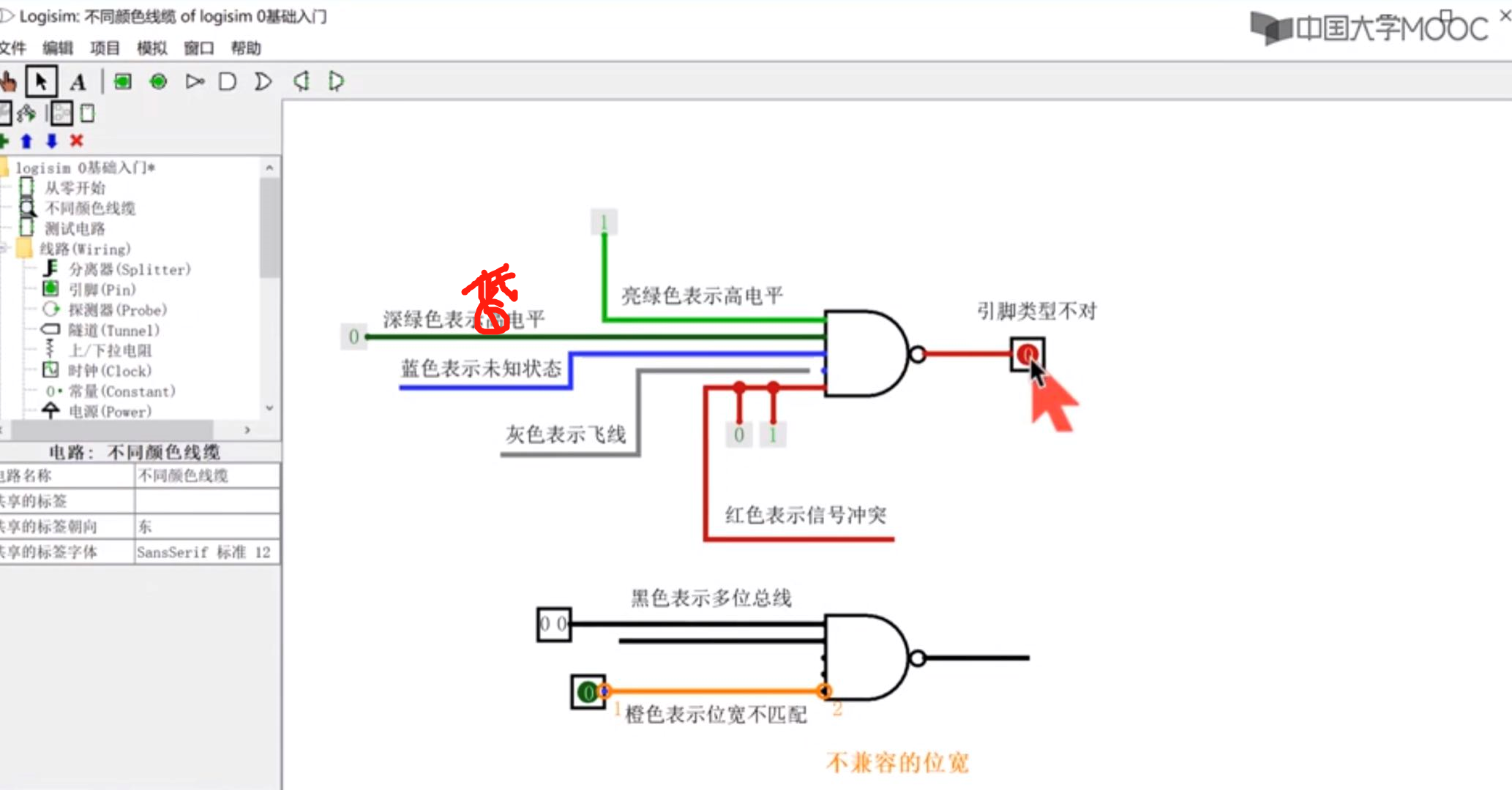

线路状态图

功能菜单

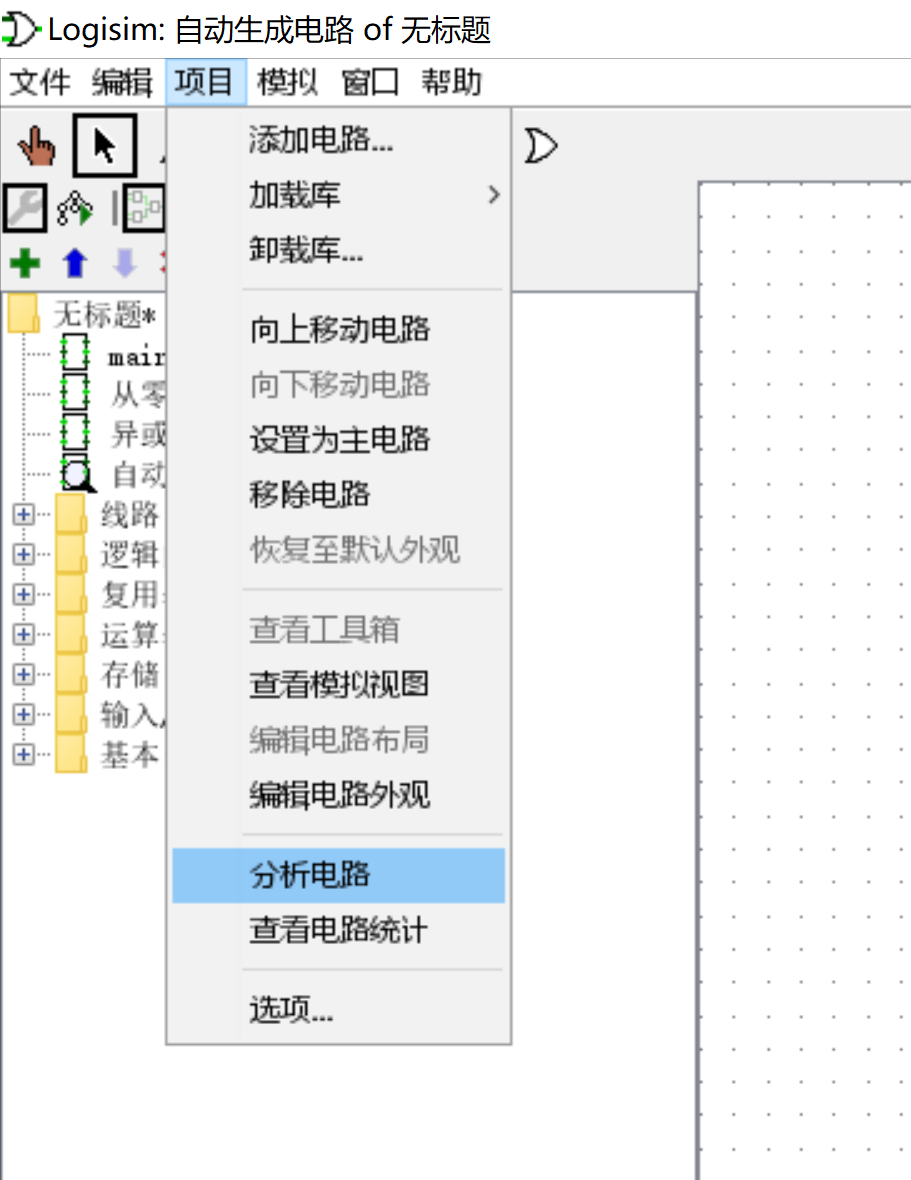

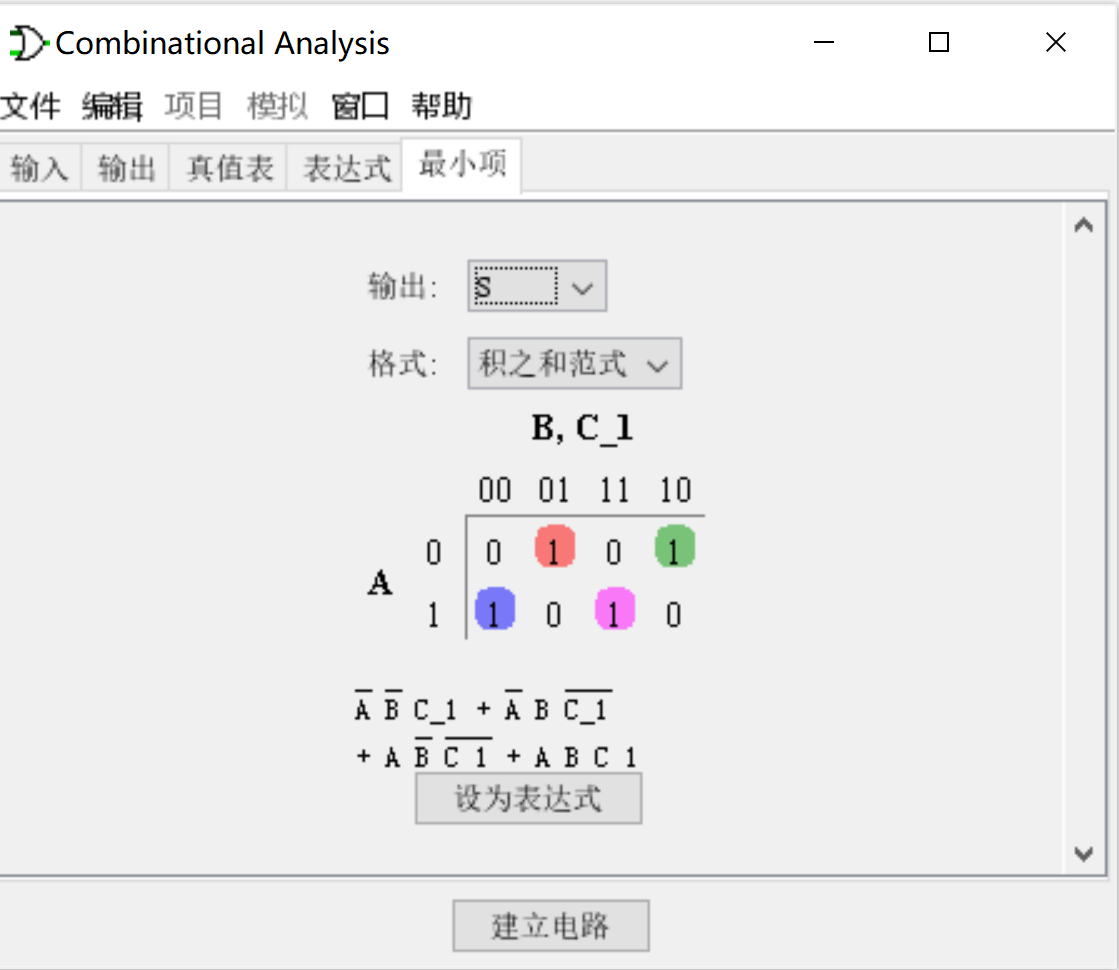

自动生成电路

左上角->项目->分析电路

优点

- 根据真值表或逻辑表达式,自动方便,避免手绘

- 生成电路相对美观

缺点 - 仅支持组合逻辑

- 输入引脚限制8个以内,输出引脚限制12个以内,且仅支持1位引脚

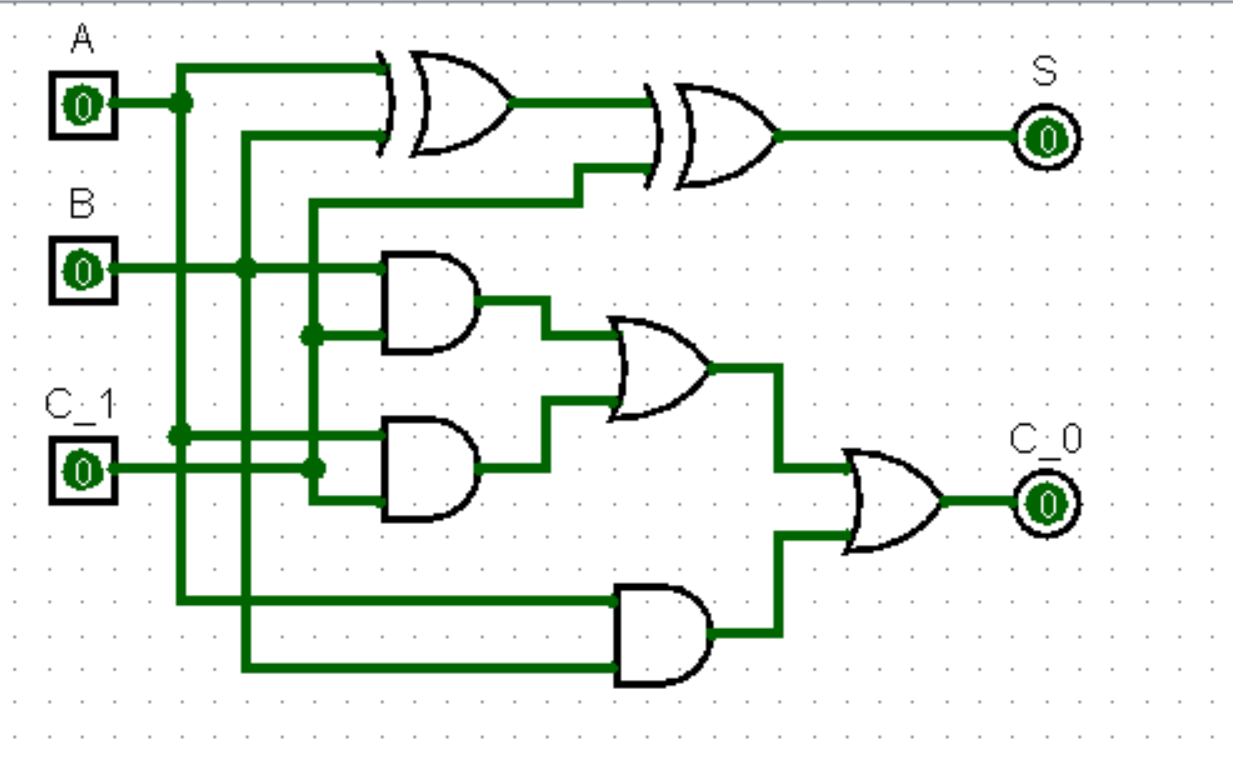

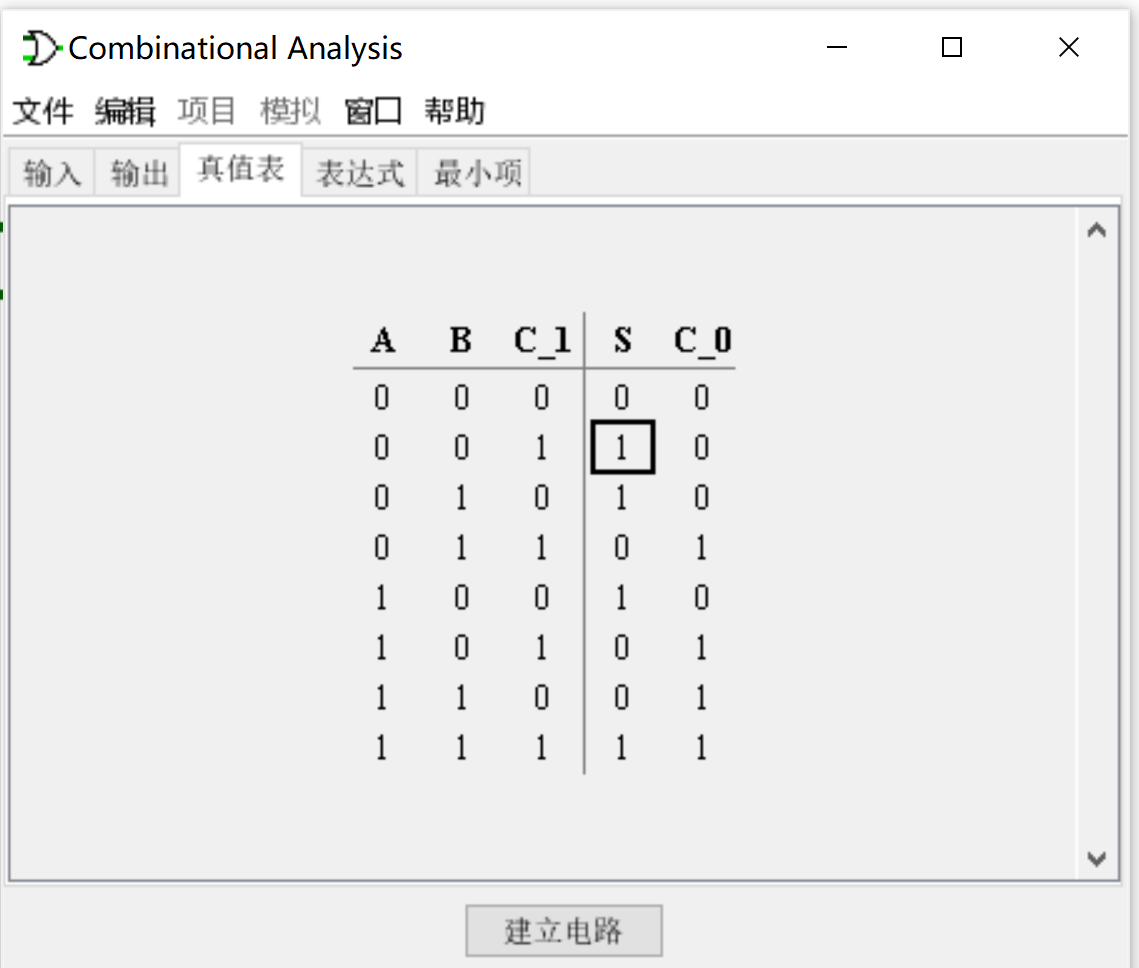

举个例子:利用分析电路实现全加器

全加器简介:利用两个1位二进制数进行相加求和,考虑来自低位的进位,并向高位进位的逻辑电路

输入:3个,参与运算的二进制数A、B,低位进位C_1

输出:2个,和S,进位C_0

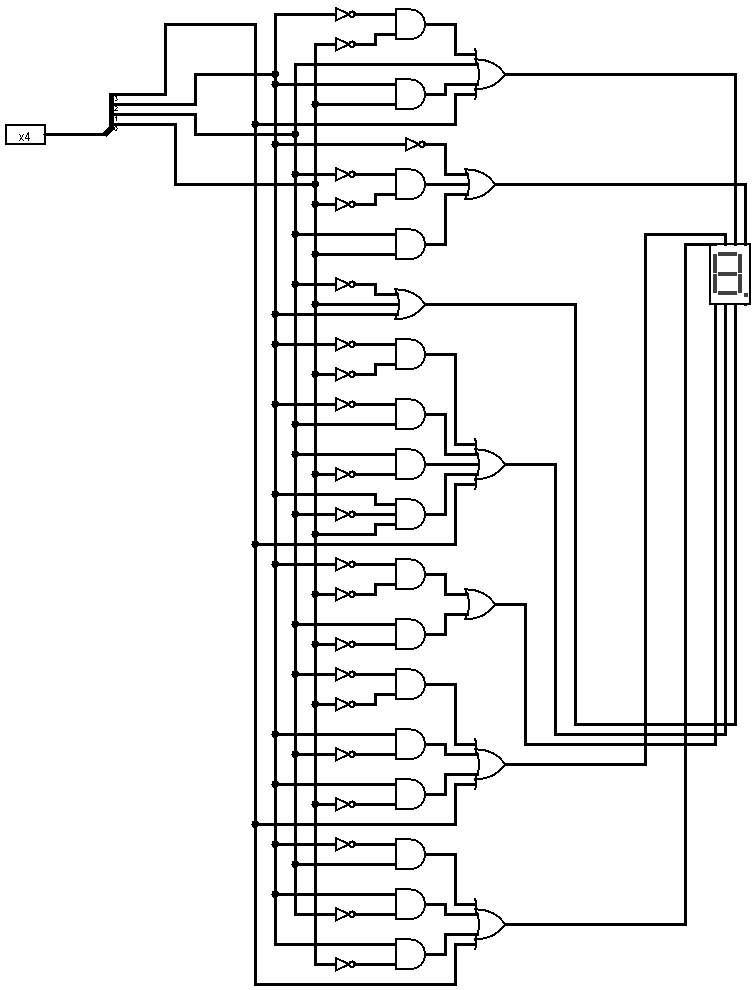

实例2:利用卡诺图实现的七段数码管

虽然自己使用手绘卡诺图分析也能做,但是不仅耗费的时间长,而且伤眼睛,现在利用自动生成电路来设计,速度快还方便(大约花了5-6分钟的样子)

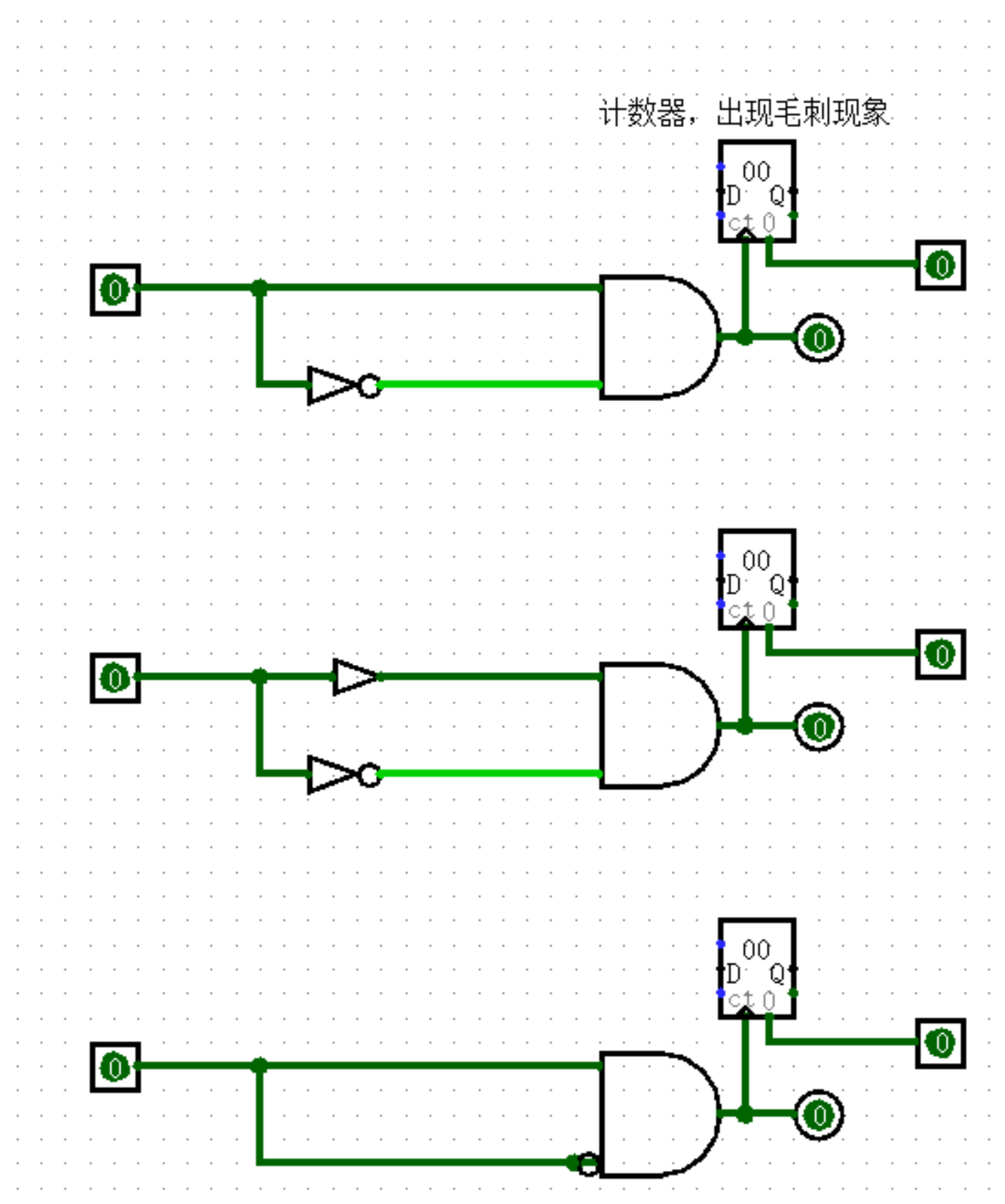

毛刺现象

Plus:logisim中的仿真环境下,所有组件的延迟是相同的

- 开启信号模拟的状态下可以添加计数器来观察毛刺现象

- 关闭默认启用的信号模拟

- 开启单步传递,ctrl+I快捷键观察信号在线路上的具体传输过程

如何避免

解决效果

- 在最短路径通路上添加一个缓冲器(起到一级延迟的作用)

- 直接将非门集成到与门中去

如何集成?

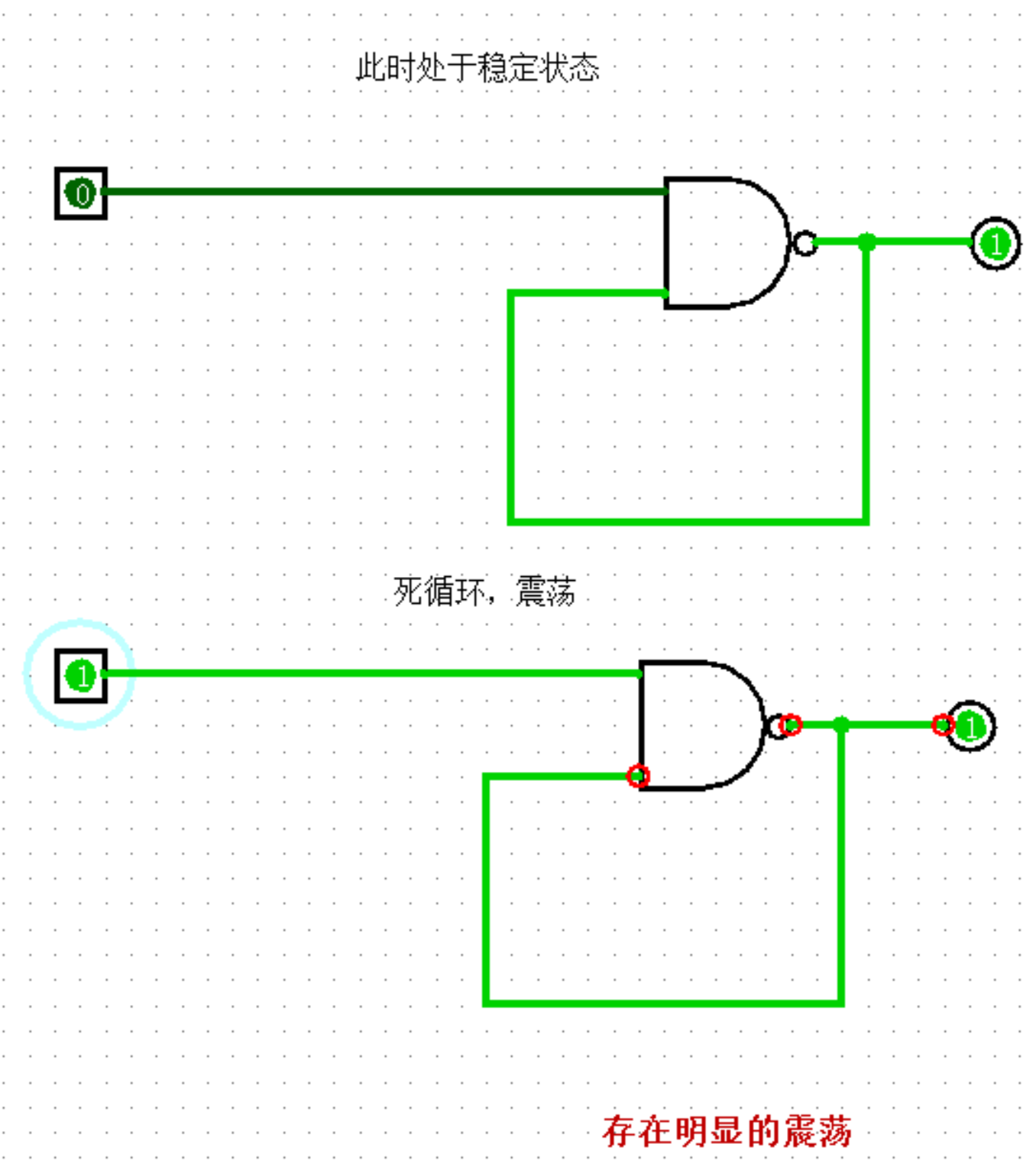

震荡现象

死循环:单位时间内信号传递达到logisim的阈值

plus:震荡情况下,logisim自动关闭信号模拟转为单步传递(为了保护仿真防止其陷入死循环),电路还能正常工作只是存在了明显的震荡

logisim自带组件介绍

基本器件介绍

-

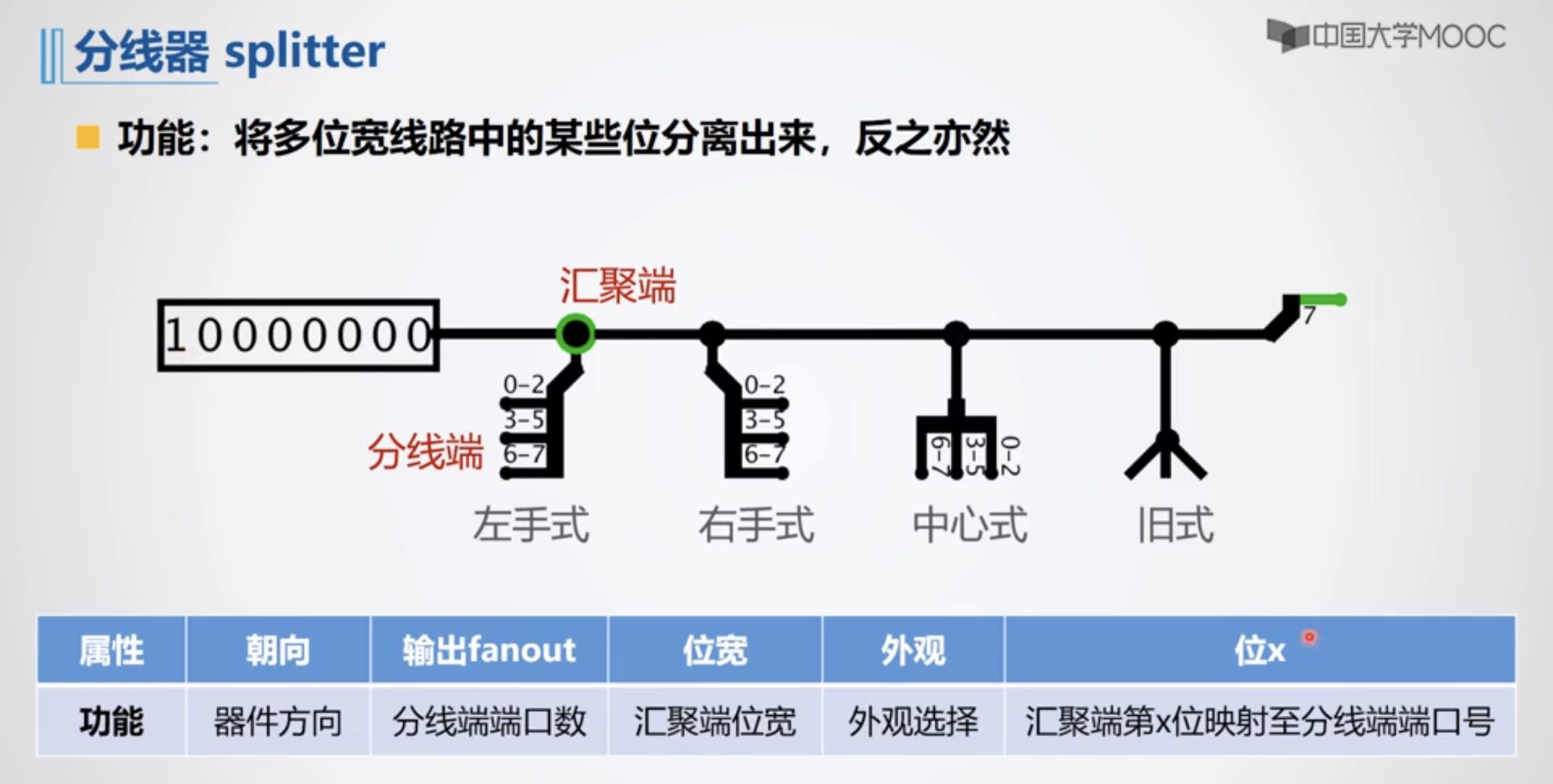

分线器:将多位宽线路中的某些位分离出来,反之亦然(合并)

Attention!分线器并不是一个逻辑功能部件,所以它没有时间延迟、方向特性

-

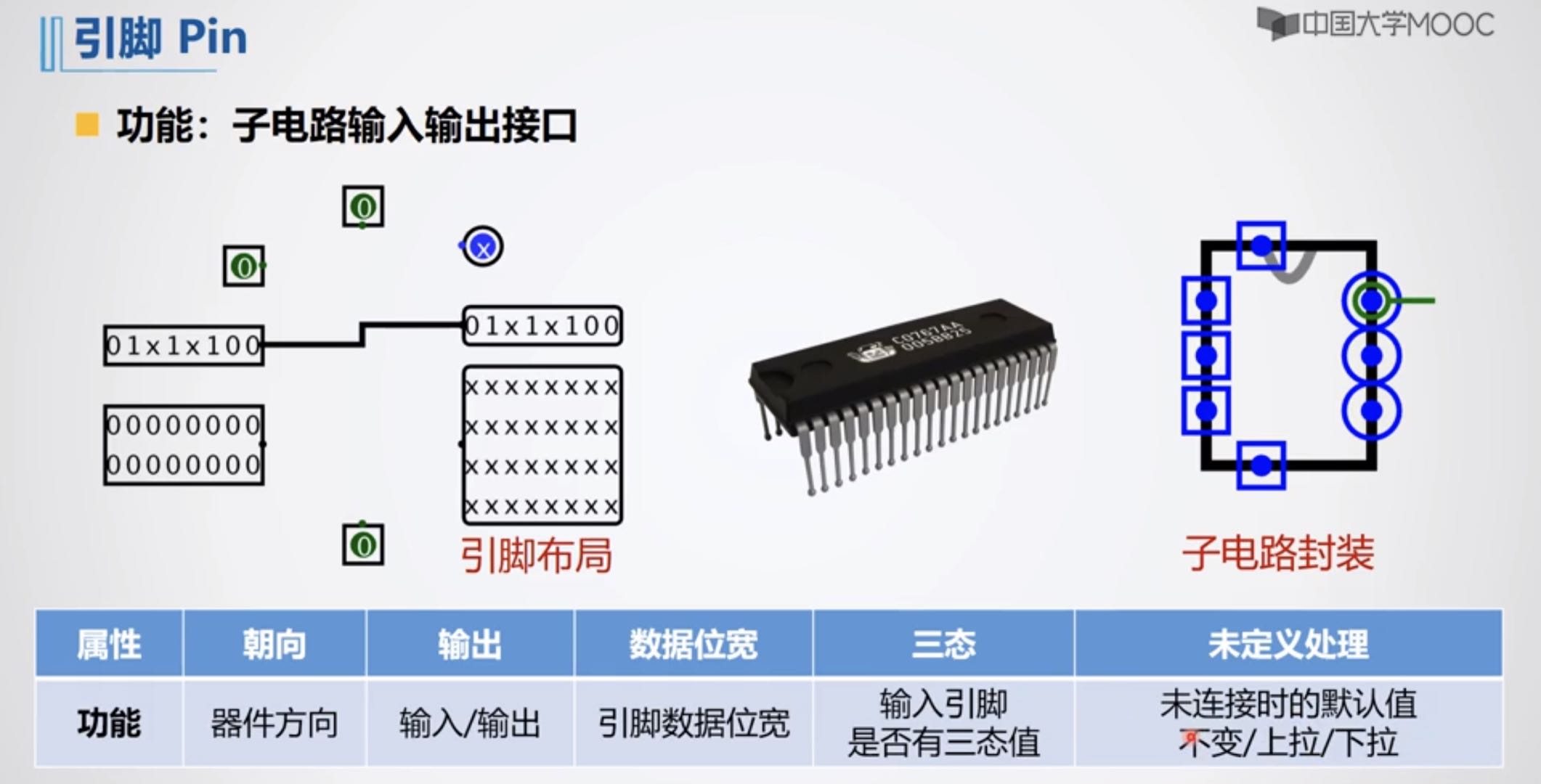

引脚:输入输出

-

探针:动态监测线路值(可以通过设置属性来显示不同格式的值)

比较简单就不贴图了 -

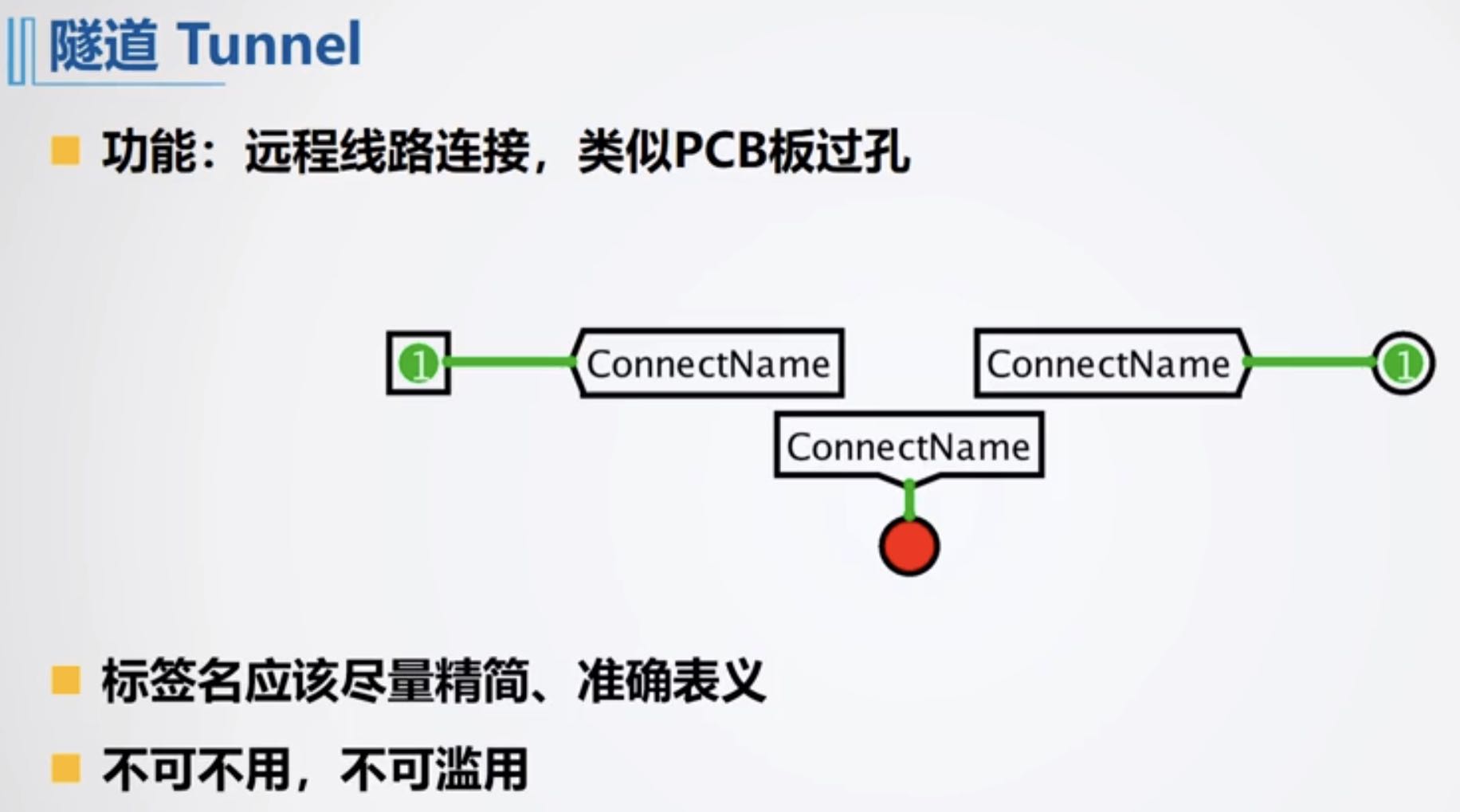

隧道:远程线路连接,类似PCB板过孔

解决了组件之间远距离连接和被遮挡组件之间的连接问题不可不用:不用的话各种线路连接过于复杂

不可滥用:滥用的话各种元器件之间的关系不够清晰

-

-

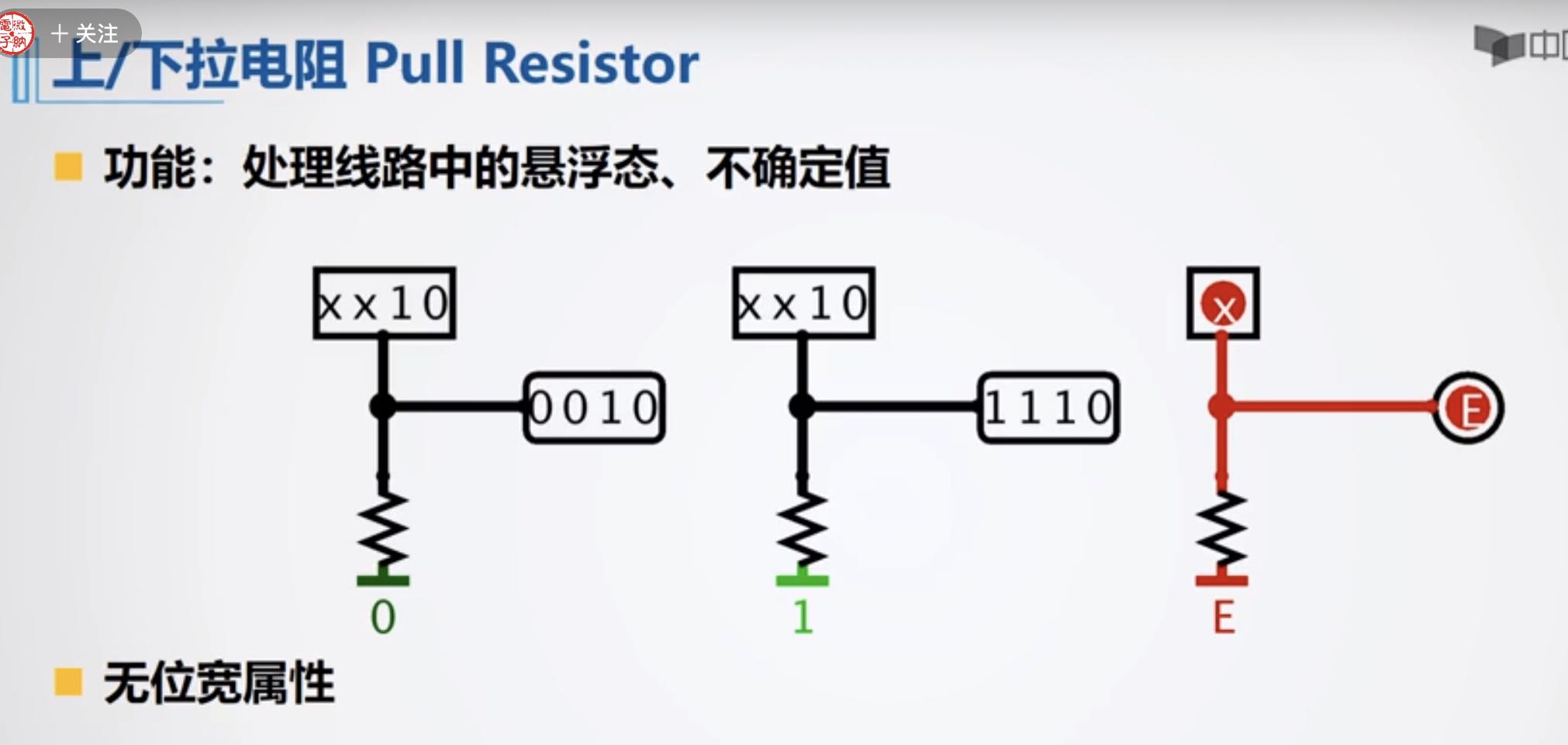

上/下拉电阻Pull Resistor:处理线路中的悬浮态、不确定值(感觉比较鸡肋?)(之前试了一下,比较容易出bug,不过还是挺有用的)

-

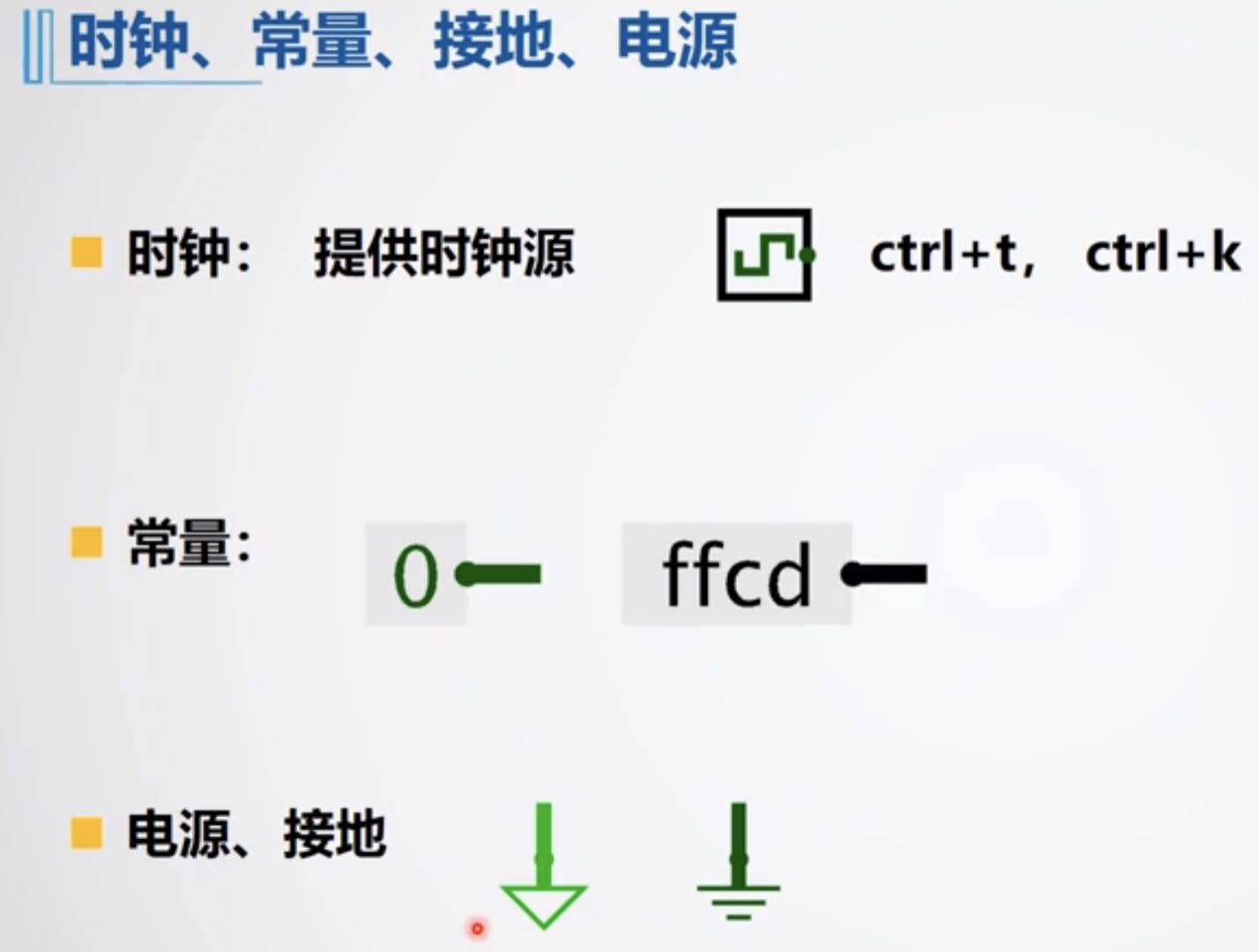

时钟、常量、接地、电源

时钟:logisim中提供时钟源,可以直接使用鼠标修改值,也可以利用快捷键ctrl+t修改,还可以使用ctrl+k使时钟源按照你的设定频率不断翻转

常量:可以在设置面板中选择常量的位宽和值(非常有用,因为它可以替代一个输入)

电源、接地:就是两个特殊的常量1 0

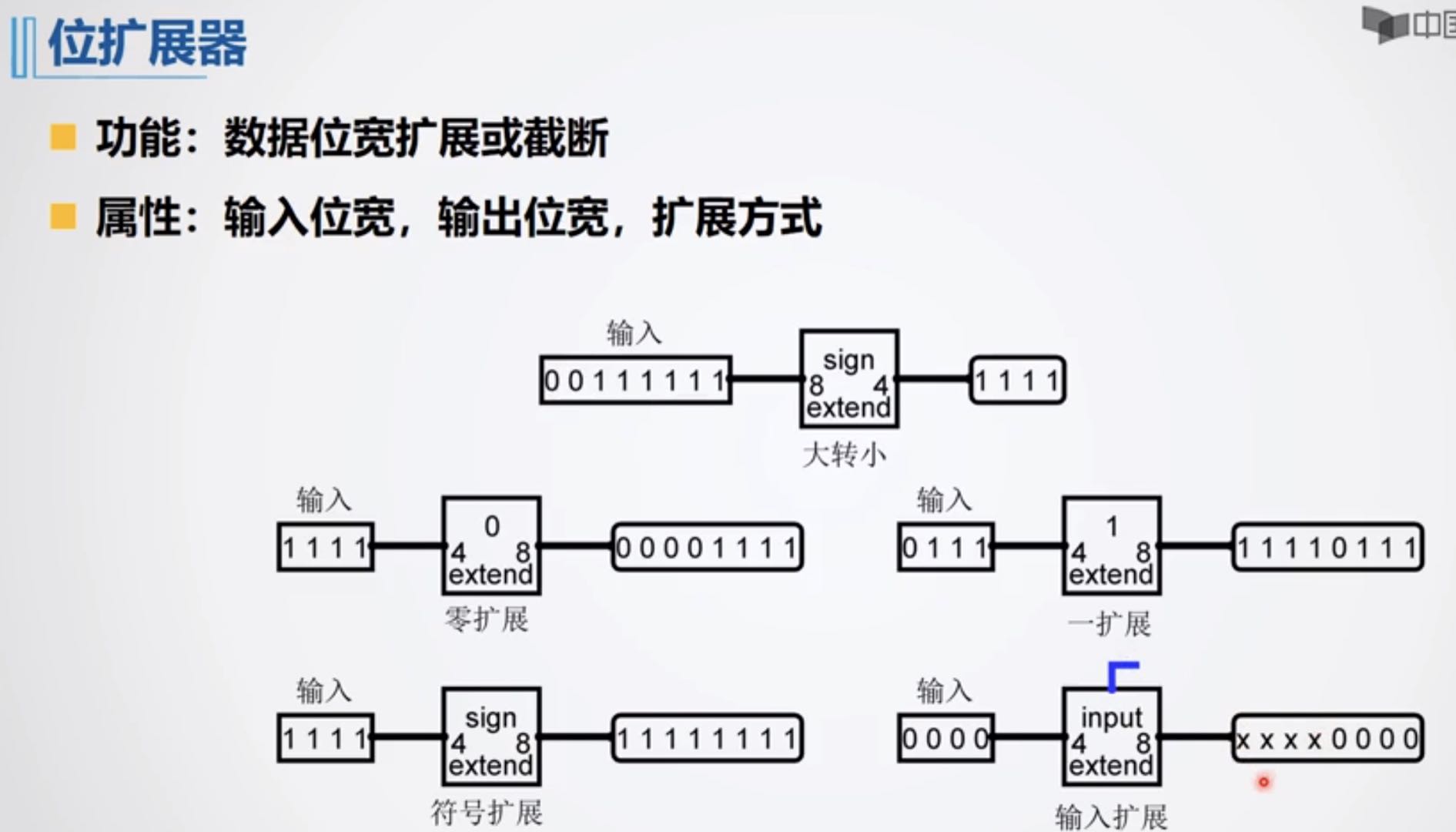

- 位扩展器:数据位宽扩展或截断(以低位为主)

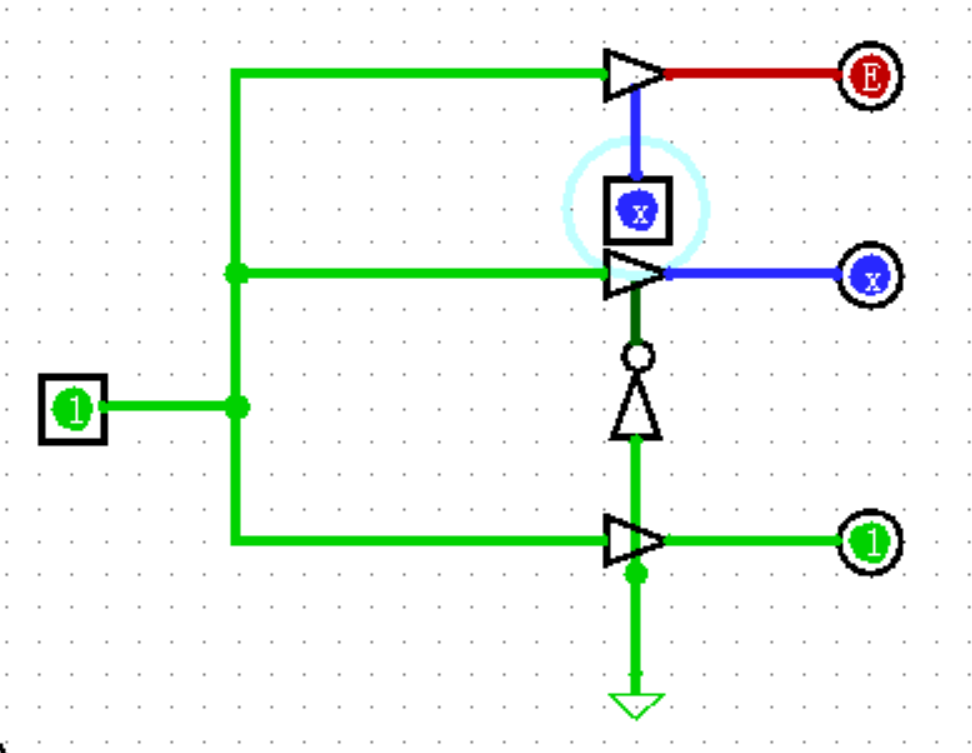

- 三态门(三态缓冲器):控制开关,用于总线传输方向的控制

(经过验证)

使能端置为高阻态x,输出为Error

使能端置为True,正常输出

使能端置为False,输出为高阻态x

复用器库主要组件

- 多路选择器(数据选择器Multiplexer)

- 解复用器(Demultiplexer)

- 解码器(译码器Decoder)

- 优先编码器(Priority Encoder)

- 位选择器(Bit Selector)

- 多路选择器:使能端为1或无使能端时正常工作,使能端为0是输出为高阻态x

- 解复用器:与多路选择器恰好相反,一个输入,根据选择端决定向那个接口输出

- 解码器(将二进制解码成高低电平):通俗讲,就是最小项生成器

- 优先编码器(将高低电平编码成二进制输出)

与解码器刚好相反,以8输入优先编码器为例,优先级7->0,逐级递减,输出为优先级最高的请求编号,使能输出为1当且仅当无请求且使能端为1,使能输入端的作用则和之前元器件里的类似

(plus:使能输出可以使两个优先编码器级联起来,前一个使能输出为1,可以作为下一个优先编码器的使能端,继续进行判断)

运算器库常用组件介绍

-

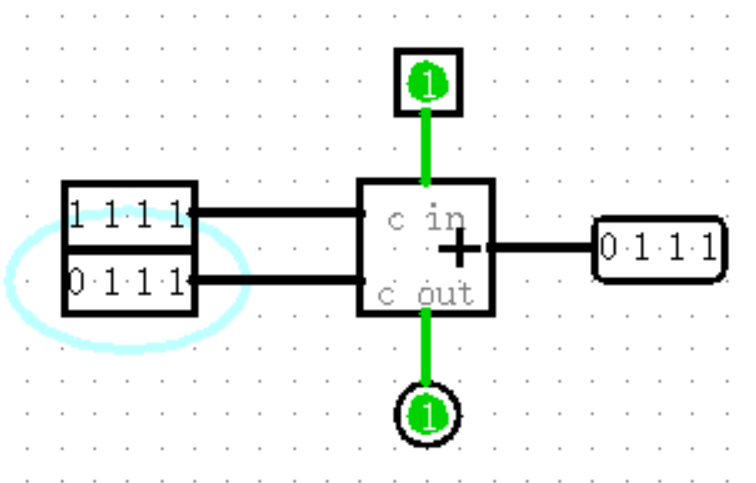

加法器:是有符号数的加法,和全加器类似

-

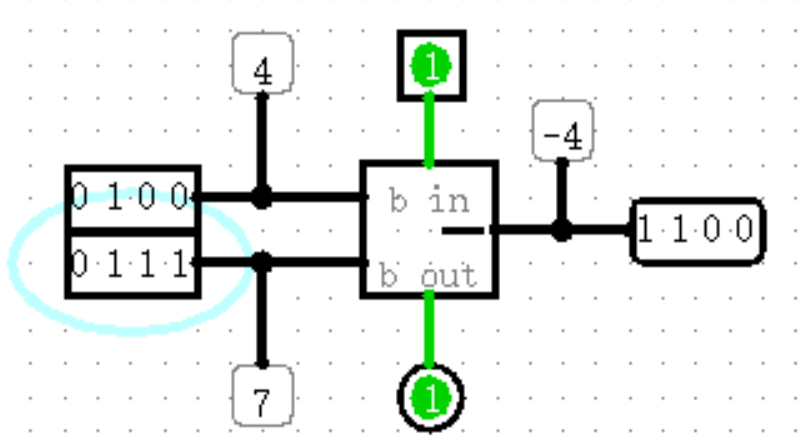

减法器:有符号数,和加法器类似(b in为1借位,b out为一位借位)

-

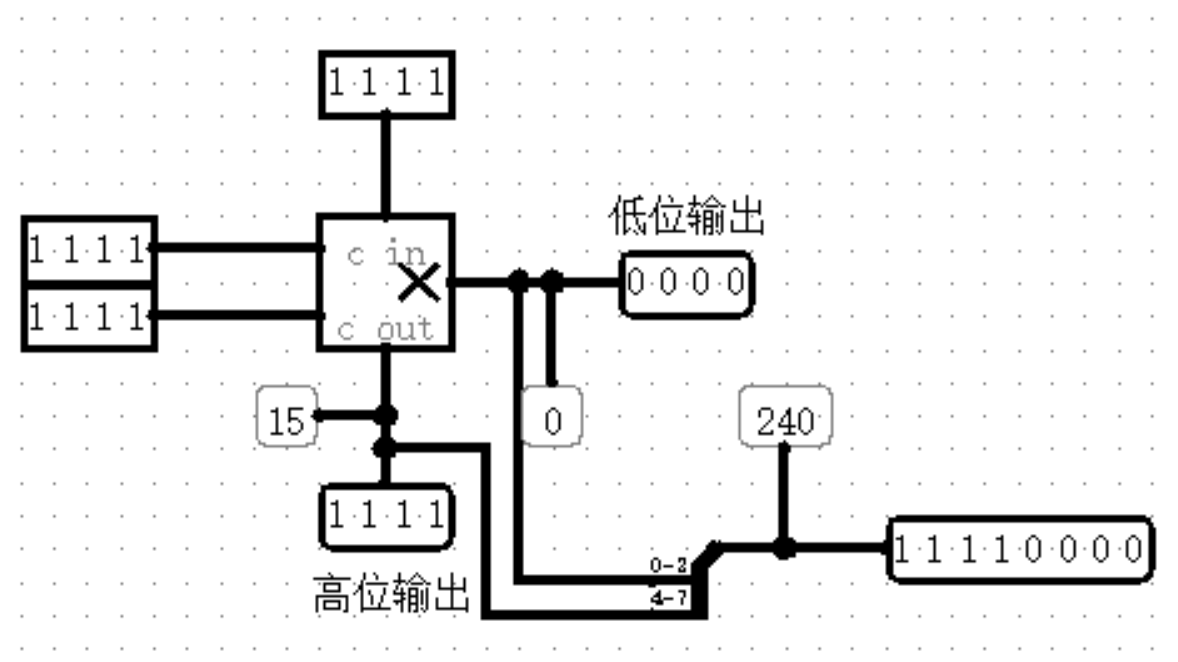

乘法器:无符号数乘法器,因为乘数和被乘数相乘得到的结果是2n位,所以分别存放在乘积低位和乘积高位

-

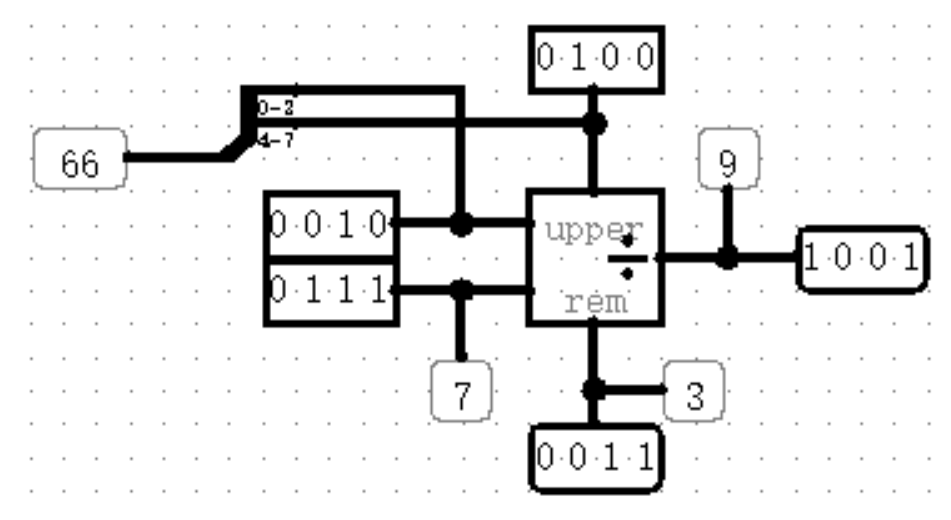

除法器:无符号,与乘法器类似

-

补码器:功能如其名,但是存在特例,如-128的补码应该是128,但是八位二进制无法表示128(补码的补码是原码)(过于简单就不贴图了)

功能比较特别,输入一个数,输出的是该数相反数的补码

-

比较器:比较大小,分为无符号和有符号

-

移位运算器:分为逻辑右移、算数右移(补符号位)、逻辑左移、循环右移/左移这些方式

存储库

总览

[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-5LQlqriC-1634449833464)(D:pictures_plus存储库基本组件.png)]

-

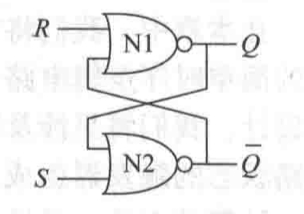

RS锁存器:最基础的锁存器,直接上图(缺点是输入R=S是无法确定输出状态),Set、Reset

-

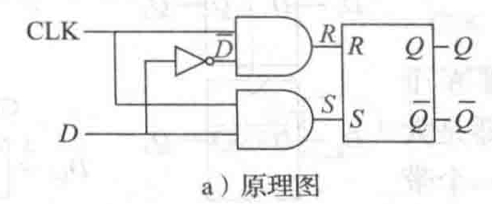

D锁存器:D锁存器是RS锁存器的修改版,包括时间输入端CLK和数据输入端D,还有通用的使能端(当输入为0时,忽略时钟输入)、异步重置01端,重置输出Q为1

有关异步重置和同步重置的区别

异步重置:无条件重置(电频敏感信号)

同步重置:只有当CLK处在时钟沿时,才触发重置

-

触发器:以D触发器为例,由两个RS锁存器构成,一个主锁存器,一个右锁存器

D锁存器和D触发器的区别在于,只要CLK=1,D锁存器就会不断根据输入D更新输出Q的状态,而D触发器只有在时钟沿时才会更新输出状态

-

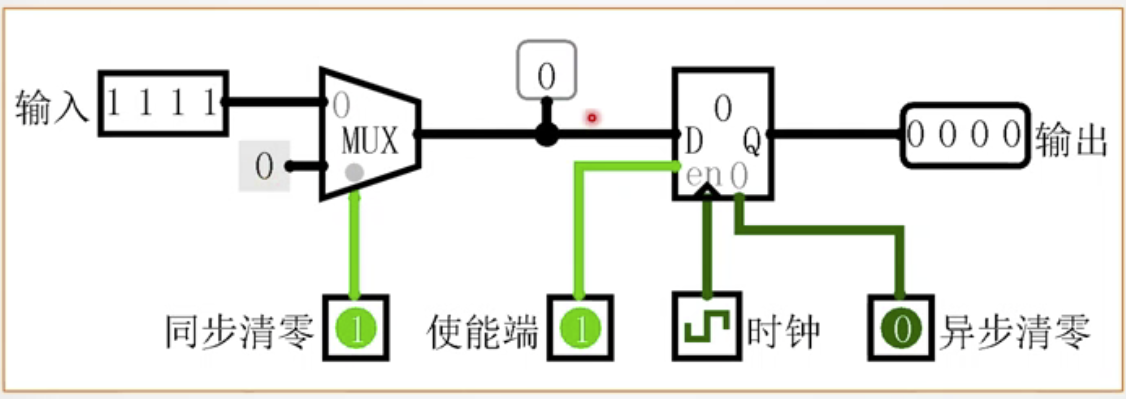

寄存器:由多个D触发器并行构成的组件,共用一个时钟元件CLK

内部原理

logisim封装

-

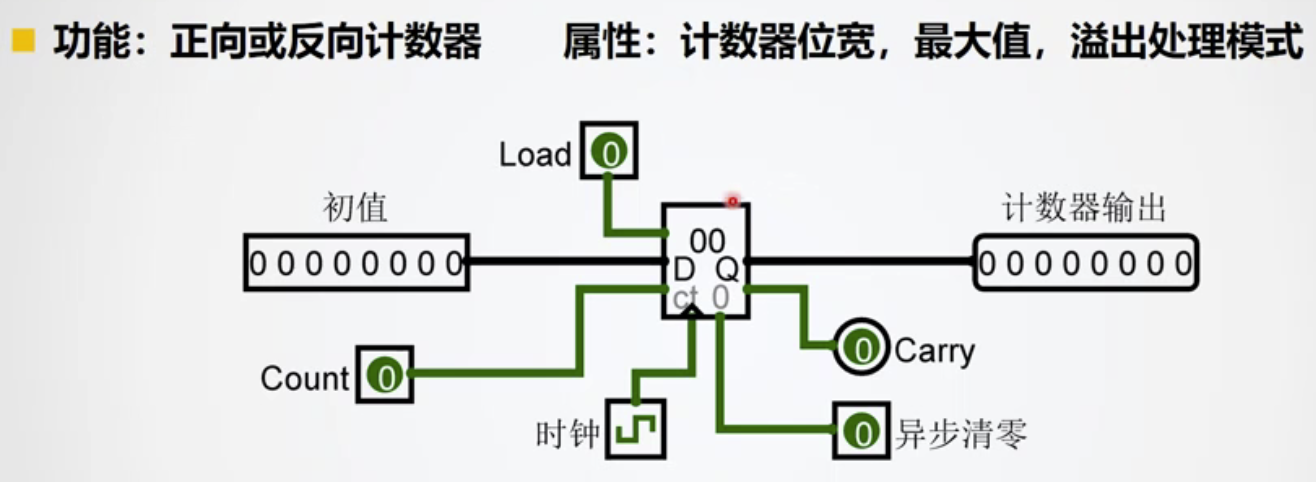

计数器(Counter):组成实验里用于对cpu时钟周期进行计数,甚至可以在cache实验里做淘汰算法的访问次数计数

四个输入:加载、数据、计数、时钟

- 数据=加载=0,计数=1,正常计数

- 加载=计数=1,反向计数

- 数据!=0,计数=0,加载=1,将数据加载到输出,此时再将计数修改为1,即开始倒计时(类似)

-

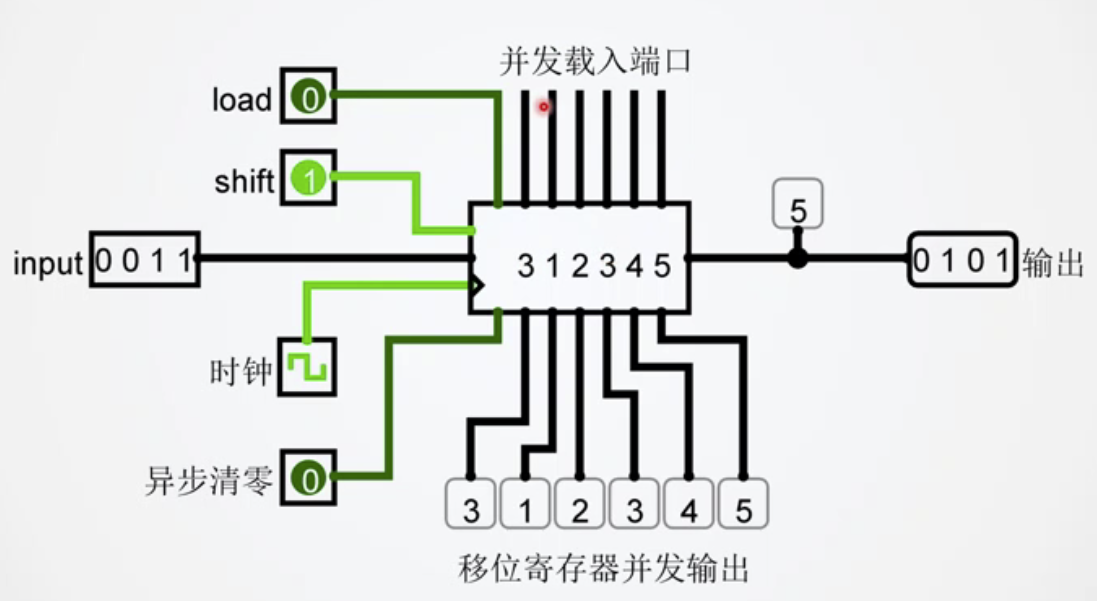

移位寄存器

功能:存储代码+移位+串行-并行转化+数值运算

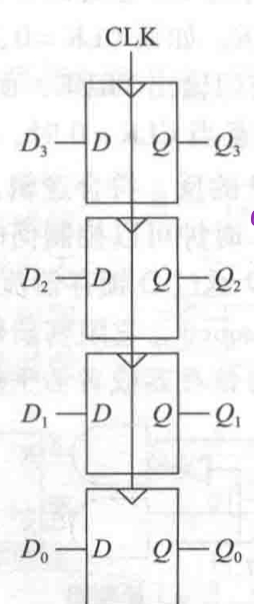

实现方式:多个D触发器并行连接即可,共用一个时钟,并且前一个数据输出作为下一个的数据输入

原理:移位从CLK上升沿到输出端新状态的建立需要一段时间,但是由于所有D触发器的时钟为并行连接,所以从 Q n Q_n Qn到 D n + 1 D_{n+1} Dn+1,输出端的输出还未改变,但是已经处于上升沿,所以前一个D触发器的输出就顺理成章的成为了下一个D触发器的输出,于是乎数据整体右移(要实现数据整体左移也简单的很,将 Q n + 1 Q_{n+1} Qn+1与 D n D_n Dn反向连接即可)

原理实现(以右移寄存器为例)

logisim

shift控制信号为1时,每出现一个时钟沿,数据右移一位,并将输出的数据传入

load为1,shift为0是,每出现一个时钟沿,将预先定义好的数据并发的载入端口中

-

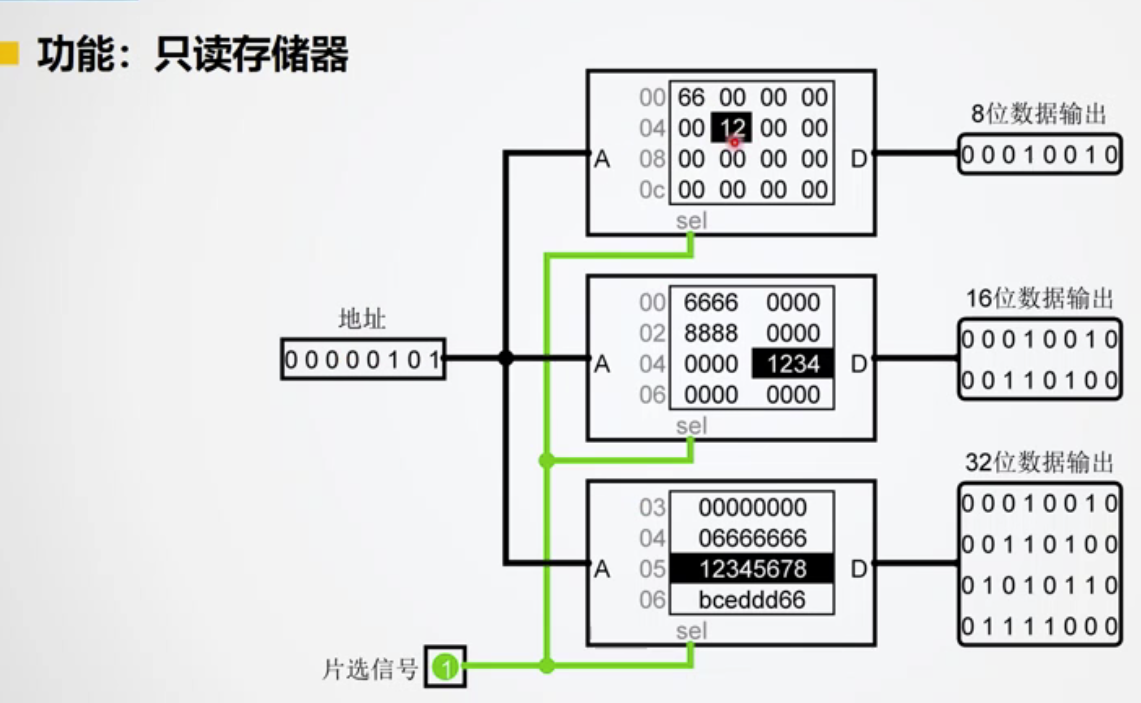

ROM(Read Only Memory):只读存储器

操作还是很通俗易懂的,就是输入地址然后根据地址输出对应数据,注意最好不要直接在元器件里面修改值,容易出bug,还有选择不同的位数,生成的存储器外观上也不太一样

-

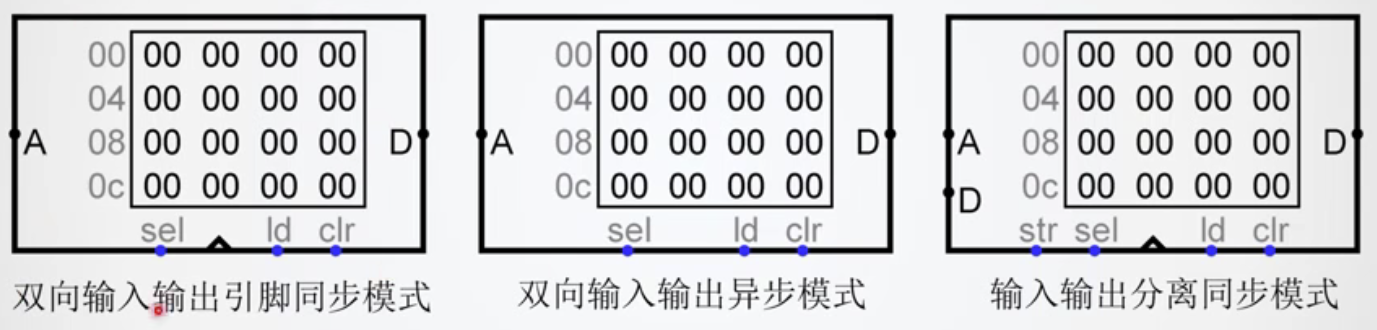

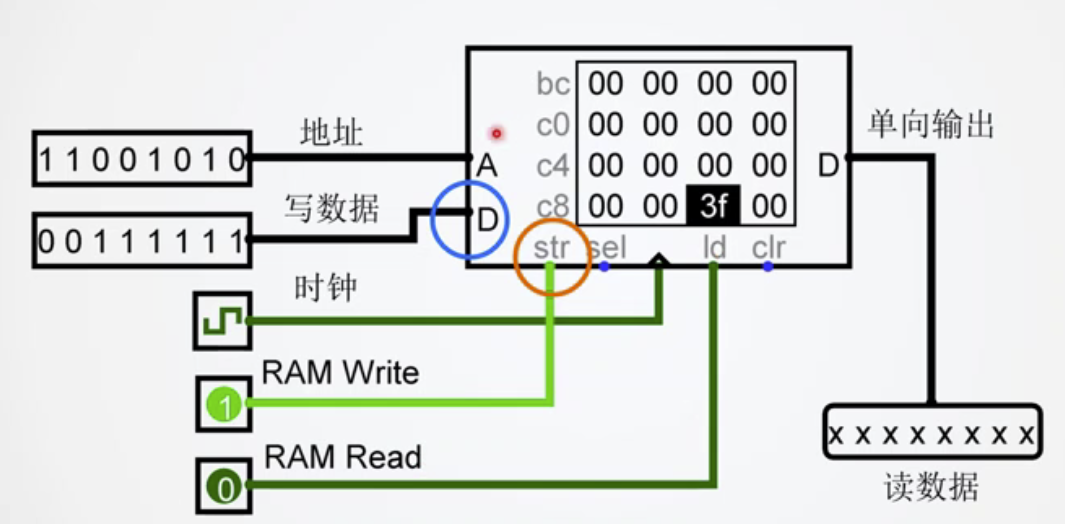

RAM(Random Access Memory):可写随机存储器

四种模式

D引脚是唯一一个既可以作为输入端又可以作为输出端的引脚

双向输入输出引脚同步模式:需要时钟信号

双向输入输出引脚异步模式:可以直接在电频信号的作用下输入输出

输入输出分离同步模式:左侧输入,右侧输出,在logisim中使用较多D

双向输入输出同步模式:注意读写数据地址共用(clr是异步重置内存),当写使能为0是,根据地址从RAM中读取数据,为1时,三台缓冲器使能,id置0,向地址中写入数据

对比之下,就可以看出分离模式的结构有多简单了

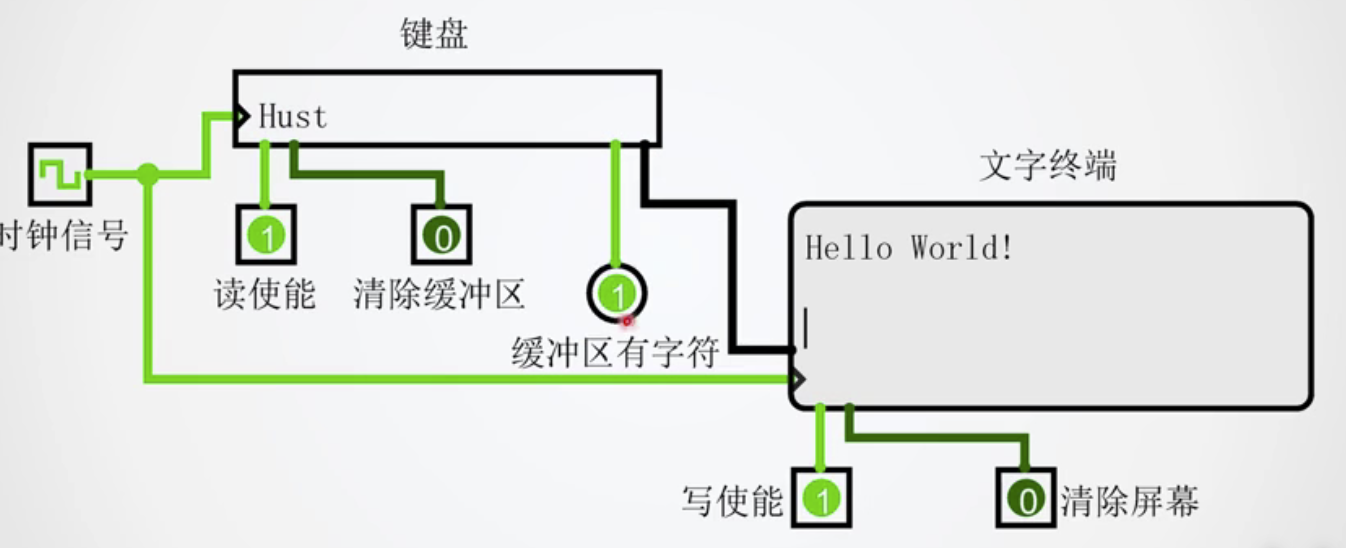

输入输出库

输入输出库常用组件

-

键盘、哑终端:非常有意思的读写组件

可以使得电路直接接受计算机输入的值,输入后,ASCII将存储在键盘组件的缓冲区中,当读使能置为1是,每出现一个时钟沿,缓冲区最左侧(最先键入的ascii字符)就会被读取到输出端输出

plus:可以接受ascii字符,但是无法输入中文

-

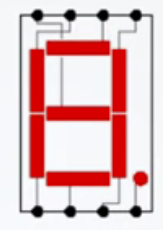

七段数码管:之前有实例涉及到过,比较熟悉(注意一下内部引脚的连接)

-

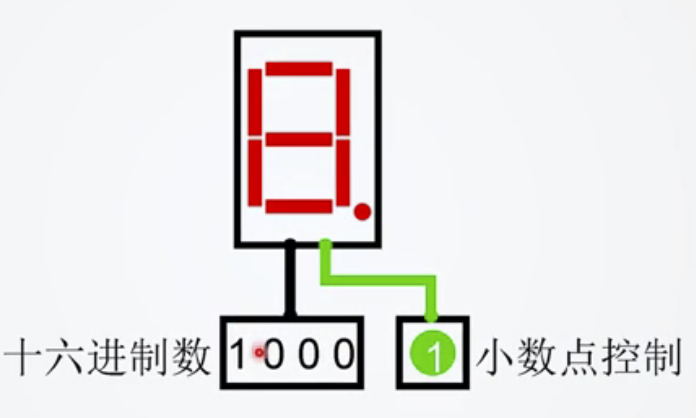

十六进制数码管:更加常用

-

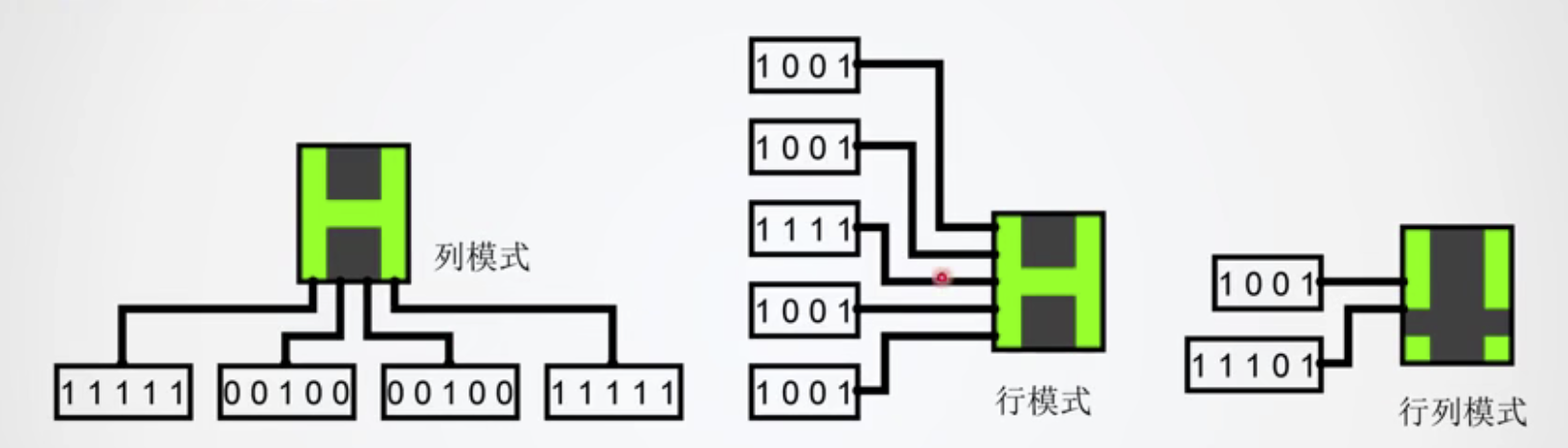

LED矩阵:分为行模式、列模式、行列模式(可以用于复杂图形显示、显示一个汉字的值等)

一些概念问题

高低电频有效的概念

高低电频有效表示给电路施加某电频是,电路功能被触发

For Example:输入低电平有效,表示你输入信号为低电平是,电路触发,为高电平时则不触发

输出时也是同理,假设某数据选择器输出无符号数为

10011,如果此时是输出高电平有效,该输出值就是19,如果是低电平有效,该输出值就是12

拓展:为什么为什么一般推荐使用低电平有效?

- 因为低电平时电路的阻抗低,噪声造成的电平变化小,也就是说,抗干扰能力更强。换句话说:低电平有效时干扰把它变成高电平,比高电平有效时干扰把它变成低电平要困难。就是因为低电平阻抗低,所以说低电平有效抗干扰能力强。

在数字系统中,比较容易出现在低电平上叠加一个噪声正脉冲。如果采用高电平有效的方式,就可能在无效的低电平上,出现高电平噪声,从而使某个信号在不应当有效的时候,出现有效的高电平。所以在数字系统中,大多数信号的有效电平为低电平。 - 该段解释引用自CSDN博主「Aslier」的原创文章,遵循CC 4.0 BY-SA版权协议,转载请附上原文出处链接及本声明。

原文链接:https://blog.csdn.net/a419116194/article/details/103238872

最后

以上就是健忘金针菇最近收集整理的关于logisim基本组件介绍Logisim基本组件介绍的全部内容,更多相关logisim基本组件介绍Logisim基本组件介绍内容请搜索靠谱客的其他文章。

发表评论 取消回复