写在前面

- 版权:原题地址,点击直达。

- 这个专栏的内容记录的是Verilog题库刷题过程,附带RTLTestBench,并进行

代码覆盖率收集。- <刷题记录>专栏,持续打卡中…

文章目录

- 一、题目

- (1)题目描述

- (2)端口描述

- 二、分析

- 三、RTL

- 四、Testbench

- 五、结果分析

- (1)TB结果

- (2)波形图

- (3)覆盖率

一、题目

(1)题目描述

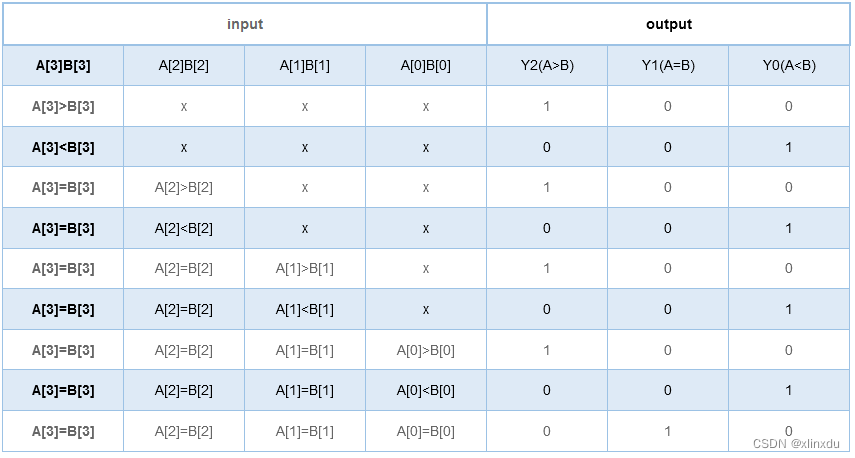

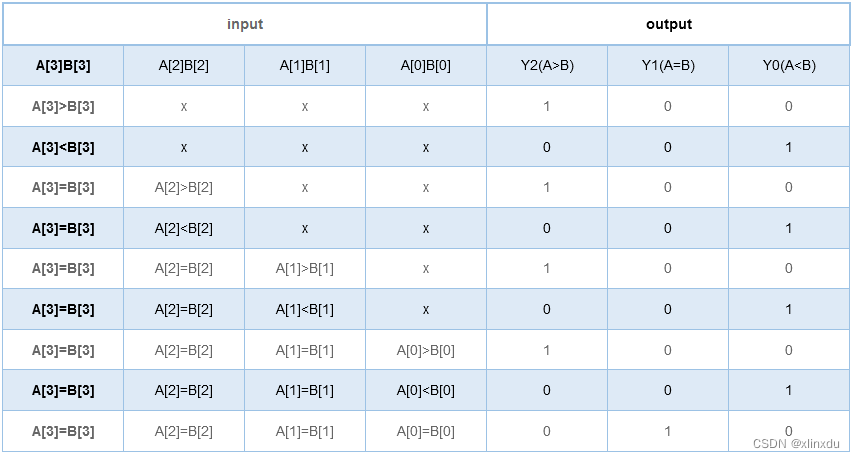

某4位数值比较器的功能表如下。请用Verilog语言采用门级描述方式,实现此4位数值比较器。

(2)端口描述

| 信号 | 方向 | 类型 | 位宽 | 描述 |

|---|---|---|---|---|

| A | input | wire | 4bit | 输入的4位数据A |

| B | input | wire | 4bit | 输入的4位数据B |

| Y2 | output | wire | 1bit | 输出信号Y2,A>B |

| Y1 | output | wire | 1bit | 输出信号Y1,A=B |

| Y0 | output | wire | 1bit | 输出信号Y0,A<B |

二、分析

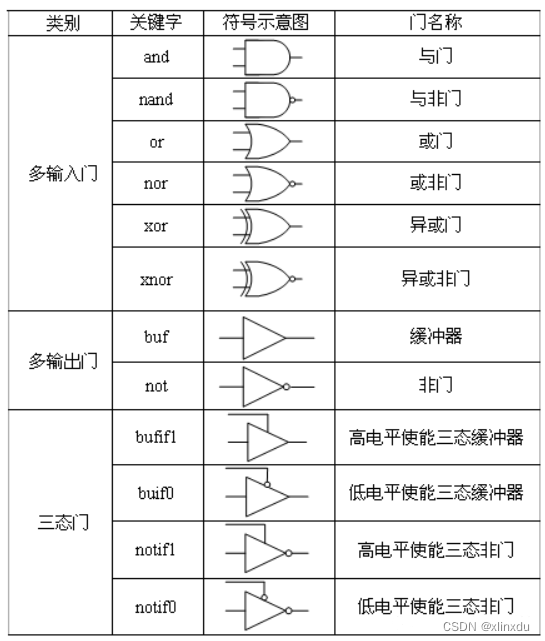

首先得知道门级单元是什么,怎么用,如上表。

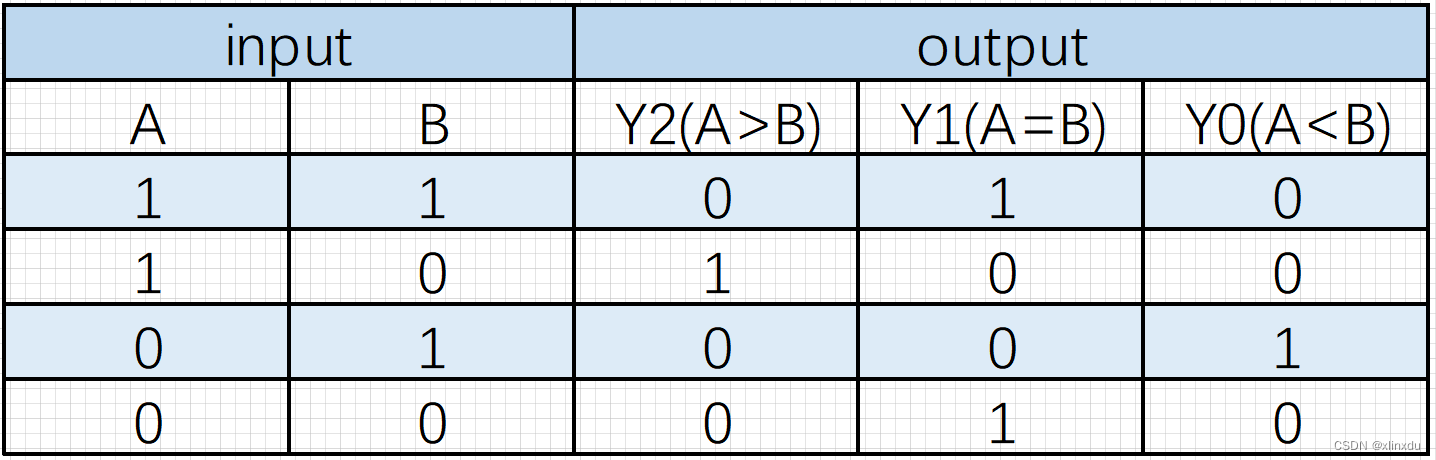

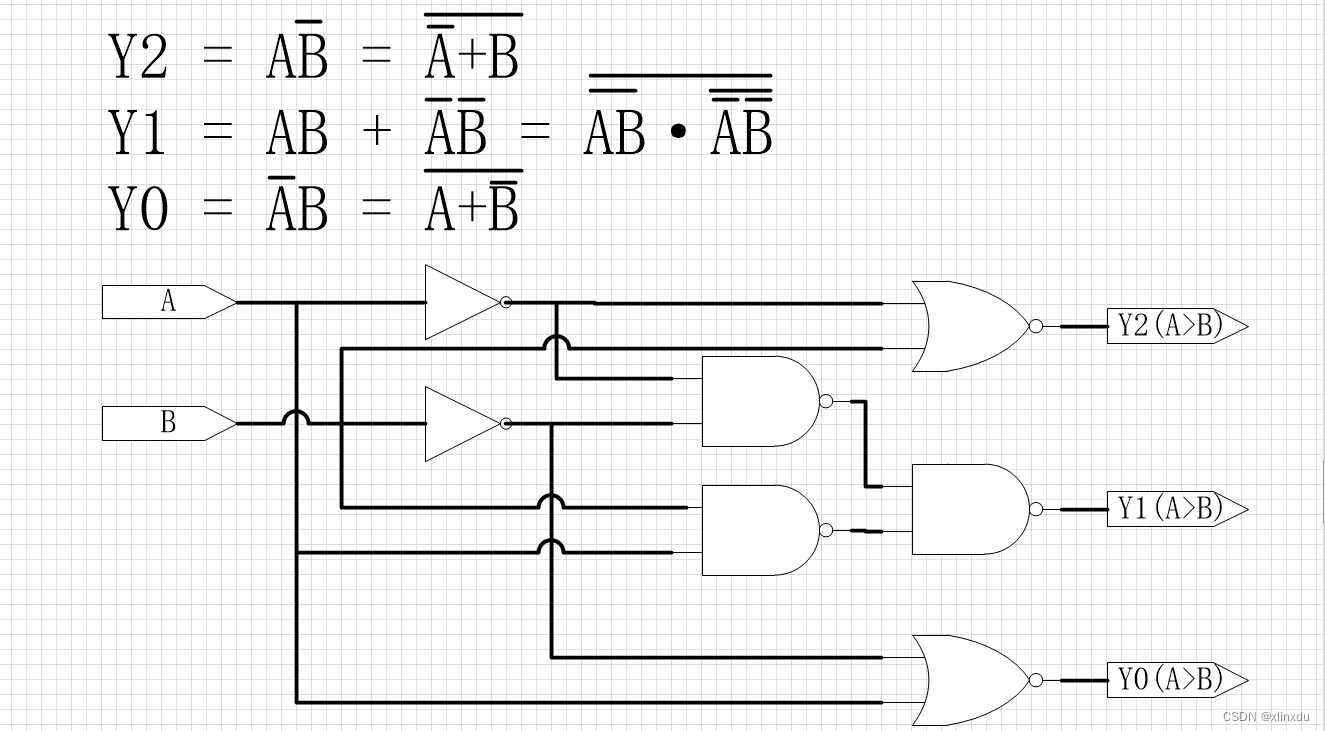

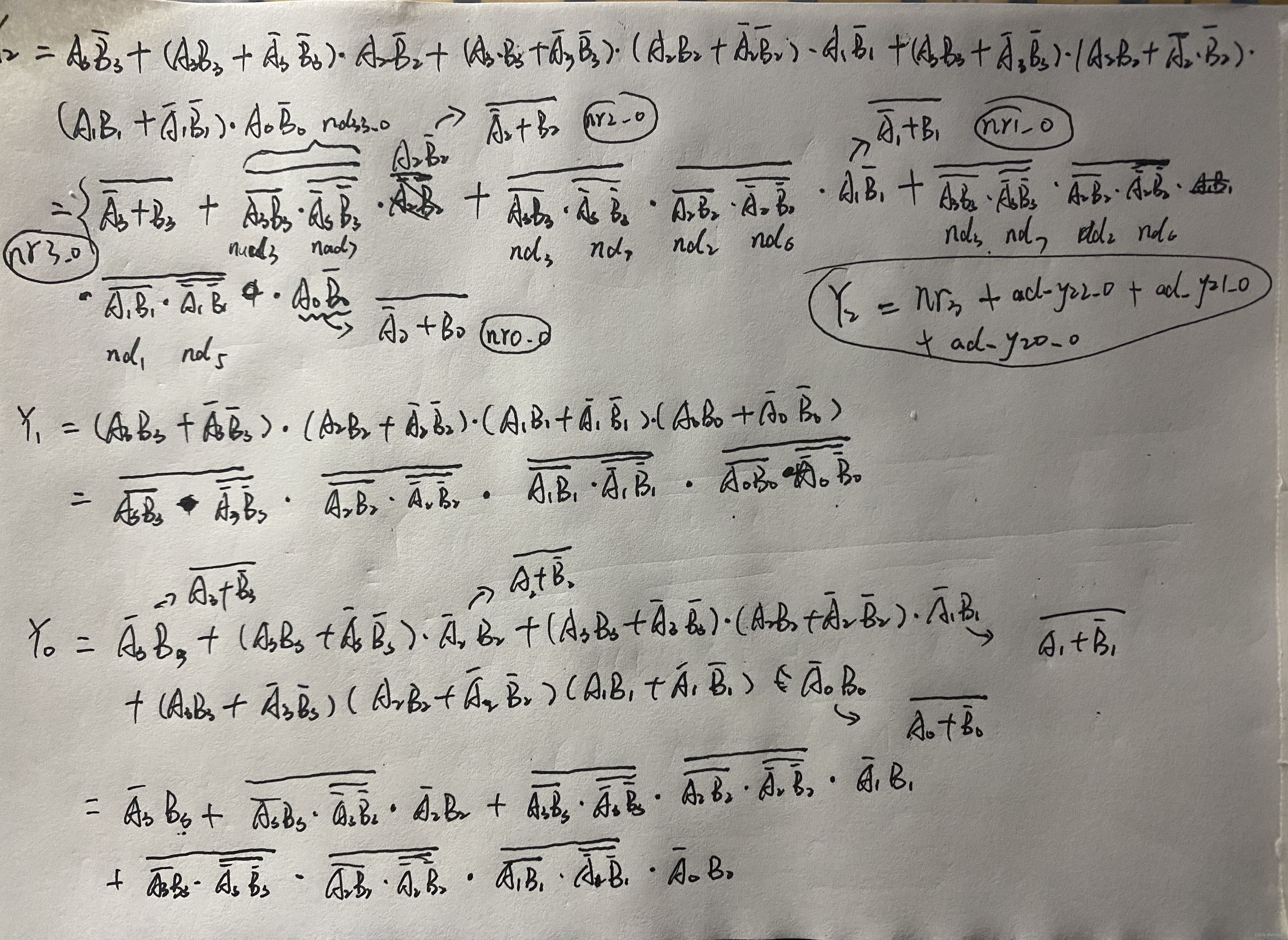

其次得了解1位比较器的构成。写真值表,写逻辑表达式,化简、变形等。这里全部转换成与非-与非 or 或非-或非模式。

为什么用与非-与非 or 或非-或非呢。因为在集成电路中,与非门和或非门所用资源仅次于非门。

在CMOS电路(互补的pMOS和nMOS)实现组合逻辑门。非门(inv)消耗1个pMOS+1个nMOS;2输入与非门(nand2)和2输入或非门(nor2)均消耗2个pMOS+2个nMOS;2输入与门(and2)和2输入或门(or2)则是在nand2和nor2后面再接inv得到,需要3个pMOS和3个nMOS。

从资源的角度来说,and和or反而不如nand和nor。与非门比或非门性能好.

CMOS工艺中pMOS的导通能力比nMOS差,对比nand2和nor2的结构,可以发现nand2中pMOS是并联,nMOS是串联,所以性能差的单个pMOS输出“1”的能力恰好匹敌2个串联nMOS输出“0的”能力,而nor2则反过来,pMOS串联,nMOS并联,对于导通能力差的pMOS来说是雪上加霜,通常需要大幅度增加nor2中的pmos的宽度才能和nmos匹敌,但是MOS管尺寸的增加会占用更多的面积且造成更大的寄生电容。

总之与非门,不管是几输入,都比和其对称的或非门要更优秀。但并不是说对于一个确定的组合逻辑,全部使用与非门来凑就是最优,比如说一个nor2无论如何也比用一个nand2加3个inv要好。

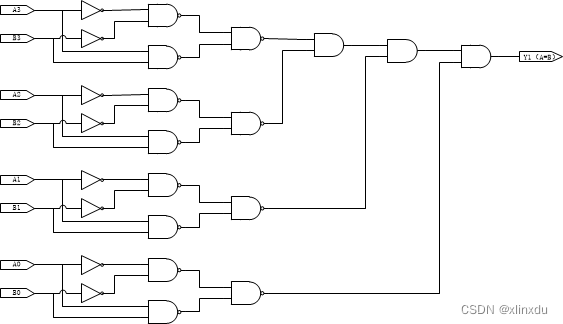

三、RTL

module comparator(

input [3:0] A ,

input [3:0] B ,

output wire Y2_o , //A>B

output wire Y1_o , //A=B

output wire Y0_o //A<B

);

//-- ~A and ~B

//-- not name(output,input)

not inv0(iv0_o, A[0]),

inv1(iv1_o, A[1]),

inv2(iv2_o, A[2]),

inv3(iv3_o, A[3]),

inv4(iv4_o, B[0]),

inv5(iv5_o, B[1]),

inv6(iv6_o, B[2]),

inv7(iv7_o, B[3]);

//--

//-- nand name(output,input list)

nand nad0(nad0_o, A[0], B[0]),// ~(A0B0)

nad1(nad1_o, A[1], B[1]),// ~(A1B1)

nad2(nad2_o, A[2], B[2]),// ~(A2B2)

nad3(nad3_o, A[3], B[3]),// ~(A3B3)

nad4(nad4_o,iv0_o,iv4_o),

nad5(nad5_o,iv1_o,iv5_o),

nad6(nad6_o,iv2_o,iv6_o),

nad7(nad7_o,iv3_o,iv7_o);

//--

nand nad00(nad00_o,nad0_o,nad4_o),

nad11(nad11_o,nad1_o,nad5_o),

nad22(nad22_o,nad2_o,nad6_o),

nad33(nad33_o,nad3_o,nad7_o);

//--

//--

nor nr0(nr0_o,iv0_o,B[0]),

nr1(nr1_o,iv1_o,B[1]),

nr2(nr2_o,iv2_o,B[2]),

nr3(nr3_o,iv3_o,B[3]);

//--

//--

//--

nor nr4(nr4_o,A[0],iv4_o),

nr5(nr5_o,A[1],iv5_o),

nr6(nr6_o,A[2],iv6_o),

nr7(nr7_o,A[3],iv7_o);

and ad0(ad3322_o,nad33_o,nad22_o),

ad1(ad332211_o,ad3322_o,nad11_o);

and ad_Y2_y20(ad_y20_o,ad332211_o,nr0_o),

ad_Y2_y21(ad_y21_o,ad3322_o ,nr1_o),

ad_Y2_y22(ad_y22_o,nad33_o ,nr2_o),

ad_Y0_y00(ad_y00_o,ad332211_o,nr4_o),

ad_Y0_y01(ad_y01_o,ad3322_o ,nr5_o),

ad_Y0_y02(ad_y02_o,nad33_o ,nr6_o);

//-- output

or (Y2_o,nr3_o,ad_y22_o,ad_y21_o,ad_y20_o),

(Y0_o,nr7_o,ad_y02_o,ad_y01_o,ad_y00_o);

and (Y1_o,ad332211_o,nad00_o );

endmodule

四、Testbench

`timescale 1ps/1ps

module tb_comparator;

reg [3:0] A ;

reg [3:0] B ;

reg Y2_o;

reg Y1_o;

reg Y0_o;

initial begin

#5000 ;

A = 1;

B = 1;

#5000 ;

A = 1 ;

B = 0 ;

#5000 ;

A = 0 ;

B = 1 ;

#5000 ;

A = 0 ;

B = 0 ;

#5000;

repeat(10000)begin

d_case(A,B,{$random}%16,{$random}%16);

#5000 ;

end

end

/*-----------------------------------------------

-- --

-----------------------------------------------*/

task d_case;

output [3:0] a;

output [3:0] b;

input [3:0] a0;

input [3:0] b0;

begin

a = a0 ;

b = b0 ;

end

endtask

/*-----------------------------------------------

-- display --

-----------------------------------------------*/

always @ ( A or B )begin

if( A>B )begin

if({Y2_o,Y1_o,Y0_o} == {1,0,0})begin

end

else begin

$display($realtime,", A>B error:A=%d ;B=%d; Y2=%d ,Y1=%d,Y0=%d",A,B,Y2_o,Y1_o,Y0_o);

end

end

else if(A==B)begin

if({Y2_o,Y1_o,Y0_o} == {0,1,0})begin

end

else begin

$display($realtime,", A=B error:A=%d ;B=%d; Y2=%d ,Y1=%d,Y0=%d",A,B,Y2_o,Y1_o,Y0_o);

end

end

else if(A <B) begin

if({Y2_o,Y1_o,Y0_o} == {0,0,1})begin

end

else begin

$display($realtime,", A<B error:A=%d ;B=%d; Y2=%d ,Y1=%d,Y0=%d",A,B,Y2_o,Y1_o,Y0_o);

end

end

else begin

$display($realtime,", error:A=%d ;B=%d; Y2=%d ,Y1=%d,Y0=%d",A,B,Y2_o,Y1_o,Y0_o);

end

end

comparator u_comparator(

.A (A ),

.B (B ),

.Y2_o (Y2_o ),

.Y1_o (Y1_o ),

.Y0_o (Y0_o )

);

initial #60000000 $finish;

initial begin

$fsdbDumpfile("comparator.fsdb");

$fsdbDumpvars ;

$fsdbDumpMDA ;

end

endmodule

五、结果分析

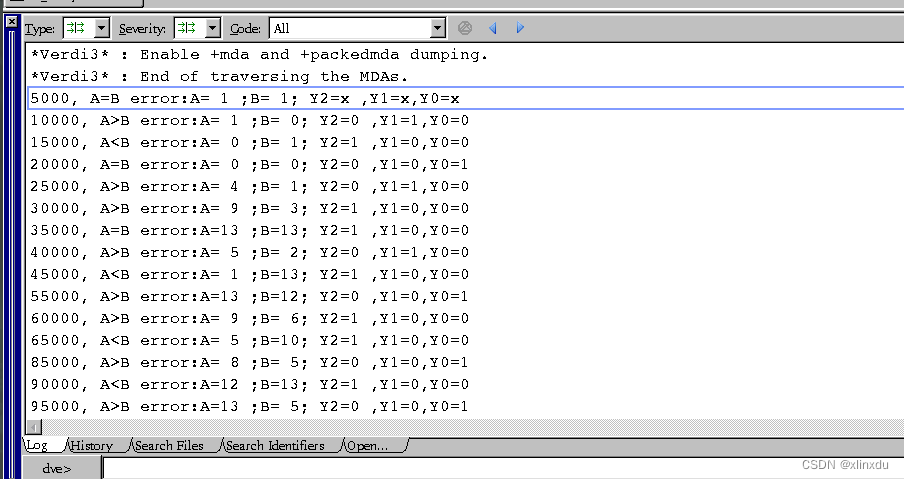

(1)TB结果

display打印错误信息,显示在时钟沿变化时出现错误。猜测是因为使用了输入作敏感列表,输入到输出存在延时。

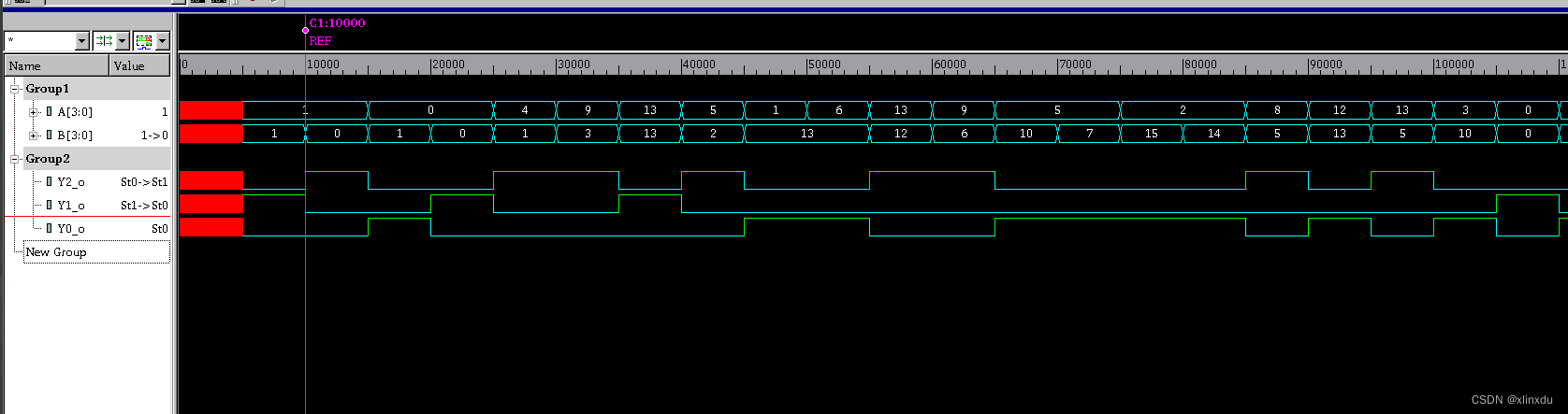

(2)波形图

时序符合预期,能正常比较两个4位数。

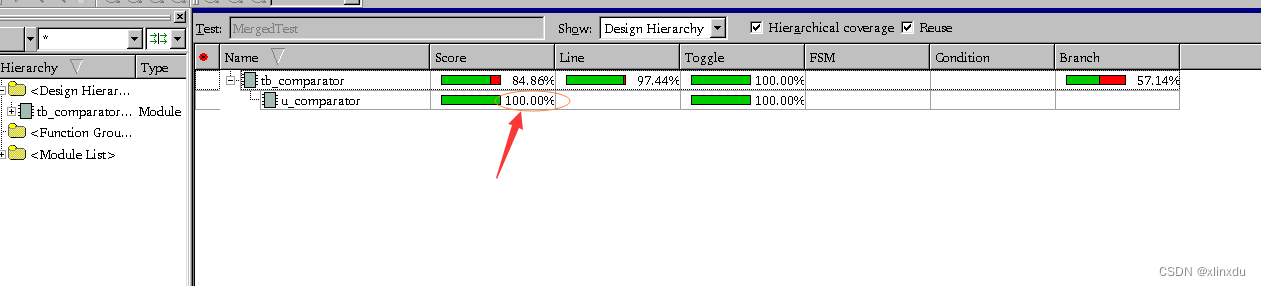

(3)覆盖率

代码覆盖率100%

✍✍☛ 题库入口

经过一段时间的沉淀,发现入行IC行业,自己的底子不扎实,文章质量参差不齐,也没能解答大家的疑问。因此决定通过补充/完善基础知识的同时,通过题库刷题不断提高自己的设计水平,<题库记录>栏目不定期更新,欢迎前来讨论。

作者:xlinxdu

版权:本文版权归作者所有

转载:未经作者允许,禁止转载,转载必须保留此段声明,必须在文章中给出原文连接。

最后

以上就是高兴花生最近收集整理的关于VL11 4位数值比较器电路一、题目(1)题目描述(2)端口描述二、分析三、RTL四、Testbench五、结果分析(1)TB结果(2)波形图(3)覆盖率的全部内容,更多相关VL11内容请搜索靠谱客的其他文章。

发表评论 取消回复