在学习sysgen的时候发现还有一个好用的工具就是hdl coder。他能够将matlab或是sumulink或是state flow'转换成verilog代码或是vhdl;

下面是是使用步骤,做个总结。

首先建立好模型,我用的是filter一个滤波器,选择用器件实现,应为这样好实现优化。

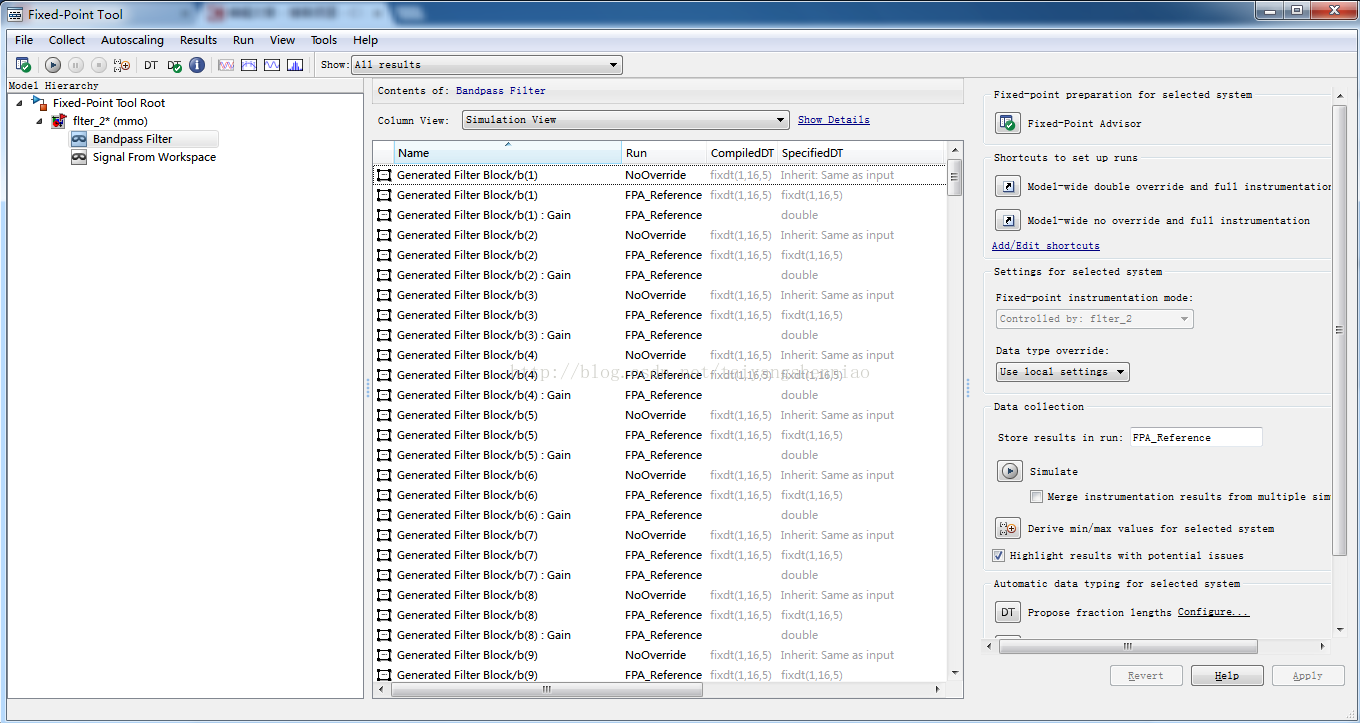

之后领用fixed point tool 来实现浮点到顶点的转换。如下图

完成后为了保存数据用于定点和浮点的比较,首先点击Model - wild double override and full instrumantation;这个使用原来的浮点模型实现设计,然后点击simulation。

之后,点击propose fraction lengths,系统推荐长度。并选择FPGA_refrence。

设置好后选择apply accepted franction length;接受系统推荐。

然后就可以点击Model - wild no override and full instrumantation;应用定点模型;病simulate。

定点设计算是完成啦,后面会有一个自动比较波形的,可以看到浮点和定点的比较。

定点装换完成后,就可以去hdl coder去做代码装换啦。

注意:代码装换只选取自己需要装换的模块,其他的不必要的如spectum display什么的就不要了。

最后

以上就是懦弱冬天最近收集整理的关于sysgen学习之hdl coder使用的全部内容,更多相关sysgen学习之hdl内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复