数字电路基础知识——CMOS门电路 (非门、或非门、与非门、或门、与门、与或非门、异或门、OD门、传输门、三态门)

先了解二极管门电路逻辑,再次介绍CMOS门电路,也是IC中用的最广泛的门电路。

主要了解与非门、或非门以及相同面积的cmos与非门和或非门哪个更快。OD门、传输门、三态门。

一、二极管门电路

CMOS门电路介绍之前,先介绍二极管门电路:

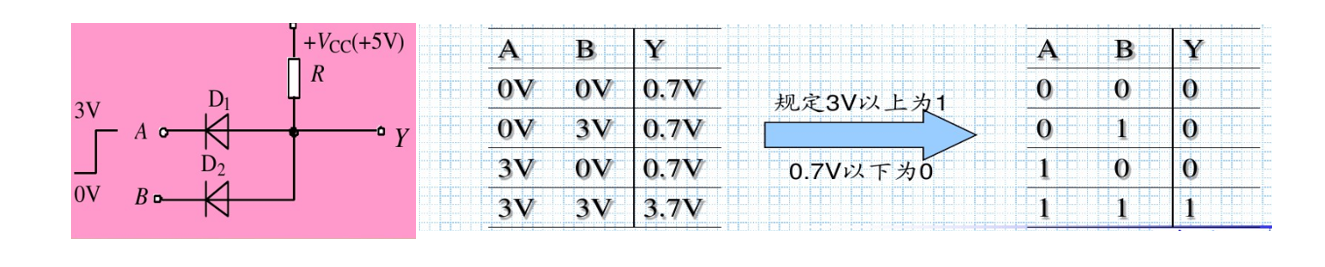

1. 与门

只要有一个为低电平,Y端就被拉低到0.7V

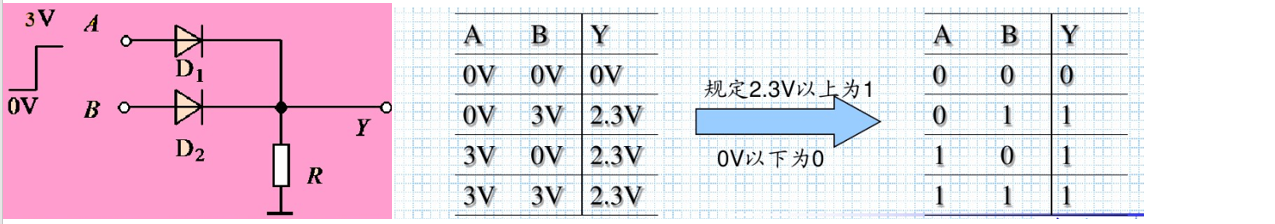

2. 或门

只要有一个为高电平,Y端就被拉高到2.3V

3. 二极管门电路的缺点

输出的高低电平数值和输入的高低电平不相等,相差一个导通电压,如果输出作为下一级门输入信号,将发生高、低电平偏移

输出端对地接上负载电阻,组在电阻的改变会影响输出高电平。因此,这种电路只用作IC内部的逻辑单元,并不能作为输出端直接驱动负载。

二、CMOS 门电路

1. 反相器(非门)

反向器的介绍可以参考

数字电路基础知识——反相器的相关知识(噪声容限、VTC、转换时间、速度的影响因素、传播延时等)

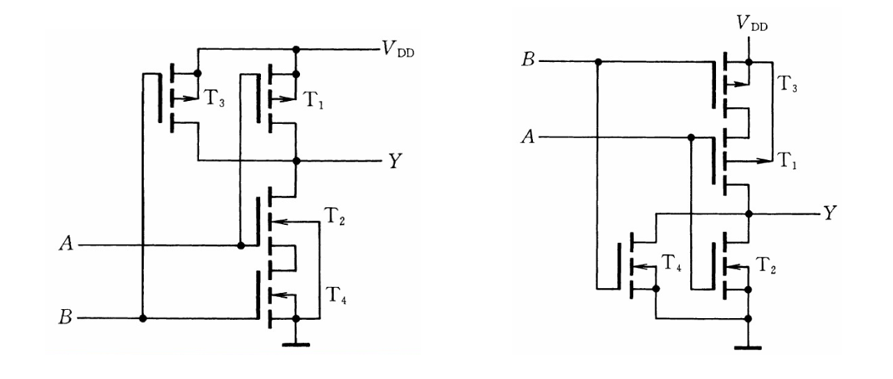

2. 常用的逻辑门:或非门、与非门

除了反相器,比较常用的有 或非门、与非门、或门、与门、与或非门、异或门等。

逻辑表达式分别为:

Y=(AB)’

T=(A+B)'

下面主要了解下与非门其缺点、和改进的电路.

主要缺点:

1)输出电阻R0受输入状态影响,即输出电阻不一样,能够相差四倍。如:

A=1, B=1,则R0 = Ron2 + Ron4 = 2Ron

A=0, B=0,则R0 = Ron2 // Ron4 = 1/2Ron

A=0, B=1,则R0 = Ron1 = Ron

A=0, B=0,则R0 = Ron3 = Ron

2)输出的高低电平受输入端数目的影响

输入端越多,,串联的驱动管数目也越多,输出的VOL越高,VOH也更高。

当输入端全部为低电平时,输入端越多负载并联的数目越多,输出的高电平VOH也越高。

3)使T2、T4的Vgs达到开启电压时,对应的Vi也会不同

相同面积的cmos与非门和或非门哪个更快——与非门会更优

学过半导体器件都知道,电子迁移率是空穴的2.5倍(在硅基CMOS工艺中),运算就是用这些大大小小的MOS管驱动后一级的负载电容,翻转速度和负载大小一级前级驱动能力相关。为了上升延迟和下降延迟相同,PMOS需要做成NMOS两倍多大小。

载流子的迁移率,对PMOS而言,载流子是空穴;对NMOS而言,载流子是电子。

PMOS采用空穴导电,NMOS采用电子导电,由于PMOS的载流子的迁移率比NMOS的迁移率小,所以,同样尺寸条件下,PMOS的充电时间要大于NMOS的充电时间长。

在互补CMOS电路中,与非门是PMOS管并联,NMOS管串联,而或非门正好相反,所以,同样尺寸条件下,与非门的速度快,所以,在互补CMOS电路中,优先选择与非门。

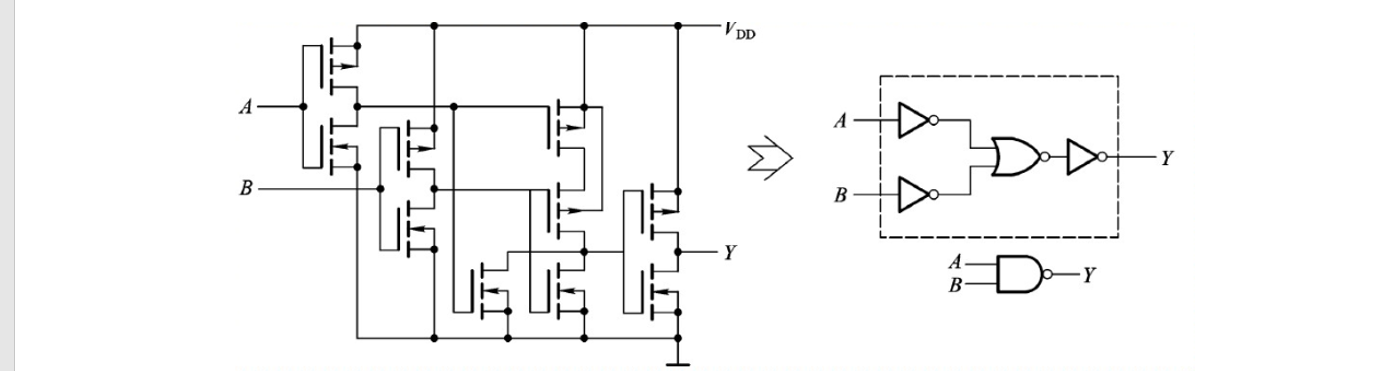

针对上面问题进行改进

采用或非门加反相器(缓冲器 就是与非门,如上图所示。

带缓冲的门电路,输出电阻、输出的高低电平以及电压传输特性将不受输入端状态的影响

对于或非门,则是与非门加缓冲器。

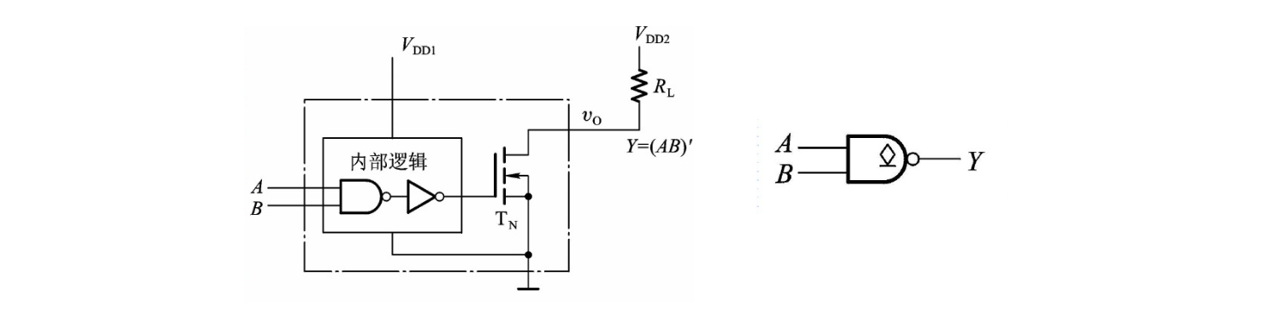

3. OD门(漏极开路的门电路)

OD门:为了满足输出电平的转换,吸收大负载电流以及线与逻辑,将MOS改为漏极开路

OD输出的与非门结构图如下:

OD门工作必须接上拉电阻RL到电源上。

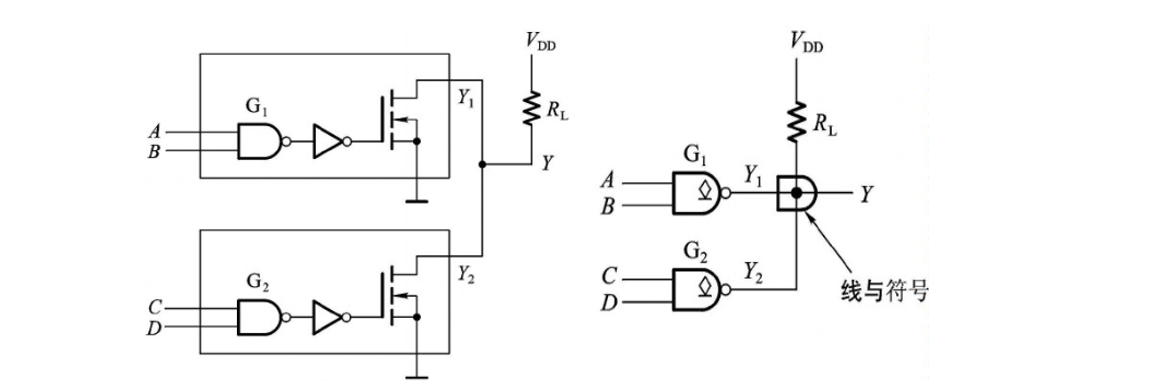

OD门的应用:可以将多个OD门输出端直接相连,实现线与逻辑,即将输出并联使用,可以实现线与或用作电平转换和驱动。如下图所示:

Y1、Y2中任何一个为低电平,输出都为低电平,同时为高时,输出才为高电平。

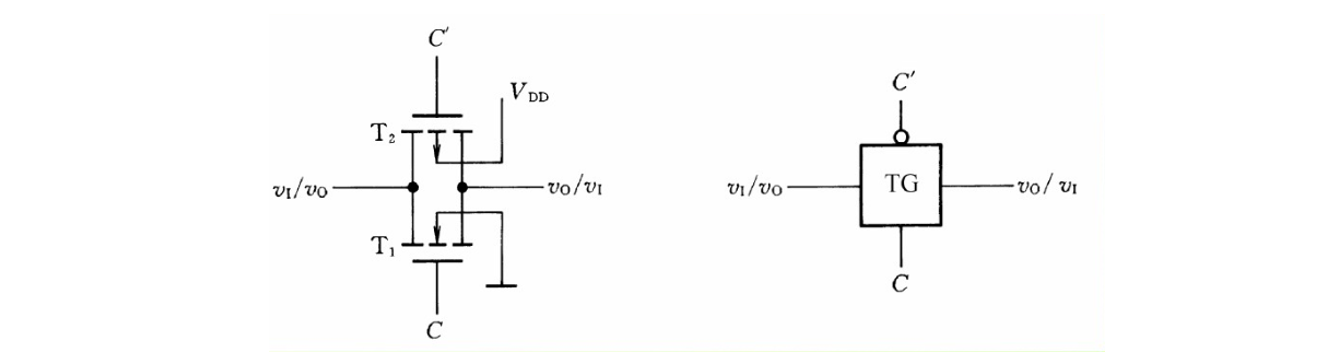

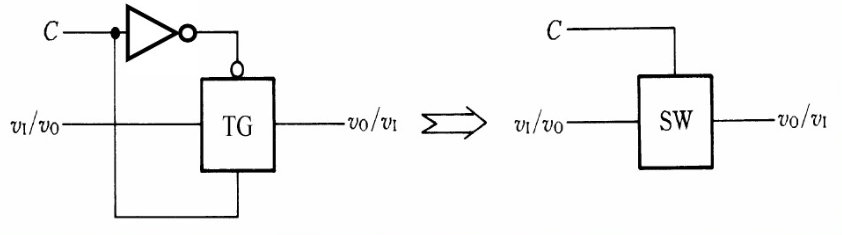

4. 传输门

CMOS传输门:利用P沟道MOS管和N沟道MOS管互补的特性连接如下图

T1是N沟道增强型MOS管,T2是P沟道增强型MOS管。T1和T2的源极和漏极分别相连作为传输门的输入端和输出端。C和C’是互补的控制信号。

由于CMOS传输门的结构是对称的,所以,输出端和输入端可以互换,是一个双向器件。

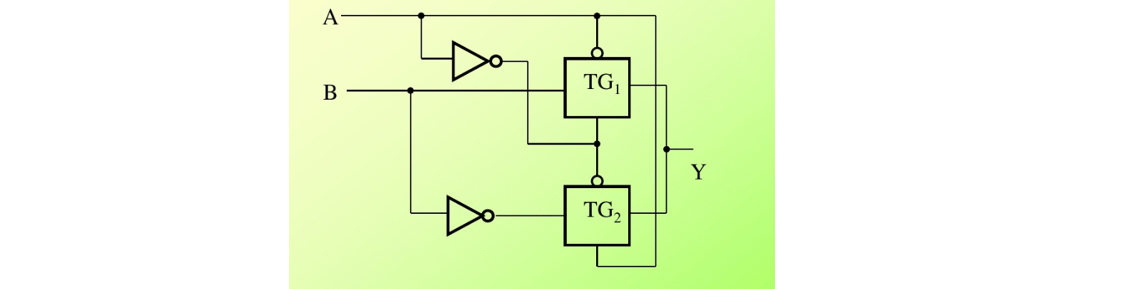

CMOS传输门的应用:

1)传输门和反相器构成异或门电路:

A=1,B=0,TG1截止,TG2导通,Y=B’=1

A=0,B=1,TG1导通,TG2截止,Y=B=1

A=0,B=0,TG1导通,TG2截止,Y=B=0

A=1,B=1,TG1截止,TG2导通,Y=B‘=0

2)模拟开关:

由传输门和一个反相器组成,双向器件。

传输连续变化的模拟电压信号。

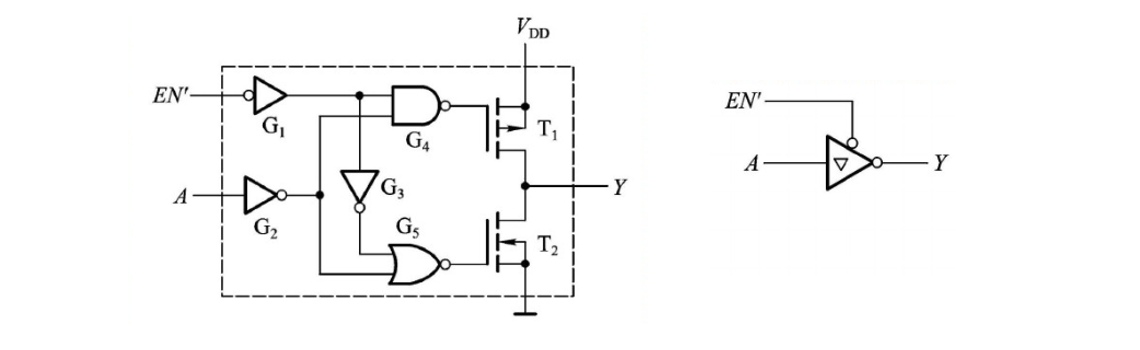

5. 三态门

1)高阻态:

三态门除了高低电平,还有第三个状态——高阻态。

高阻态:电路的一种输出状态,既不是高电平也不是低电平,如果高阻态再输入下一级电路的话,对下级电路无任何影响,可以理解为断路,不被任何东西所驱动,也不驱动任何东西。

三态门常用在IC的输出端,也称为输出缓冲器

2)下图是CMOS三态输出反相器的结构:

当EN’=0时,Y=A’:

A=1,G4、G5的输出为高电平,T1截止、T2导通,Y=0;

A=0,G4、G5的输出为低电平,T1导通、T2截止,Y=1;

当EN’=1时,不管A为高低状态,G4输出高电平,G5输出低电平,T1和T2同时截止,输出呈现高阻态。

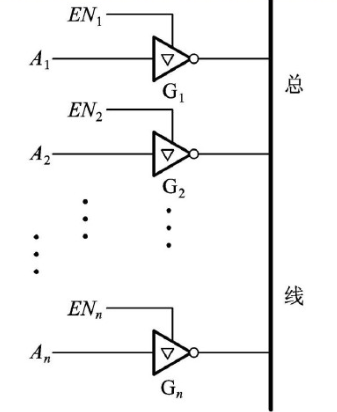

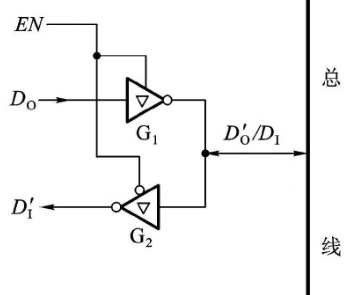

3)三态门的应用:

减少各单元之间的连线数目:

数据的双向传输:

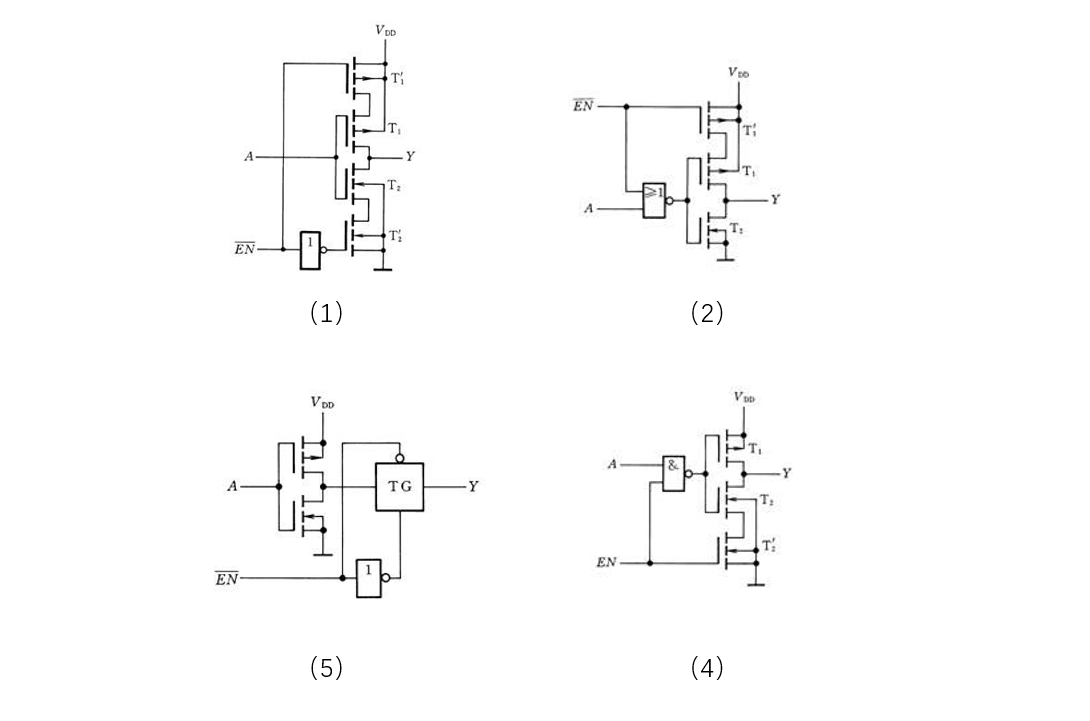

4)还有几种常见的三门结构:

图一:

三态非门,当~ EN为1时,最上面的PMOS和最下面的NMOS管截止,无论A取什么状态,输出为高阻态,反之输出为 Y= ~ A

图二:

利用一个与非门,得到三态缓冲门,当~EN为高电平时,最上面的PMOS管截止,输出为高阻态,反之,输出为 Y=A

图三:

三态非门,在反相器后面加一个传输门,当~EN为低电平,传输门导通,输出 Y = ~A,反之传输门截止,输出高阻态。如果想要EN高电平有效,交换传输门上下端子的反相器即可。

图四:

利用一个与非门,得到三态缓冲门,当~EN为高电平时,最上面的PMOS管截止,输出为高阻态,反之,输出为 Y=A

最后

以上就是深情学姐最近收集整理的关于数字电路基础知识——CMOS门电路 (与非门、或非、非门、OD门、传输门、三态门)的全部内容,更多相关数字电路基础知识——CMOS门电路内容请搜索靠谱客的其他文章。

发表评论 取消回复