文章目录

- 锁存器和触发器

- 一、基本双稳态电路

- 1.1 原理

- 1.2 定义

- 1.3 电路图

- 二、基本 SR 锁存器

- 2.1 引入

- 2.2 功能分析

- 2.3 波形图

- 2.4 逻辑符号

- 2.5 动态特性

- 三、门控 SR 锁存器

- 3.1 引入

- 3.2 原理

- 3.3 逻辑符号

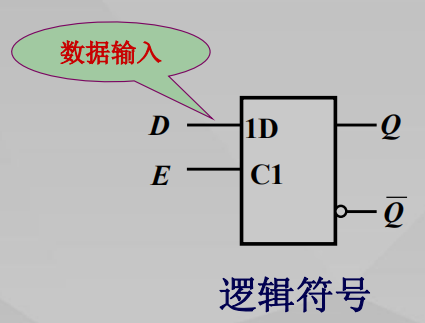

- 四、逻辑门控 D 锁存器

- 4.1 引入

- 4.2 功能表

- 4.3 逻辑符号

- 五、传输门控 D 锁存器

- 5.1 传输门

- 5.2 组成

- 5.3 功能分析

- 5.5 逻辑符号

锁存器和触发器

一、基本双稳态电路

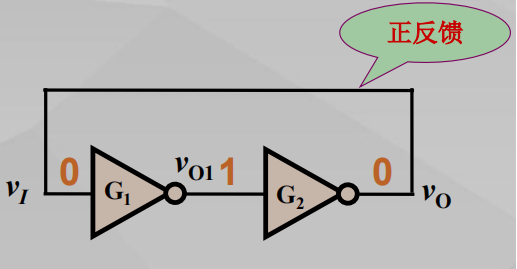

1.1 原理

- 假设刚上电时,

v

O

=

0

v_O= 0

vO=0,则

v

i

=

0

→

v

O

1

=

1

→

v

O

=

0

v_i = 0to v_{O1} = 1to v_O = 0

vi=0→vO1=1→vO=0;

- 假设刚上电时,

v

O

=

1

v_O= 1

vO=1,则

v

i

=

1

→

v

O

1

=

0

→

v

O

=

1

v_i = 1to v_{O1} = 0to v_O = 1

vi=1→vO1=0→vO=1;

- 结论:该电路一旦进入某一种逻辑状态,就能长期保持该状态不变。

1.2 定义

- 将具有0、1两种逻辑状态,且一旦进入某一种逻辑状态,就能长期保持该状态不变的电路,称为双稳态存储电路,简称双稳态电路。

1.3 电路图

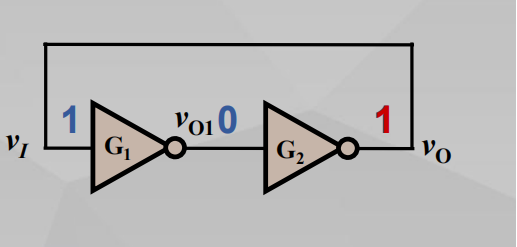

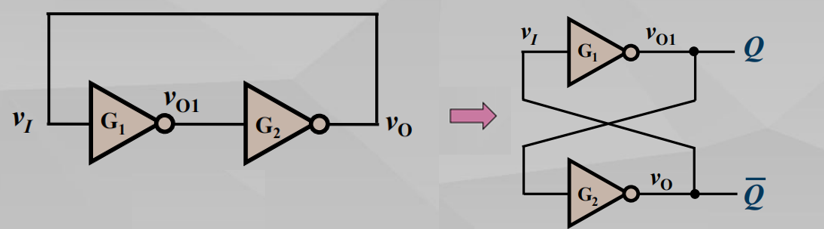

- 电路图

改变一下电路的画法,并用 Q Q Q、 Q ‾ overline{Q} Q 作为两个非门的输出。

- 定义

(1)定义 Q = 0 Q = 0 Q=0、 Q ‾ = 1 overline{Q} = 1 Q=1时为电路的 0状态;

(2)定义 Q = 1 Q = 1 Q=1、 Q ‾ = 0 overline{Q} = 0 Q=0时为电路的 1状态。 - 说明

(1) 电路在正常工作时,两个输出端的状态通常是相反的(也称为互补的);

(2)输出端 Q 称为常态输出,Q 称为反态输出;

(3)习惯上, 用输出端 Q 的状态来表示双稳态电路的状态。

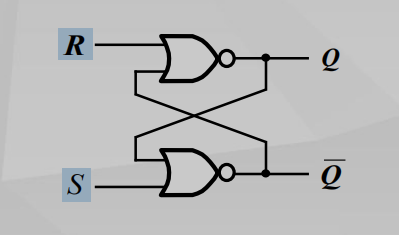

二、基本 SR 锁存器

2.1 引入

- 在基本双稳态电路图中,用或非门来替换掉非门,构成基本SR锁存器,如下图所示:【注意】:一下分析均为用或非门构成的基本SR锁存器,用与非门构成的基本SR 锁存器功能(基本

S

‾

R

‾

overline{S} overline{R}

S R锁存器)与之相反,这里不给予介绍。

2.2 功能分析

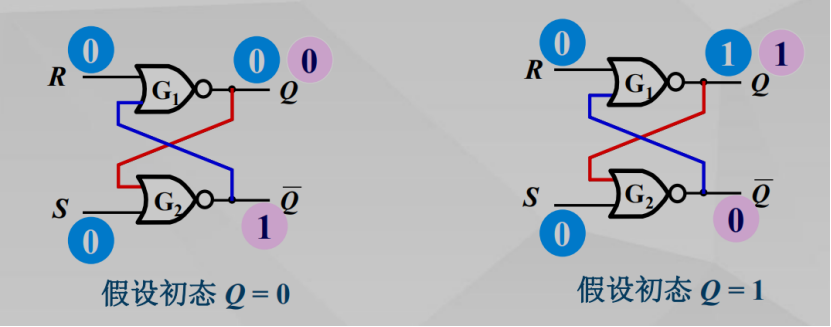

- 当S=0,R=0时,状态保持不变。即SR 锁存器对输入的低电平信号不起作用。

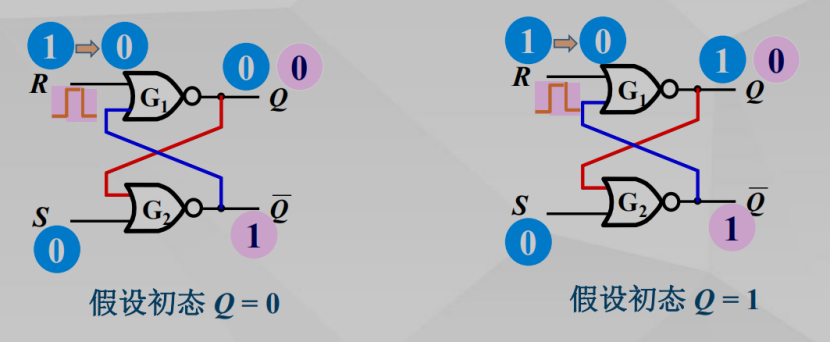

- 当S=0,R=1时,复位(Reset)。即无论初态为0或1,锁存器的次态均为0态。输入信号消失后,新的状态将被记忆下来。

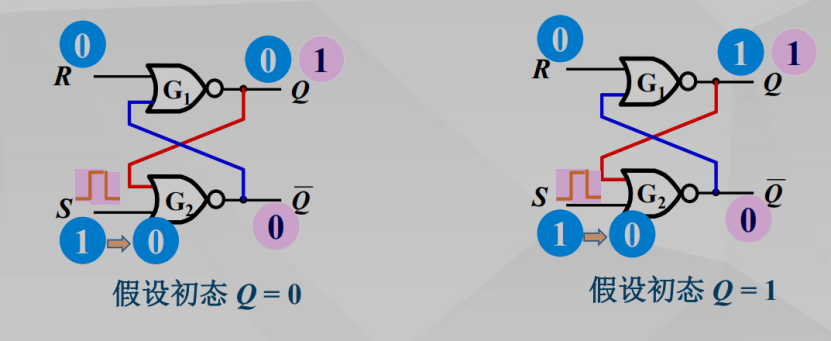

- 当S=1,R=0时, 置位(Set)。即无论初态为0或1,锁存器的次态均为1态。输入信号消失后新的状态将被记忆下来。

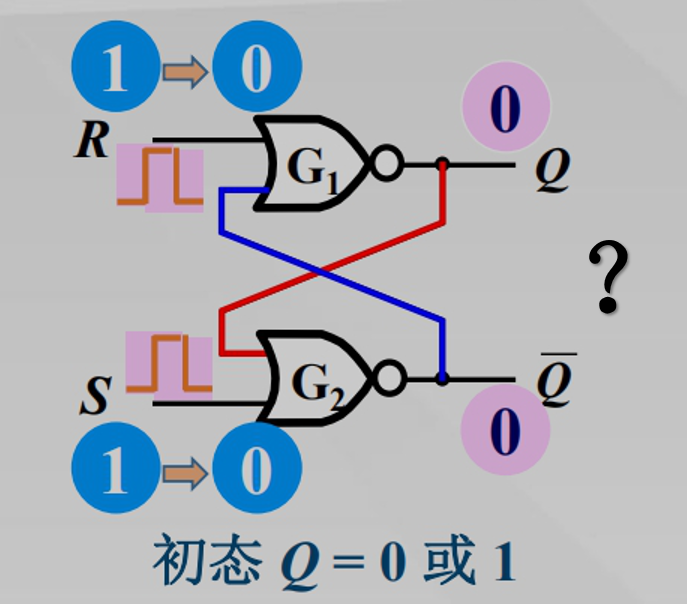

- 当S=1,R=1时,状态不确定。即无论初态为0或1,锁存器的两个输出端均为0。

(1)锁存器的输出既不是0态,也不是1态。 即状态不确定。

(2)当 S、R 同时回到0时,无法确定锁存器的最终稳定状态为 1 还是 0 。

(3)因此,不允许输入出现 S=R=1 的情况。换言之,输入信号要满足条件: S ⋅ R = 0 Scdot R = 0 S⋅R=0(约束条件) - 功能表

| S S S | R R R | Q Q Q | Q ‾ overline{Q} Q | 功 能 |

|---|---|---|---|---|

| 0 | 0 | 不变 | 不变 | 保持 (No change) |

| 0 | 1 | 0 | 1 | 置 0 (RESET) |

| 1 | 0 | 1 | 0 | 置 1 (SET) |

| 1 | 1 | 0 | 0 | 非定义状态 |

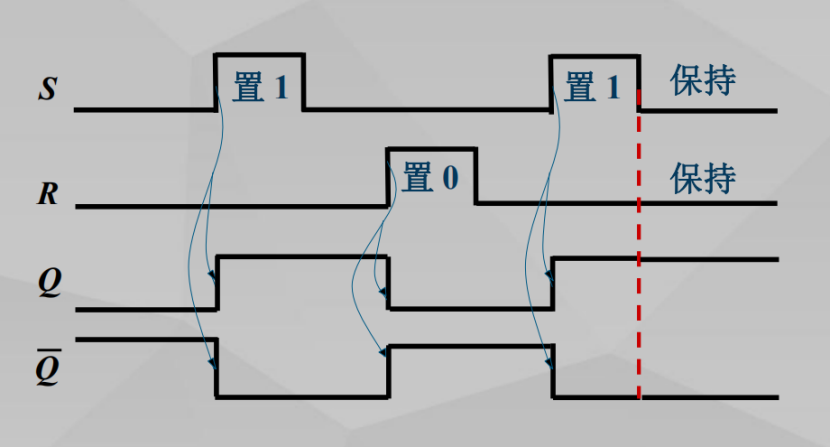

2.3 波形图

- 假设 SR 锁存器的初态

Q

=

0

Q = 0

Q=0,输入波形如图所示,试

画出 Q Q Q 和 Q ‾ overline{Q} Q 波形。

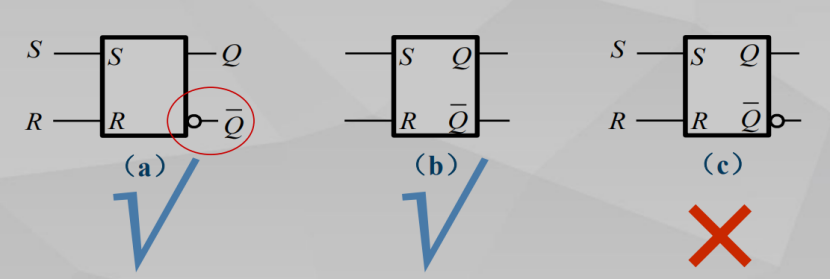

2.4 逻辑符号

- 符号(a)是当前最流行的一种符号。

- 符号(b)是历史上曾经使用过的一种符号。

- 符号(c)是错误的。

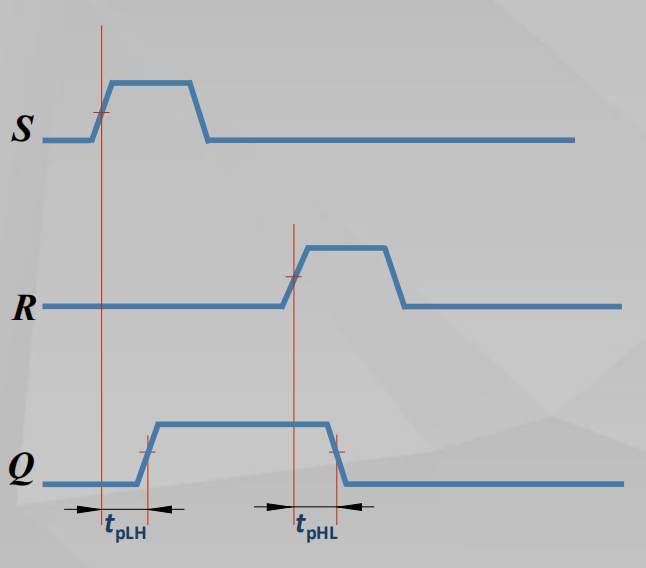

2.5 动态特性

- 传输延迟时间

t

p

L

H

t_{pLH}

tpLH和

t

p

H

L

t_{pHL}

tpHL

(1) t p L H t_{pLH} tpLH为输出由低到高时,相对于输入的延迟时间。

(2) t p H L t_{pHL} tpHL为输出由高到低时,相对于输入的延迟时间。

(3) t p L H t_{pLH} tpLH和 t p H L t_{pHL} tpHL一般不相等。

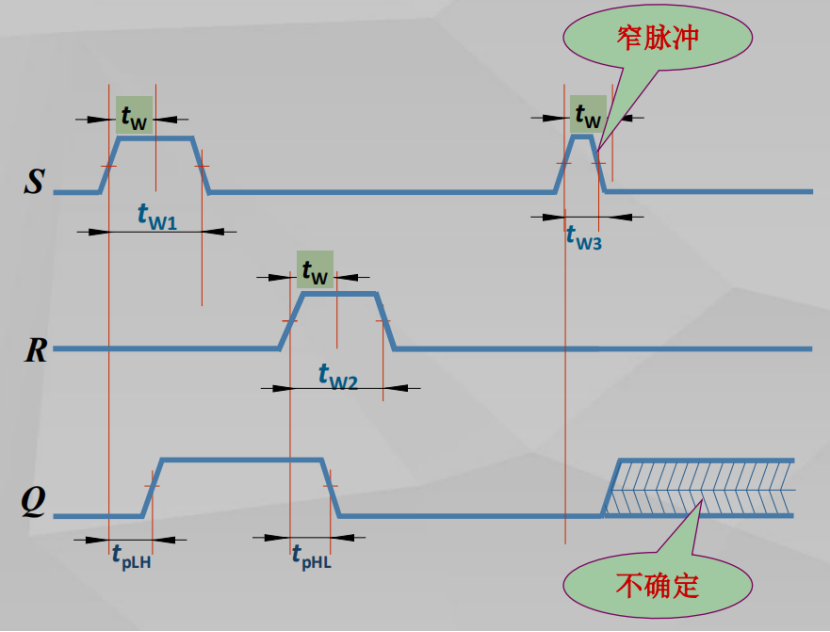

- 脉冲宽度

t

W

t_W

tW

(1) t W t_W tW是保证锁存器正常翻转时,输入高电平脉冲宽度的最小值。

(2)如果输入脉冲宽度 < t W <t_W <tW , Q Q Q 端电压值未越过逻辑阈值电平时,输入的高电平被撤出,就会导致输出状态不稳定。

三、门控 SR 锁存器

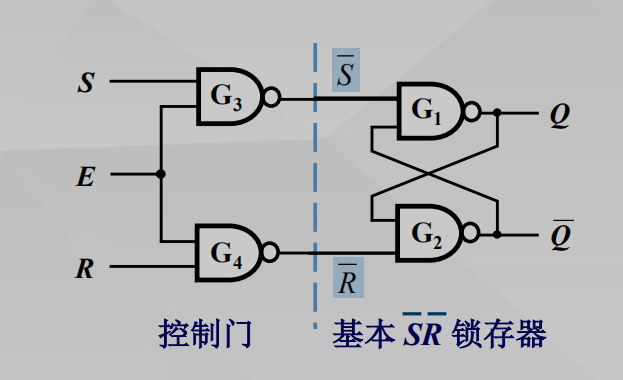

3.1 引入

- 在基本

S

‾

R

‾

overline{S} overline{R}

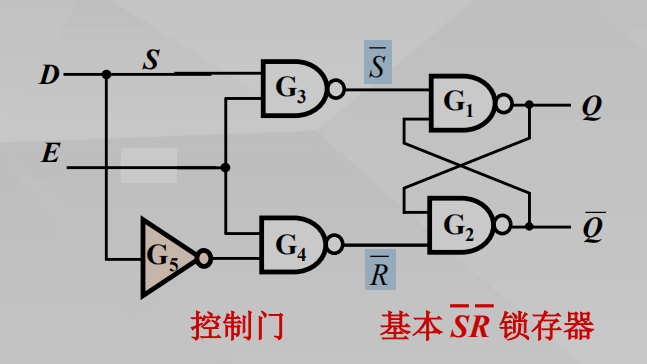

S R锁存器输入端增加了一对与非门G3、G4,用使能信号 E控制锁存器在某一指定时刻,根据 S、R 输入信号确定输出状态,这种锁存器称为门控 SR 锁存器。

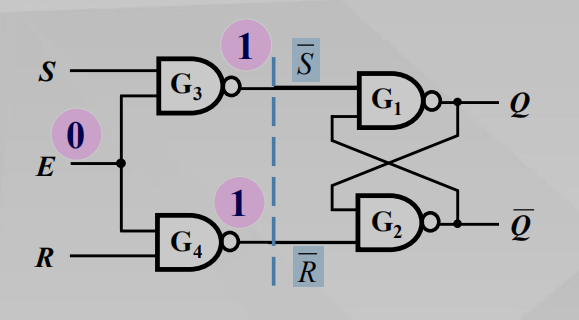

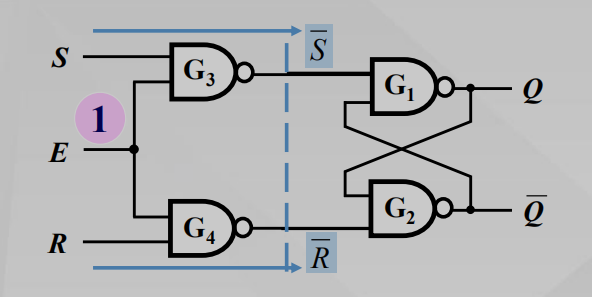

3.2 原理

- 当 E = 0 时,

S

‾

=

R

‾

=

1

overline{S}=overline{R}=1

S=R=1,锁存器状态不变。

功能和基本 S ‾ R ‾ overline{S} overline{R} S R锁存器相同,功能表如下:

| S ‾ overline{S} S | R ‾ overline{R} R | Q Q Q | Q ‾ overline{Q} Q | 功 能 |

|---|---|---|---|---|

| 1 | 1 | 不变 | 不变 | 保持 (No change) |

| 1 | 0 | 0 | 1 | 置 0 (RESET) |

| 0 | 1 | 1 | 0 | 置 1 (SET) |

| 0 | 0 | 1 | 1 | 非定义状态 |

- 当 E = 1 时,则S、R端的信号被传送到基本锁存器的输入端,使输出状态发生变化。

门控 SR 锁存器的功能表(E=1时),功能表如下:

| S S S | R R R | Q Q Q | Q ‾ overline{Q} Q | 功 能 |

|---|---|---|---|---|

| 0 | 0 | 不变 | 不变 | 保持 (No change) |

| 0 | 1 | 0 | 1 | 置 0 (RESET) |

| 1 | 0 | 1 | 0 | 置 1 (SET) |

| 1 | 1 | 1 | 1 | 非定义状态 |

- 总功能表

门控 SR 锁存器的功能表如下:

| E | S S S | R R R | Q Q Q | Q ‾ overline{Q} Q | 功 能 |

|---|---|---|---|---|---|

| 0 | X | X | 不变 | 不变 | 保持 (No change) |

| 1 | 0 | 0 | 不变 | 不变 | 保持 (No change) |

| 1 | 0 | 1 | 0 | 1 | 置 0 (RESET) |

| 1 | 1 | 0 | 1 | 0 | 置 1 (SET) |

| 1 | 1 | 1 | 1 | 1 | 非定义状态 |

门控 SR 锁存器输入信号要满足条件: S ⋅ R = 0 Scdot R = 0 S⋅R=0 (约束条件)

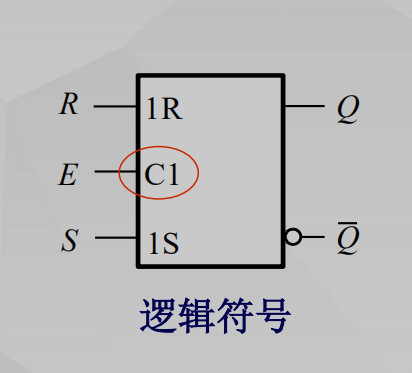

3.3 逻辑符号

- 逻辑符号方框内用 C1 和 1R、1S 表达内部逻辑之间的关联关系。

- C 表示这种关联属于控制类型,其后缀用标识序号“1”表示该输入的逻辑状态对所有以“1”作为前缀的输入起控制作用。

四、逻辑门控 D 锁存器

4.1 引入

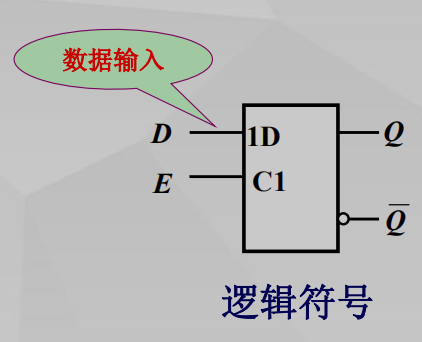

- 在门控 SR 锁存器的两个输入端之间增加一个非门,构成门控 D 锁存器。

由于 S = D S = D S=D, R = D ‾ R = overline{D} R=D, 所以消除了输出端可能出现的非定义状态。

4.2 功能表

| E E E | D D D | Q Q Q | Q ‾ overline{Q} Q | 功 能 |

|---|---|---|---|---|

| 0 | X | 不变 | 不变 | 保持 (No change) |

| 1 | 0 | 0 | 1 | 置 0 (RESET) |

| 1 | 1 | 1 | 0 | 置 1 (SET) |

4.3 逻辑符号

五、传输门控 D 锁存器

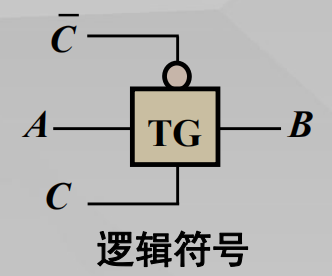

5.1 传输门

- 逻辑符号

- 定义

传输门就是一个能够传输模拟信号的模拟开关。开关导通时,其导通电阻较低。 - 功能分析

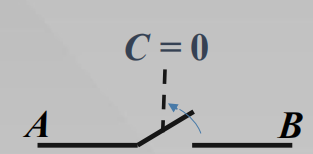

(1)传输门通常受互补逻辑信号 C C C 和 C ‾ overline{C} C控制。

(2)当 C = 0 C = 0 C=0, C ‾ = 1 overline{C} = 1 C=1 时, 开关断开,不能传送信号。

(3)当 C = 1 C = 1 C=1, C ‾ = 0 overline{C} = 0 C=0 , 开关连通,信号可以从A传送到B。也可以从B传送到A。

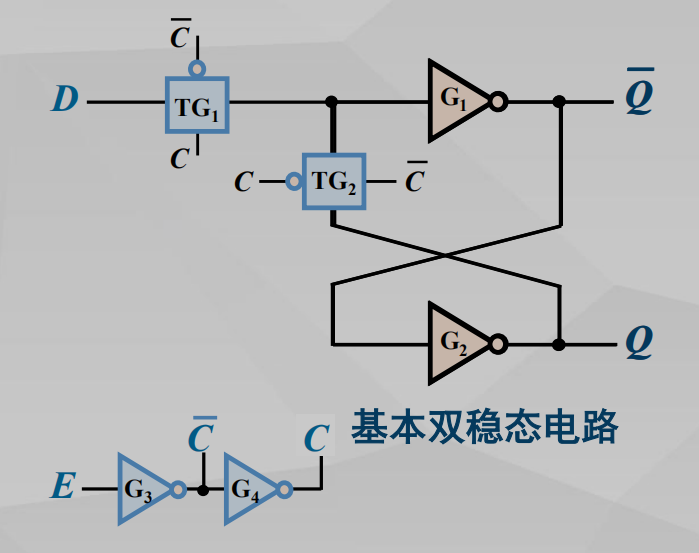

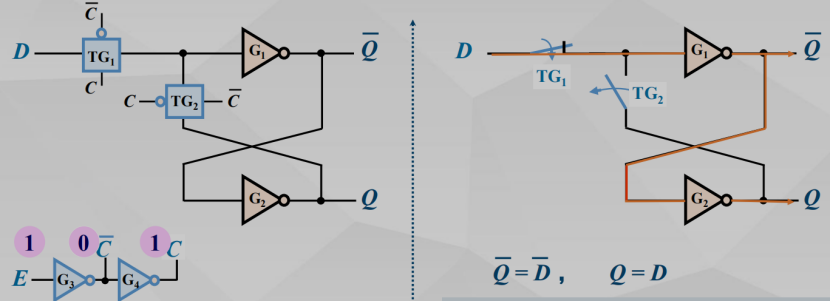

5.2 组成

- 传输门控 D 锁存器由基本双稳态电路和传输门组成。

5.3 功能分析

- 当

E

=

1

E=1

E=1 时,

C

‾

=

0

overline{C} = 0

C=0,

C

=

1

C = 1

C=1,

T

G

1

TG_1

TG1导通

T

G

2

TG_2

TG2断开。

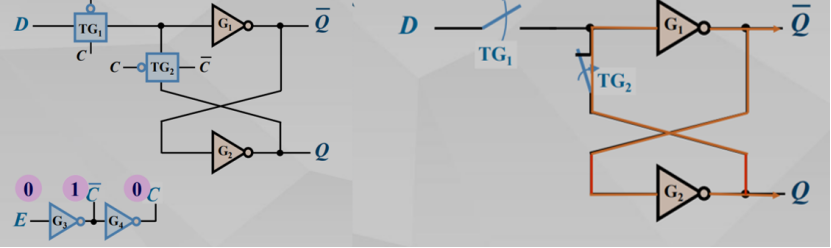

可见,在 E=1期间,输出端Q 的状态始终与输入的状态保持相同。 - 当

E

=

0

E=0

E=0 时,

C

‾

=

1

overline{C} = 1

C=1,

C

=

0

C = 0

C=0,

T

G

1

TG_1

TG1断开

T

G

2

TG_2

TG2导通。

电路的原理与基本双稳态电路相同。电路将存储 E由1变0之前的瞬间 D的值,实现了 1位数据的存储。

5.5 逻辑符号

最后

以上就是淡定御姐最近收集整理的关于数值逻辑之锁存器锁存器和触发器的全部内容,更多相关数值逻辑之锁存器锁存器和触发器内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复