时序逻辑的一般设计规则是:

在绝大多数设计中避免产生latch(锁存器)。它会让您设计的时序完蛋,并且它的隐蔽性很强,非老手不能查出。latch最大的危害在于不能过滤毛刺。这对于下一级电路是极其危险的。所以,只要能用D触发器的地方,就不用latch。

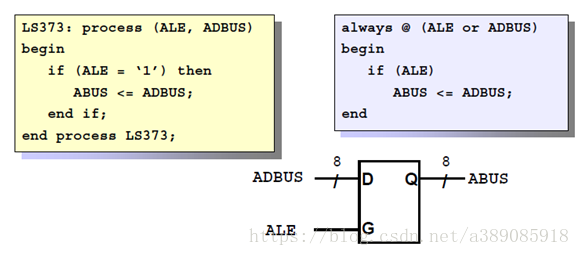

钟控D触发器其实就是D锁存器,边沿D触发器才是真正的D触发器,钟控D触发器在使能情况下输出随输入变化,边沿触发器只有在边沿跳变的情况下输出才变化。

两个锁存器可以构成一个触发器,归根到底还是dff是边沿触发的,而latch是电平触发的。锁存器的输出对输入透明的,输入是什么,输出就是什么,这就是锁存器不稳定的原因,而触发器是由两个锁存器构成的一个主从触发器,输出对输入是不透明的,必须在时钟的上升/下降沿才会将输入体现到输出,所以能够消除输入的毛刺信号。

always块可以表示时序逻辑或者组合逻辑,也可以用always块既表示电平敏感的透明锁存器又

同时表示组合逻辑。但是不推荐使用这种描述方法,因为这容易产生错误和多余的电平敏感的透明锁存器。

如果要为电平敏感的锁存器建模,使用连续赋值语句是最简单的方法。

例:

input a,b,c;

reg e,d;

always @(a or b or c) begin

e =d & a & b;

end

/* 因为d没有在敏感电平列表中,所以d变化时,

e不能立刻变化,要等到a或b或c变化时才体现出来,

这就是说实际上相当于存在一个电平敏感的透

明锁存器在起作用, 把d信号的变化锁存其中 */

应更改为

用assign赋值: assign e = d&a&b;

always @(*) begin

e =d & a & b;

end

最后

以上就是老实大地最近收集整理的关于D触发器和锁存器的全部内容,更多相关D触发器和锁存器内容请搜索靠谱客的其他文章。

发表评论 取消回复