VHDL课程设计:四位电子密码锁

荒废了一个假期,快要开学了,写篇博客"庆祝庆祝",同时,今天心情也不是很好,算了,废话不多说,下面进入正题吧。

1.题目要求:

本次博客的题目是利用VHDL设计一个四位密码锁,题目要求如下:

四位密码,使用数据开关K1-K10分别代表数字0-9

输入密码用数码管显示,每输入一位,密码左移一位

删除的是最后一位数字,删除一位,右移一位,空出位补充”0”

用一位输出电平表示锁开闭状态

设置万能密码,在忘记密码的情况下可以打开锁

2.源码及注释(文件附件下载):

编译的软件为Quartus II13.0,工程如何建立大家应该都知道了,这块不多讲,就直接添加各个模块相关源码及注释 PS:实在不想排版了,附件有源码文件加载,需要用的直接下载就行。

顶层文件:fanzhen.vhd

--顶层文件。 LIBRARY ieee; USE ieee.std_logic_1164.all; LIBRARY work; --实体描述 ENTITY fangzhen IS port( rest : IN STD_LOGIC; shizhongxinhao : IN STD_LOGIC; gaimij : IN STD_LOGIC; querenj : IN STD_LOGIC; shanchuj : IN STD_LOGIC; jianpanshurru : IN STD_LOGIC_VECTOR(3 downto 0); zhenque_gaodianping : OUT STD_LOGIC; baojing : OUT STD_LOGIC; zhishideng : OUT STD_LOGIC; qimaguanxianshi : OUT STD_LOGIC_VECTOR(15 downto 0)); END fangzhen; --结构体描述 ARCHITECTURE bdf_type OF fangzhen IS --验证改密元件定义 component yzgm PORT( clk : IN STD_LOGIC; gaimij2 : IN STD_LOGIC; queren : IN STD_LOGIC; input2 : IN STD_LOGIC_VECTOR(15 downto 0); output2 : OUT STD_LOGIC); end component; --移位寄存器元件定义 component ywjcq PORT( rest : IN STD_LOGIC; shanchu : IN STD_LOGIC; clk : IN STD_LOGIC; input : IN STD_LOGIC_VECTOR(3 downto 0); output : OUT STD_LOGIC_VECTOR(15 downto 0)); end component; --数码管显示元件定义 component yimasc PORT( clk : IN STD_LOGIC; datain : IN STD_LOGIC_VECTOR(15 downto 0); dataout : OUT STD_LOGIC_VECTOR(15 downto 0)); end component; --电锁控制元件定义 component dskz PORT( clk : IN STD_LOGIC; input : IN STD_LOGIC; reset : IN STD_LOGIC; queren : IN STD_LOGIC; light : OUT STD_LOGIC; alarm : OUT STD_LOGIC); end component; --d4触发器元件定义 component d4 port( clk:in std_logic; a: in std_logic_vector(3 downto 0); rest1,querenj1,gaimij1,shanchuj1:in std_logic; q:out std_logic_vector(3 downto 0); rest2,querenj2,gaimij2,shanchuj2:out std_logic; oclk:out std_logic); end component; --输入密码存放 signal SYNTHESIZED_WIRE_0 : STD_LOGIC_VECTOR(15 downto 0); --开锁信号 signal SYNTHESIZED_WIRE_1 : STD_LOGIC:='0'; --按键 signal key:std_LOGIC_VECTOR(3 downto 0); --依次是重置、确认、改密、删除、以及键盘输入信号 signal rest3,querenj3,gaimij3,shanchuj3,ok: STD_LOGIC; BEGIN zhenque_gaodianping <= SYNTHESIZED_WIRE_1; --验证改密元件例化 b2v_inst : yzgm PORT MAP(clk => shizhongxinhao, gaimij2 => gaimij3, queren => querenj3, input2 => SYNTHESIZED_WIRE_0, output2 => SYNTHESIZED_WIRE_1); --移位寄存器元件例化 b2v_inst1 : ywjcq PORT MAP(rest => rest3, shanchu => shanchuj3, clk => ok, input => key, output => SYNTHESIZED_WIRE_0); --数码管显示元件例化 b2v_inst2 : yimasc PORT MAP( clk => shizhongxinhao, datain => SYNTHESIZED_WIRE_0, dataout => qimaguanxianshi); --电锁控制元件例化 b2v_inst3 : dskz PORT MAP(clk => shizhongxinhao, input => SYNTHESIZED_WIRE_1, reset => rest3, queren => querenj3, light => zhishideng, alarm => baojing ); --d4触发器例化 b2v_inst4 : d4 port map( clk=>shizhongxinhao, a=>jianpanshurru, rest1=>rest, querenj1=>querenj, gaimij1=>gaimij, shanchuj1=>shanchuj, q=>key, rest2=>rest3, querenj2=>querenj3, gaimij2=>gaimij3, shanchuj2=>shanchuj3, oclk=>ok); END;

D4触发器:d4.vhd

--D触发器:实现消抖作用 library ieee; use ieee.std_logic_1164.all; --d4触发器实体描述 entity d4 is port( clk:in std_logic; a: in std_logic_vector(3 downto 0); rest1,querenj1,gaimij1,shanchuj1:in std_logic; q:out std_logic_vector(3 downto 0); rest2,querenj2,gaimij2,shanchuj2:out std_logic; --表示按键按下信号 以及删除键按下信号 oclk:out std_logic); end d4; --d4结构体描述 architecture f of d4 is signal qi:integer range 0 to 200; signal clk_temp,delay:std_logic; begin process(clk) begin if rising_edge(clk) then if qi=200 then qi<=0; clk_temp<= '1'; else qi<=qi+1; clk_temp<= '0'; end if; end if; end process; process(clk_temp) begin if clk_temp 'event and clk_temp ='1' then if a/="0000" then q <=a; oclk<='1'; elsif shanchuj1/='0' then shanchuj2<='1'; oclk<='1'; else shanchuj2<='0'; oclk<='0'; end if; rest2<=rest1;querenj2<=querenj1; gaimij2<=gaimij1; end if; end process; end if;

数码管显示模块:yimasc.vhd

--数码管显示部分代码 library ieee; use ieee.std_logic_1164.all; --实体描述 entity yimasc is port( --显示数据 datain:in std_logic_vector(15 downto 0); clk:in std_logic; --数码管输出 dataout:out std_logic_vector(15 downto 0)); end yimasc; --结构体描述 architecture behave of yimasc is begin process(clk) begin if clk'event and clk='1' then dataout<=datain; end if; end process; end behave;

移位寄存器模块:ywjcq.vhd

--移位寄存器,用于保存四位密码、删除密码控制 library ieee; use ieee.std_logic_1164.all; --实体描述 entity ywjcq is port( --按键输入(一位) input:in std_logic_vector(3 downto 0); --重新输入,删除,输入脉冲 rest,shanchu,clk :in std_logic; --密码输出 output :out std_logic_vector(15 downto 0)); end ywjcq; --结构体描述 architecture behave of ywjcq is begin process(clk,shanchu) variable output_tmp: std_logic_vector(15 downto 0):="1111111111111111"; variable ok:std_logic:='0'; begin if rest='1' then output_temp:="1110111011101110"; elsif (rising_edge(clk)) then if shanchu='0' then output_temp(15 downto 12):=output_temp(11 downto 8); output_temp(11 downto 8):=output_temp(7 downto 4); output_temp(7 downto 4):=output_temp(3 downto 0); output_temp(3 downto 0):=input; else output_temp(3 downto 0):=output_temp(7 downto 4); output_temp(7 downto 4):=output_temp(11 downto 8); output_temp(11 downto 8):=output_temp(15 downto 12); output_temp(15 downto 12):="1110"; end if; end if; output<=output_temp; end process; end behave;

验证改密模块:yzgm.vhd

--验证改密模,验证密码以及改密 library ieee; use ieee.std_logic_1164.all; --模块试题描述 entity yzgm is port ( --时钟信号,改密键,确认键 clk,gaimij2,queren:in std_logic; --输入密码 input2:in std_logic_vector(15 downto 0); --锁信号,1:表示验证通过 0:表示验证未通过 output2:out std_logic); end yzgm; --结构体描述 architecture a of yzgm is begin process (clk,gaimij2) --设置初始密码是:8421 variable input2_temp:std_logic_vector(15 downto 0):="1000010000100001"; --万能密码为:8888 variable input2_temp1:std_logic_vector(15 downto 0):="1000100010001000"; begin if clk'event and clk='1' then --改密 if gaimij2='1' then input2_temp :=input2; end if; --验证 if queren='1' then if input2_temp=input2 or input2=input2_temp1 then output2<='1'; else output2<='0'; end if; end if; end if; end process; end a;

以上就是工程需要建立的相关文件,工程建立以后,就直接编译,然后配置好引脚烧录就行。

3.答辩讲解PPT(点击下载PPT):

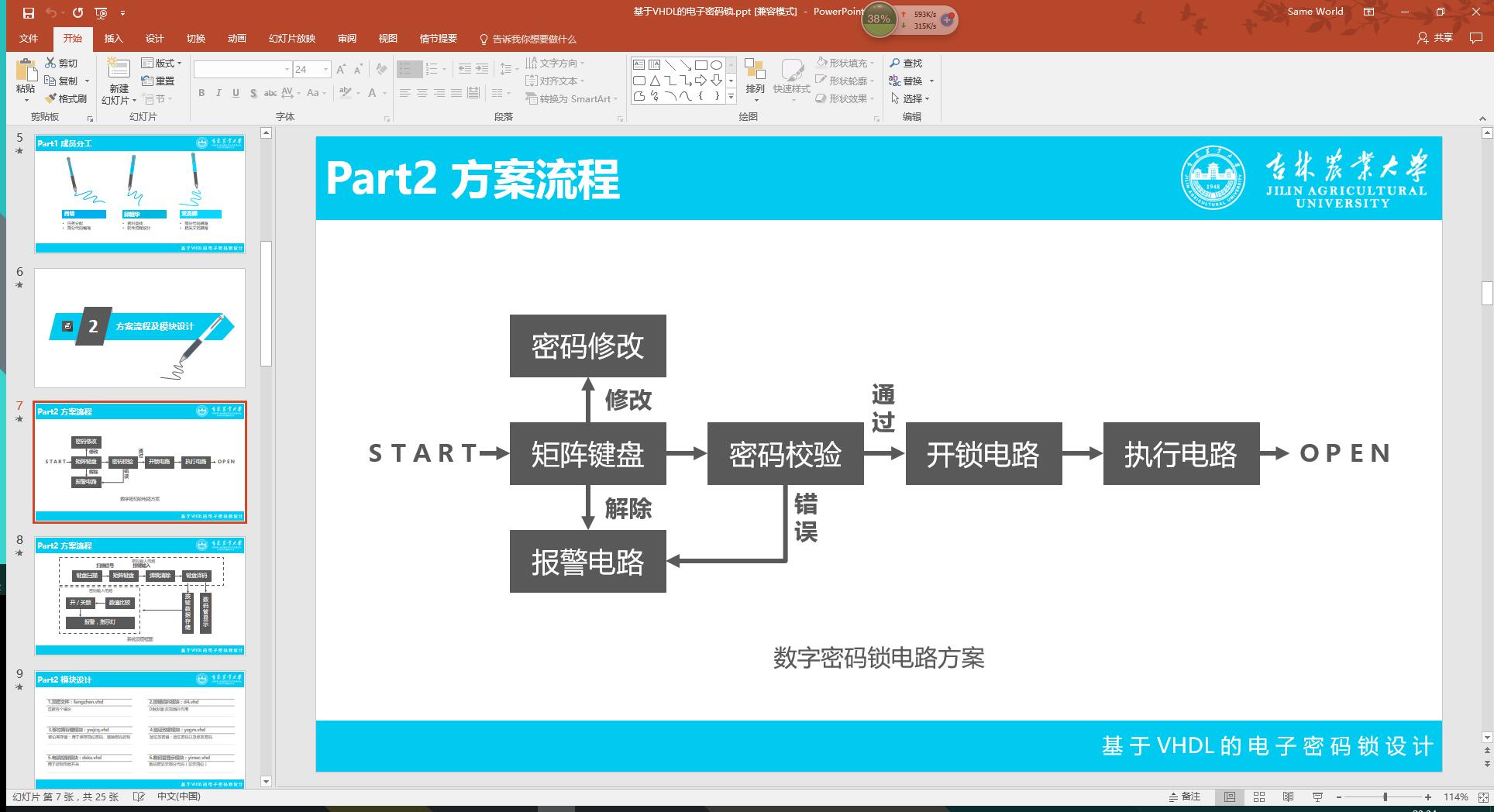

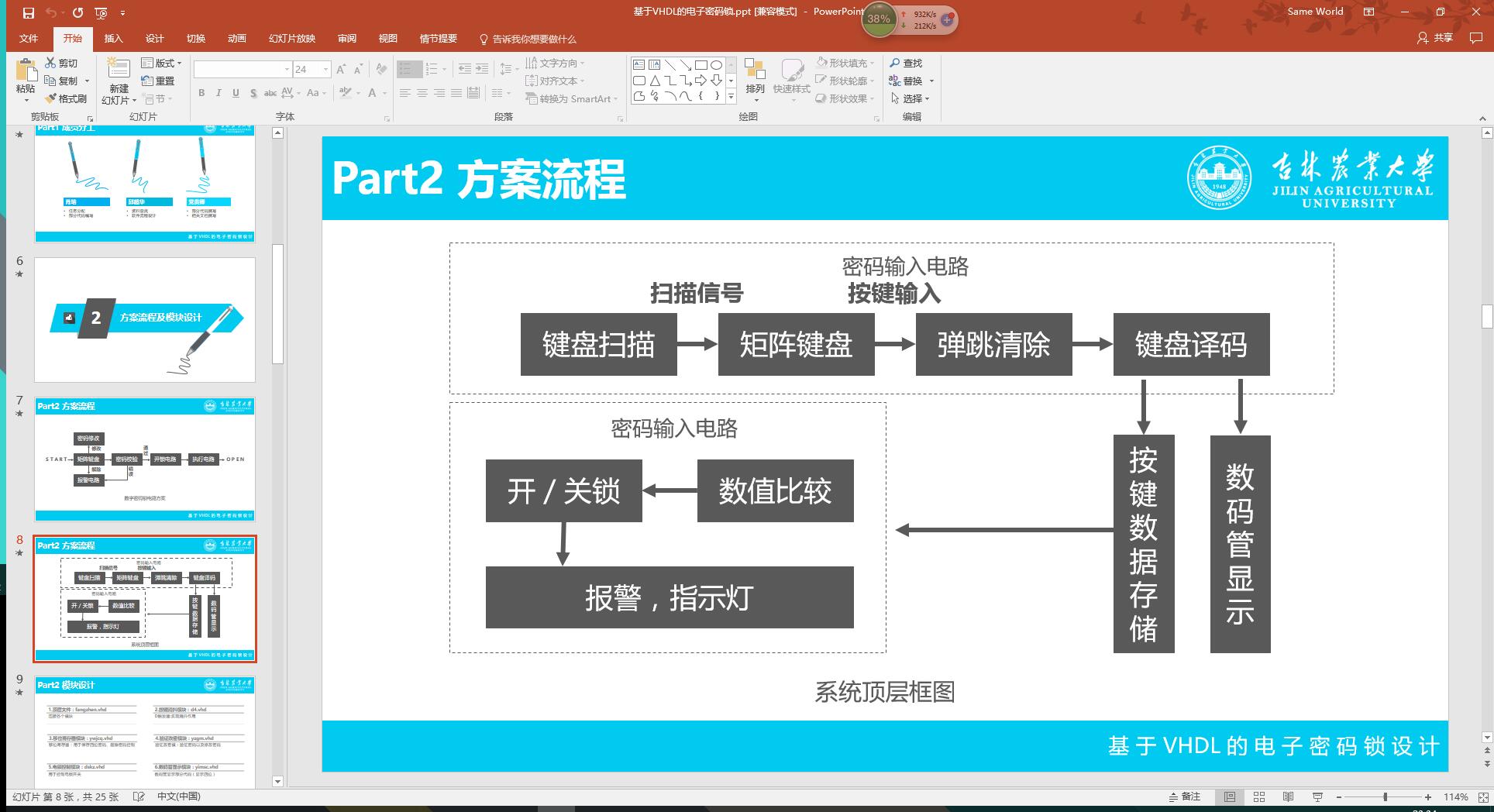

像这种课程设计类的答辩基本就是这种模式,首先讲题目要求,然后方案,接下来就是源码讲解,最后就是试验中遇到的问题以及随便写一些心得体会就行。

部分PPT截图:

转载于:https://blog.51cto.com/970076933/1900388

最后

以上就是快乐枫叶最近收集整理的关于VHDL课程设计:四位电子密码锁(附答辩PPT)的全部内容,更多相关VHDL课程设计内容请搜索靠谱客的其他文章。

发表评论 取消回复