触 发 器

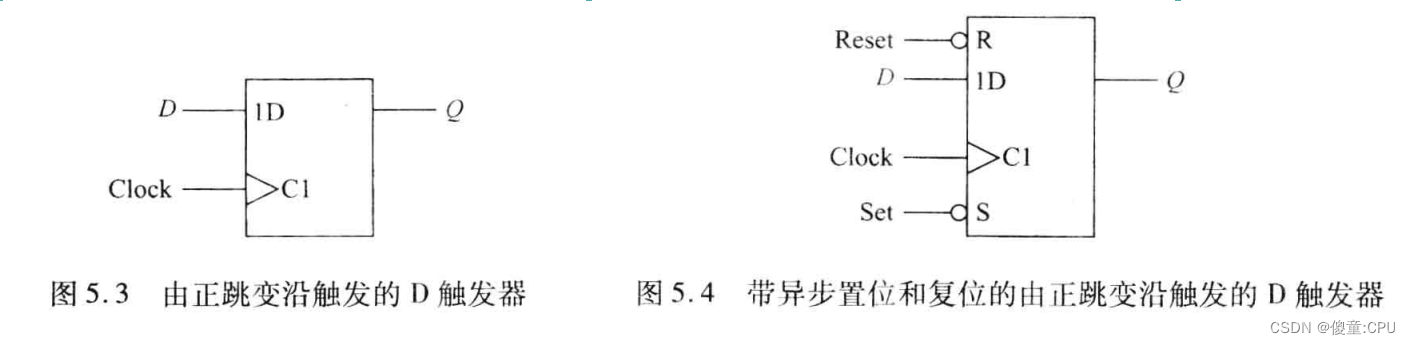

由正跳变沿触发的D触发器的最简单的SystemVerilog模型如下所示:

module dff loutput logic q, input logic d,clk);

always_ff @(posedge clk)

q<=d;

endmodule

因为这是时序逻辑,所以必须用非阻塞赋值。同样,负跳变沿触发的触发器可以通过检测逻辑电平从1跳变到0来建立模型。

异步置位和复位

这两个输入应该只用于触发器的初始化。在系统正常运行期间,用R和S信号来设置触发器的状态是一个坏习惯,必须改正。这样做是因为在同步系统中,触发器的状态改变只允许由时钟的跳变沿触发。由于置位或复位输人信号是异步的,因此不能确保触发器输出的改变发生在特定时刻。这会引起各种时序问题。总而言之,在设计中必须保持严格的同步,或者遵循结构化的异步设计方法,才能设计出稳定可靠的时序电路。

下面是一个带异步复位的D触发器的SystemVerilog模型,该触发器的输出变化必须发生在时钟的正跳变沿和复位信号的负跳变沿时刻:

module dffr (output logic q,

input logicd,clk,n_reset);

always ff @(posedge clk,negedge n_reset)

if(~n_reset)

q <= '0;

else

q <= d;

endmodule

最后

以上就是任性皮带最近收集整理的关于触 发 器的全部内容,更多相关触内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复