一、RS锁存器解析

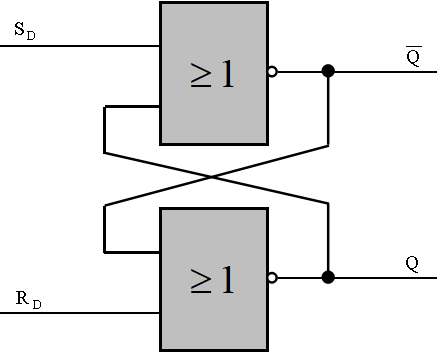

1.1 由两个或非门组成的如下图所示RS锁存器

SD 、RD 分别作为锁存器的输入端,Q'、Q为锁存器输出端。

我们在这里可以将输入端SD当作SET,即置位;将RD当作RESET,即复位。这也便是RS的锁存器名为RS锁存器的原由。

| 输入 | 输出 | ||

| SD | RD | Q' | Q |

| 0 | 0 | X | X |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 1 |

| 1 | 1 | 0 | 0 |

通过真值表我们不难发现

- 当锁存器输入端SD、RD 同时为0时,Q'、Q输出为X;

- 当SD=0、RD=1 输出端Q=0,即复位有效;

- 当SD=1、RD=0 输出端Q=1,即置位有效;

- 当SD=1,RD=1 虽然Q=0,但是Q`=0,(事实上Q是不可能等于Q'的)这种情况实际是不存在的;而且输入端SD与RD同时等于1,这也是存在矛盾的,因为不可能让一个电路即复位又同时置位。

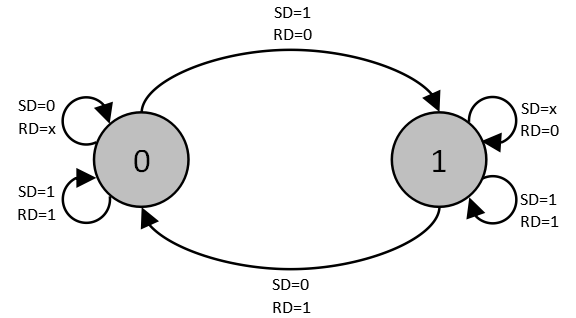

接下来我通过状态图来帮助大家理解RS锁存器到底是怎样实现所存的。

如上图所示,灰色圆圈内0,1分别代表Q的值。

- 当Q=0时,只有SD=1、RD=0,Q的值才会改变为1,其他情况均保持不变(即锁存);

- 当Q=1时,只有SD=0,RD=1,Q的值才会改变为0,其他情况均保持不变(即锁定)。

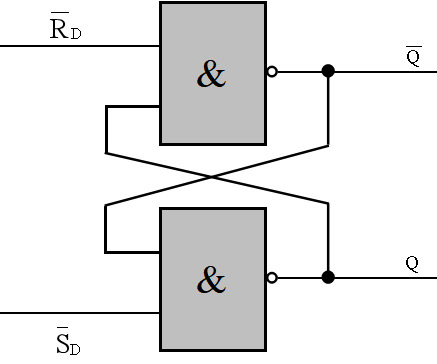

1.2 由与非门组成的RS锁存器

如上图所示RD'和SD'是电路的输入端,Q'与Q是电路的输出端。同样我们可以通过电路得到真值表。

| 输入 | 输出 | ||

| RD' | SD' | Q' | Q |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 1 |

| 1 | 1 | x | x |

通过真值表我们不难发现,由与非门组成的RS锁存器逻辑功能和或非门一致,只不过与非门组成的电路输入为负逻辑,即(输入0“有效”,1“无效”)。

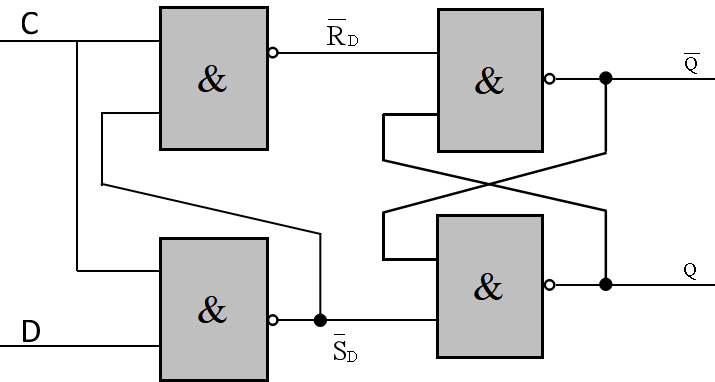

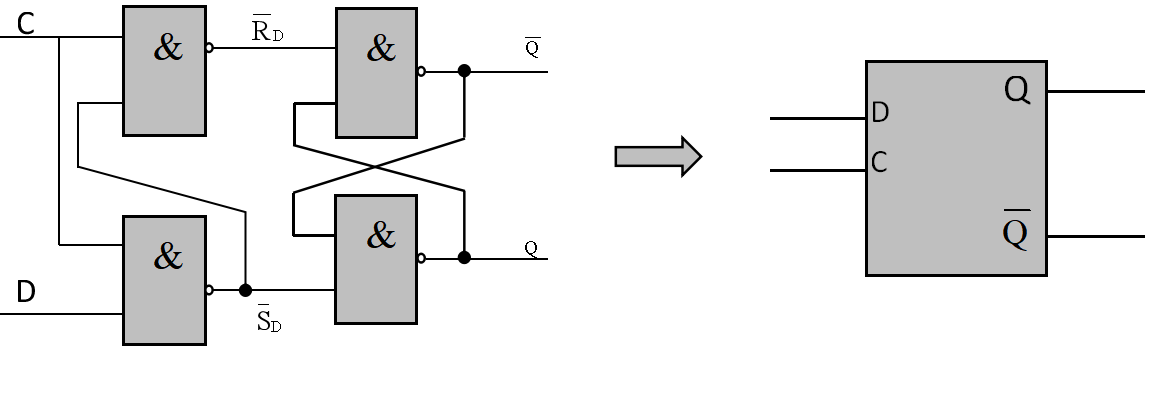

1.3 D锁存器

如上图所示,C、D为电路的输入端,Q'和Q为电路的输出端,同样我们可以得到真值表。

| 输入 | 中间信号 | 输出 | |||

| C | D | RD' | SD' | Q' | Q |

| 0 | 0 | 1 | 1 | x | x |

| 0 | 1 | 1 | 1 | x | x |

| 1 | 0 | 0 | 1 | 1 | 0 |

| 1 | 1 | 1 | 0 | 0 | 1 |

通过真值表总结如下:

当C=0,无论D取何值,中间信号RD'和SD'的值确定,Q的值未知

当C=1,Q=D

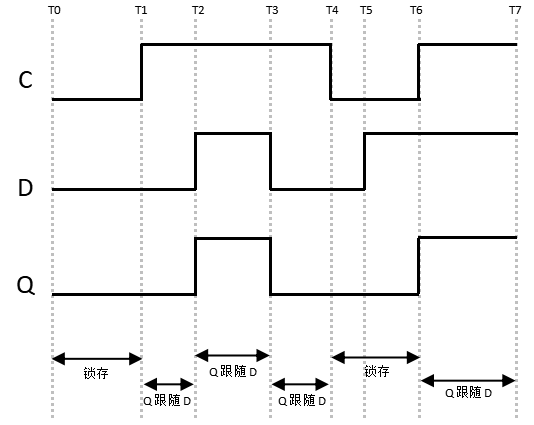

由此我们可以将输入端C当作电路的“使能”端。下面由电路的波形图加以说明:

在T0-T1和T4-T6时间段C=0,Q值保持次态实现锁存。

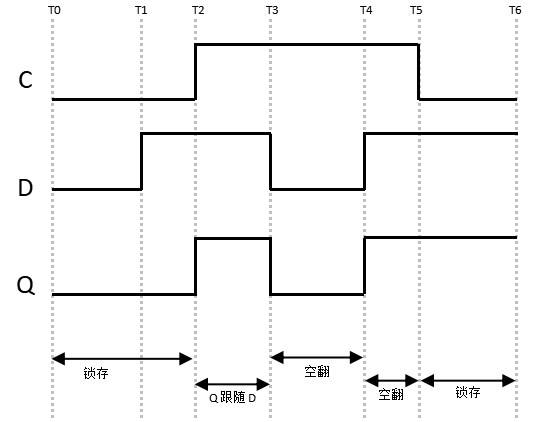

实际D锁存器还存在一种特殊情况——“空翻”。

如上图所示,C=1时,输入端D发生多次翻转,Q也随之发生多次翻转,因此将Q的多次翻转称为空翻,这种情况是无利的。在实际应用时需要避免,同时因此才诞生触发器。

二、D触发器

2.1 D触发器

如上图所示将左侧图的电路用右侧图的符号代替。

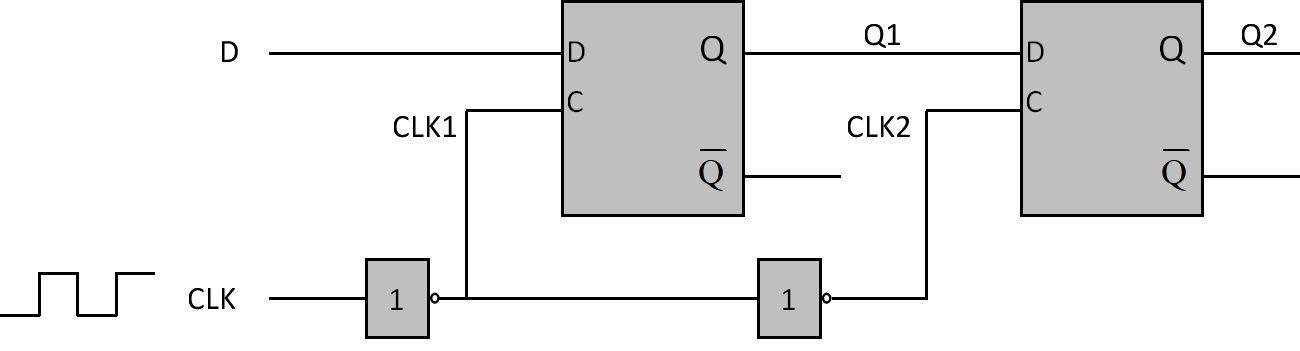

如上图所示由两个D锁存器组成的主从D触发器,其中D、CLK是电路的输入,Q'和Q是输出。

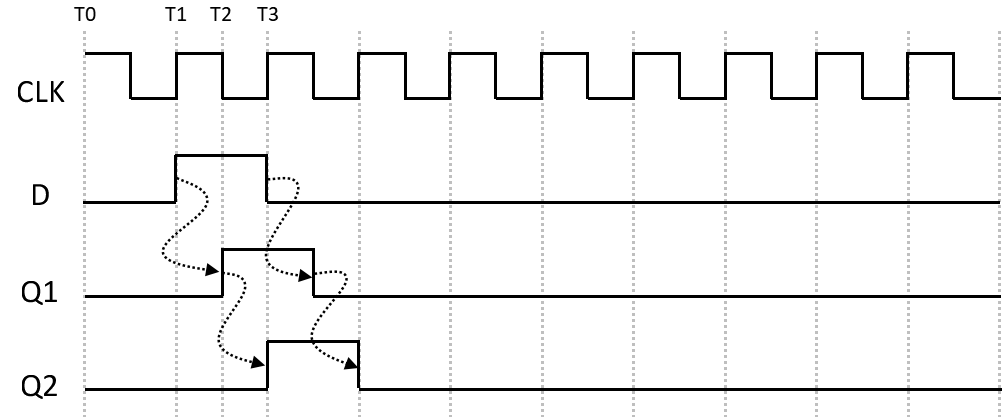

如上图所示是D触发器的波形图,此时我们发现输入端D,输出端Q2则是通过CLK的上升沿来触发改变的。这也是触发器与锁存器最大的区别。同时这也是时序电路的雏形。

三、寄存器

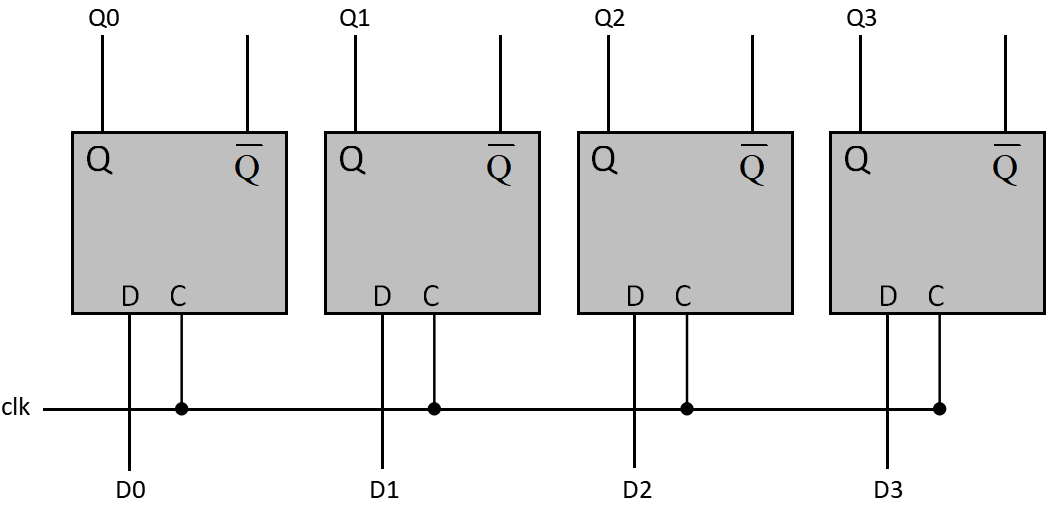

如上图所示,由四个D触发器组成的四位宽寄存器。(在时钟端clk的驱动下,输入端D0-D3输入的数据被寄存器到输出端Q0-Q3)。

四、移位寄存器

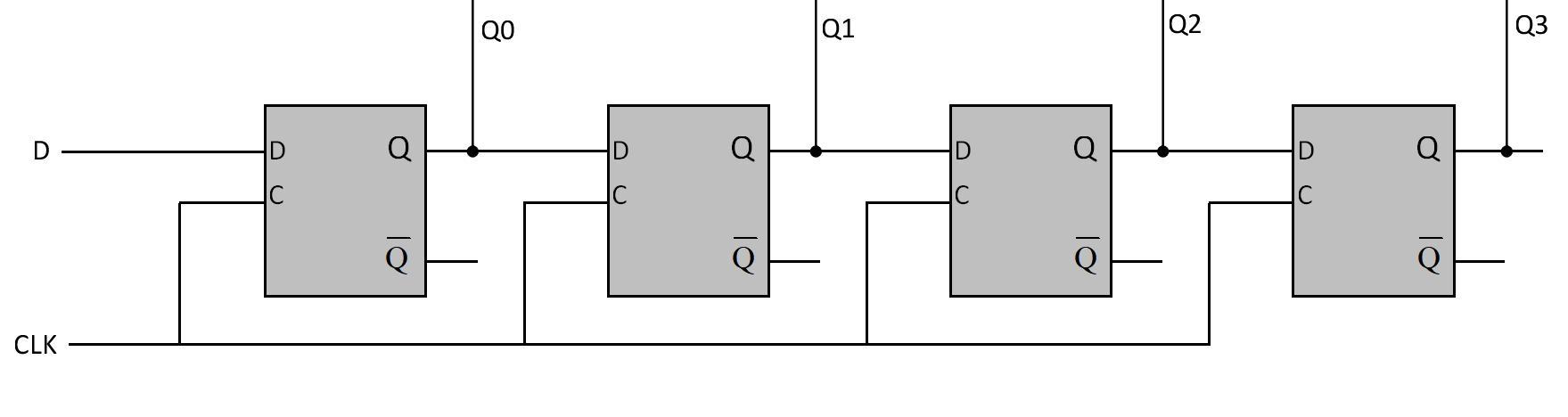

如上图所示由四个D触发器组合的移位寄存器,数据输入端D在时钟输入端clk的驱动下,每一个时钟脉冲数据依次向右移动。

最后

以上就是正直小虾米最近收集整理的关于锁存器、触发器、寄存器、移位寄存器、计数器的全部内容,更多相关锁存器、触发器、寄存器、移位寄存器、计数器内容请搜索靠谱客的其他文章。

发表评论 取消回复