基本数字电路的Verilog实现

1.半加器

module halfadd(x,y,s,cout);

input x;

input y;

output s;

output cout;

assign s = x^y;

assign cout = x&y;

endmodule

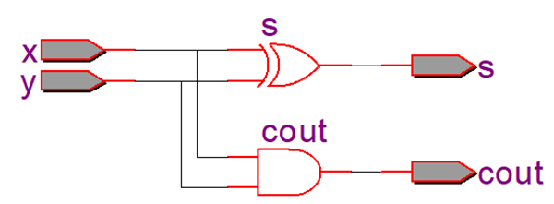

半加器RTL视图

半加器RTL视图

2.全加器

module fulladd(cin,x,y,s,cout);

input cin;

input x;

input y;

output s;

output cout;

assign s = xycin;

assign cout = (x&y)|(x&cin)|(y&cin);

//assign {cout,s}=x+y+cin;

endmodule

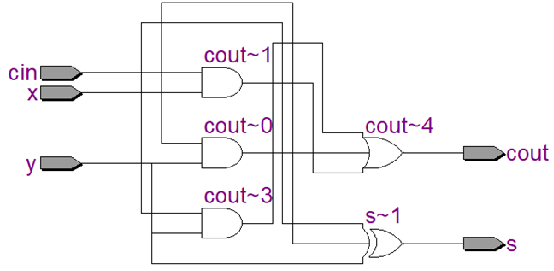

全加器RTL视图

3.4位全加器

module FA_4(x,y,cin,s,cout);

input [3:0] x;

input [3:0] y;

input cin;

output wire cout;

output wire [3:0] s;

assign {cout,s}=x+y+cin;

endmodule

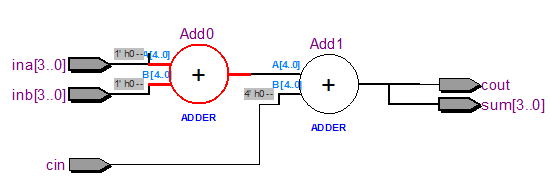

4位全加器RTL视图

4.二选一

module MUXtwo_one(sel,a,b,c);

input sel,a,b;

output reg c;

//assign c=sel?a:b;

always@(*)begin

if(sel==1'b1)

c=a;

else

c=b;

end

endmodule

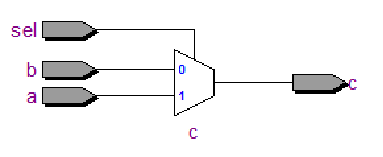

二选一RTL视图(两种描述方式综合后视图一样)

5.四选一

module MUX4_1(

input en,

input [3:0] din,

input [1:0] sel,

output reg out

);

always@(en,din,sel) //case语句描述

begin

if(en)

out=0;

else

case(sel)

2’d0:out=din[0];

2’d1:out=din[1];

2’d2:out=din[2];

2’d3:out=din[3];

endcase

end

/*always@(en,din,sel) //if-else语句描述

begin

if(en)

out=0;

else if(sel==2'd0) out=din[0];

else if(sel==2'd1) out=din[1];

else if(sel==2'd2) out=din[2];

else out=din[3];

end*/

endmodule

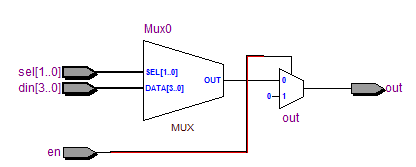

四选一(case语句)RTL视图

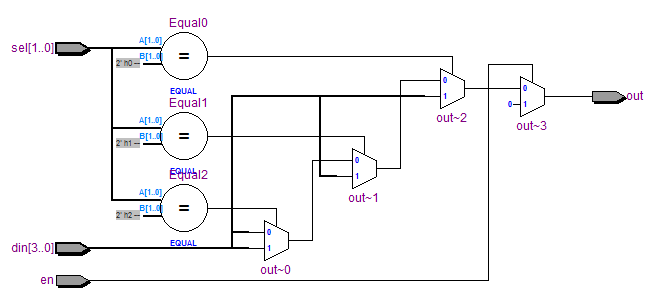

四选一(if-else语句)RTL视图

四选一(if-else语句)RTL视图

6.四位计数器

module jsq(

input clk,

input rst_n,

output reg [3:0] out

);

always@(posedge clk or negedge rst_n)

begin

if(rst_n==1’b0)

out<=4’d0;

else

out<=out+1’b1;

end

endmodule

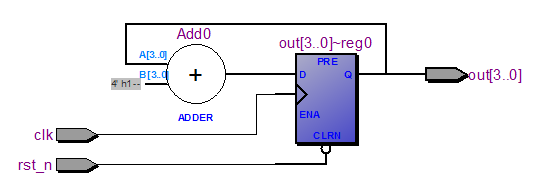

四位计数器RTL视图

7.3-8译码器

module ym3_8(Ain,En,Yout);

input En ;

input [2:0] Ain ;

output [7:0] Yout ;

reg [7:0] Yout ;

always@(En or Ain)

begin

if(!En)

Yout = 8'b0 ;

else

case (Ain)

3'b000 : Yout = 8'b0000_0001 ;

3'b001 : Yout = 8'b0000_0010 ;

3'b010 : Yout = 8'b0000_0100 ;

3'b011 : Yout = 8'b0000_1000 ;

3'b100 : Yout = 8'b0001_0000 ;

3'b101 : Yout = 8'b0010_0000 ;

3'b110 : Yout = 8'b0100_0000 ;

3'b111 : Yout = 8'b1000_0000 ;

default : Yout = 8'b0000_0000 ;

endcase

end

endmodule

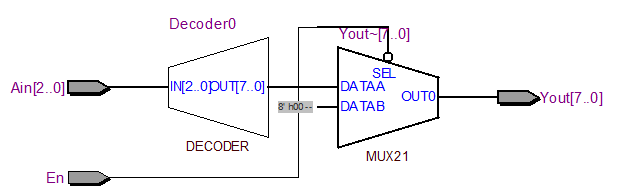

3-8译码器RTL视图

最后

以上就是粗暴机器猫最近收集整理的关于基本数字电路的Verilog实现的全部内容,更多相关基本数字电路内容请搜索靠谱客的其他文章。

发表评论 取消回复