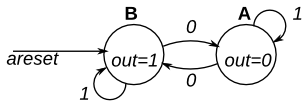

119 fsm1

This is a Moore state machine with two states, one input, and one output. Implement this state machine. Notice that the reset state is B.

This exercise is the same as fsm1s, but using asynchronous reset.

Hint...Yes, there are ways to do this other than writing an FSM. But that wasn't the point of this exercise.Hint...

This is a TFF with the T input inverted.

module top_module(

input clk,

input areset, // Asynchronous reset to state B

input in,

output out);//

parameter A=1'd0, B=1'd1;

reg state, next_state;

always @(*) begin // This is a combinational always block

// State transition logic

case(state)

A:next_state = (in)?A:B;

B:next_state = (in)?B:A;

endcase

end

always @(posedge clk, posedge areset) begin // This is a sequential always block

// State flip-flops with asynchronous reset

if(areset)begin

state<=B;

end

else begin

state<=next_state;

end

end

// Output logic

assign out = (state == B);

endmodule

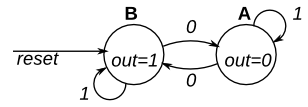

120 fsm1s

This is a Moore state machine with two states, one input, and one output. Implement this state machine. Notice that the reset state is B.

This exercise is the same as fsm1, but using synchronous reset.

Hint...Yes, there are ways to do this other than writing an FSM. But that wasn't the point of this exercise.Hint...

This is a TFF with the T input inverted.

module top_module(

input clk,

input reset, // Asynchronous reset to state B

input in,

output out);//

parameter A=1'd0, B=1'd1;

reg state, next_state;

always @(*) begin // This is a combinational always block

// State transition logic

case(state)

A:next_state = (in)?A:B;

B:next_state = (in)?B:A;

endcase

end

always @(posedge clk) begin // This is a sequential always block

// State flip-flops with asynchronous reset

if(reset)begin

state<=B;

end

else begin

state<=next_state;

end

end

// Output logic

assign out = (state == B);

endmodule

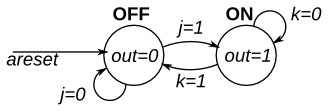

121 fsm2

This is a Moore state machine with two states, two inputs, and one output. Implement this state machine.

This exercise is the same as fsm2s, but using asynchronous reset.

Module Declaration

Hint...Yes, there are ways to do this other than writing an FSM. But that wasn't the point of this exercise.Hint...

This is a JK flip-flop.

module top_module(

input clk,

input areset, // Asynchronous reset to OFF

input j,

input k,

output out); //

parameter OFF=1'd0, ON=1'd1;

reg state, next_state;

always @(*) begin

// State transition logic

case (state)

ON:next_state = k?OFF:ON;

OFF:next_state = j?ON:OFF;

endcase

end

always @(posedge clk, posedge areset) begin

// State flip-flops with asynchronous reset

if(areset)begin

state <= OFF;

end

else begin

state <= next_state;

end

end

// Output logic

assign out = (state == ON);

endmodule

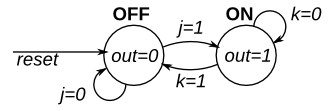

122 fsm2s

This is a Moore state machine with two states, two inputs, and one output. Implement this state machine.

This exercise is the same as fsm2, but using synchronous reset.

Hint...Yes, there are ways to do this other than writing an FSM. But that wasn't the point of this exercise.Hint...

This is a JK flip-flop.

module top_module(

input clk,

input reset, // Asynchronous reset to OFF

input j,

input k,

output out); //

parameter OFF=1'd0, ON=1'd1;

reg state, next_state;

always @(*) begin

// State transition logic

case (state)

ON:next_state = k?OFF:ON;

OFF:next_state = j?ON:OFF;

endcase

end

always @(posedge clk) begin

// State flip-flops with asynchronous reset

if(reset)begin

state <= OFF;

end

else begin

state <= next_state;

end

end

// Output logic

assign out = (state == ON);

endmodule

最后

以上就是微笑斑马最近收集整理的关于HDLBits练习 119-122 FSM(1)119 fsm1120 fsm1s121 fsm2122 fsm2s的全部内容,更多相关HDLBits练习内容请搜索靠谱客的其他文章。

发表评论 取消回复