数据实现时钟时钟区域穿越,也就是从一个时钟区域传递到另外一个时钟区域,要使用寄存器穿越(暂且用穿越,我词穷了~),必须注意两点:1,每次变化只有一位,这样是为了尽量减少另外一个时钟采样误差;2,要打两个以上拍子,这样防止到了目标时钟域后产生亚稳态(就是寄存器被不同的区域所采样得到的结果不一致)。

以上两个条件中打两个拍子不是问题,主要是问题是传递寄存器一次只变化一位的规定(大家都遵守的最小出错率约定,尤其是在芯片设计中)。因为我们要传递的寄存器位数无法预知,内容更无法预知。

在FPGA可以实现一种双时钟的RAM,就是说都和谐使用不同时钟,只要读写口各自满足建立保持条件,对同地址的读写注意保持在算法层面的同步,就不会出错。这个双时钟RAM可以说就是为了实现时钟穿越而生。但是这个确定在于还需要另外的实现读写双方时钟区域的逻辑,

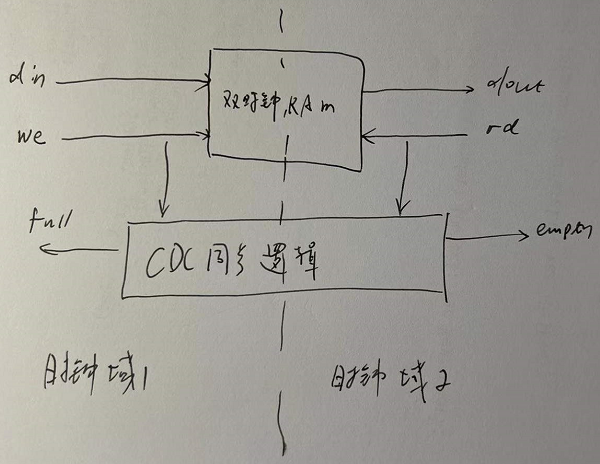

结合上述面寄存器穿越时钟域和双时钟RAM实现的优缺点,我们可以用双时钟RAM实现数据传递,用寄存器穿越时钟实现同步和控制信号传递。这种典型的实现就是双时钟FIFO,一般写DC_FIFO,这里DC就是就是DualClock的意思。

这里CDC 就是咱们上述说的时钟区域穿越Clock Domain Crossing.上图比较清晰展示了一个双时钟FIFO中RAM和控制逻辑分工和协同。

在上篇https://blog.csdn.net/mcupro/article/details/121849662中给出了opencores.org里一个开源DC_FIFO的源码。我们可以在代码中看到上述思路写的DC FIFO。

另外对时钟区域穿越先深入分析一下可以参考:fpga4fun.com - Crossing clock domains

原则上穿越时钟导致错误概率存在,我们上述做的努力就是降低其概率使之可忽略。实际上使用上述的同步逻辑或者RAM或者两者组成的FIFO,是可以将错误概率降低我极小,我在实际设计中没有遇到异步时钟穿越导致的错误。

最后

以上就是无聊玉米最近收集整理的关于双时钟先入先出队列DC_FIFO的时钟基本思路的全部内容,更多相关双时钟先入先出队列DC_FIFO内容请搜索靠谱客的其他文章。

发表评论 取消回复