一.引言

E D A技术在当今社会为现代电子设计领域提供了可能性,这也是E D A 技术飞速发展的理由。现如今,E D A技术不再是某一门课程的分支,也不是某种新的技术,而是一门综合性学科。让计算机软件与计算机硬件相结合,他代表了电子设计技术的不断发展方向。

在当今社会EDA技术为现代电子设计领域提供了可能性,这也是E D A 技术飞速发展的理由。现如今,E D A技术不再是某一门课程的分支,也不是某种新的技术,而是一门综合性学科。通过计算机软件与计算机硬件相结合,代表了电子设计技术的不断发展方向。

数字钟的应用十分的广泛,每一个家庭,车站,教室等公共场所都应该会有数字钟的身影,给人们带来极大的方便和快捷。

随着科技的进步和人们生活水平的提高,我们对于时钟的要求也在不断的提高。现在时钟已经不再是一个简单的报时工具,在很多特殊的时刻我们还需要用到时钟的其他功能。在这种新形势下,制作数字电子钟成为时代的主流设计和发展方向。数字钟是利用数字电路实现时、分、秒的计时装备,较以往的机械钟具有更强的直观性和准确性,并且延长了时钟的使用寿命。

二.设计目的

12进制数字钟的计时装置的周期是12小时,显示满刻度为11小时59分59秒。

制作数字钟是为了了解数字钟的工作原理和工作过程,能够自主独立的编写和修改各种进制数字钟的语言。熟练使用EDA课程中使用的软件和将所学到的知识理论应用于实践中。并能因为此次实验对EDA程序设计产生浓厚兴趣,因为只有真正喜欢上这门课程,才能在未来的学习中不断进步。

三.实验内容

利用M A X+p l u s II 10.2软件设计12进制数字钟。

四.实验原理和思路

由于我设计的是12进制数字钟,所以在设计过程中我让数字钟在“时”上从0-11循环,在“分”和“秒”上依旧实现0-59的循环。

在《EDA技术与应用》这篇课本p205页中我们可以见到60进制的计数器,我设计的12进制数字钟原理其实和60进制计数器是一样的,不同之处只是12进制是十位在0时,个位实现0-9的循环,十位等于1时,个位实现0-1的循环。

五.数字钟模块设计

5.1“时”程序段设计

过程如下:

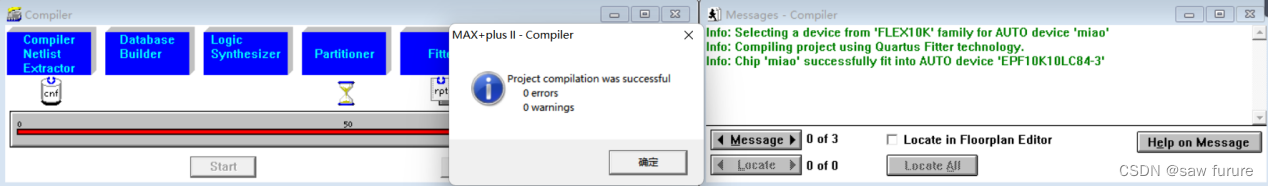

1.打开M A X+p l u sⅡ10.2,新建 Text Editor file

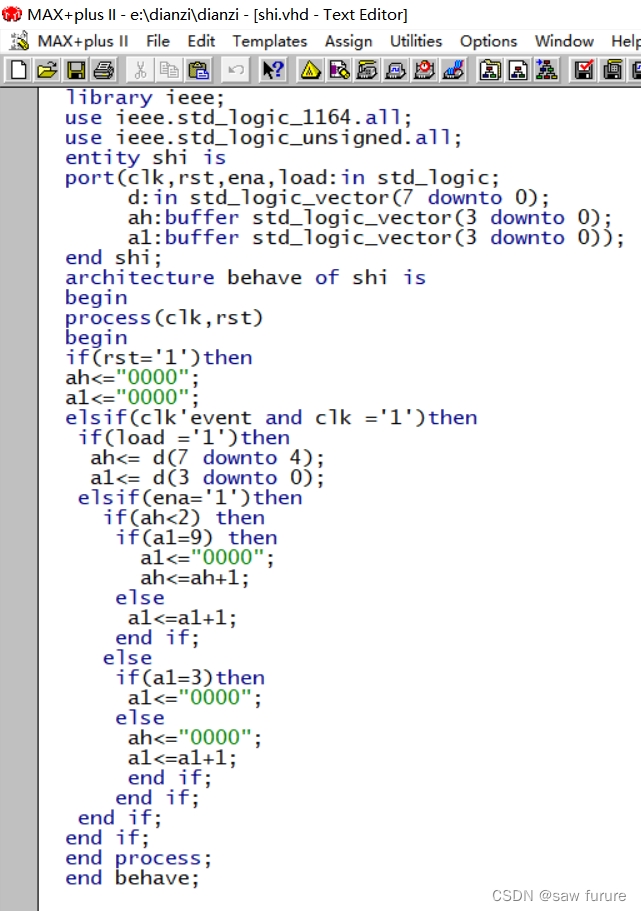

2.编写程序如图:

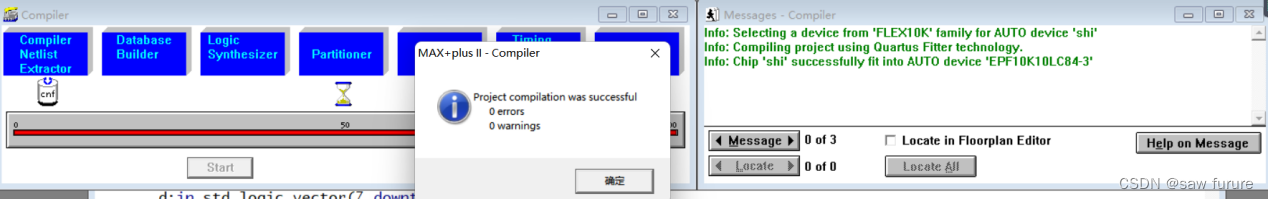

3.点击 ctrl + shift + j 将设计项目设置成工程文件,注意类型为.vhd。

4.点击M A X + p l u s Ⅱ下的compiler进行编译

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity shi is

port(clk,rst,ena,load:in std_logic;

d:in std_logic_vector(7 downto 0);

ah:buffer std_logic_vector(3 downto 0);

a1:buffer std_logic_vector(3 downto 0));

end shi;

architecture behave of shi is

begin

process(clk,rst)

begin

if(rst='1')then

ah<="0000";

a1<="0000";

elsif(clk'event and clk ='1')then

if(load ='1')then

ah<= d(7 downto 4);

a1<= d(3 downto 0);

elsif(ena='1')then

if(ah<2) then

if(a1=9) then

a1<="0000";

ah<=ah+1;

else

a1<=a1+1;

end if;

else

if(a1=3)then

a1<="0000";

else

ah<="0000";

a1<=a1+1;

end if;

end if;

end if;

end if;

end process;

end behave;接下来是“分”设计和“秒”设计原理和“时”是一样的。

5.2“分”程序段设计

“分”的设计过程同上,我们要知道上一个“时”时0-33之间循环。“分”不同在于0-59之间循环。我们仅仅要修改一小部分程序。

用和“时”一样的编写方法编写“分”程序。

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity fen is

port(clk,rst2,ena2,load2:in std_logic;

rco2:out std_logic;

d2:in std_logic_vector(7 downto 0);

ah2:buffer std_logic_vector(3 downto 0);

a12:buffer std_logic_vector(3 downto 0));

end fen;

architecture behave2 of fen is

begin

rco2<='1' when (ah2= "0101" and a12="1001" and ena2 ='1')else'0';

process(clk,rst2)

begin

if(rst2='1')then

ah2<="0000";

a12<="0000";

elsif(clk'event and clk ='1')then

if(load2 ='1')then

ah2<= d2(7 downto 4);

a12<= d2(3 downto 0);

elsif(ena2='1')then

if(a12=9) then

a12<="0000";

if(ah2=5)then

ah2<="0000";

else

ah2<=ah2+1;

end if;

else

a12<=a12+1;

end if;

end if;

end if;

end process;

end behave2;5.3“秒”程序段设计

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

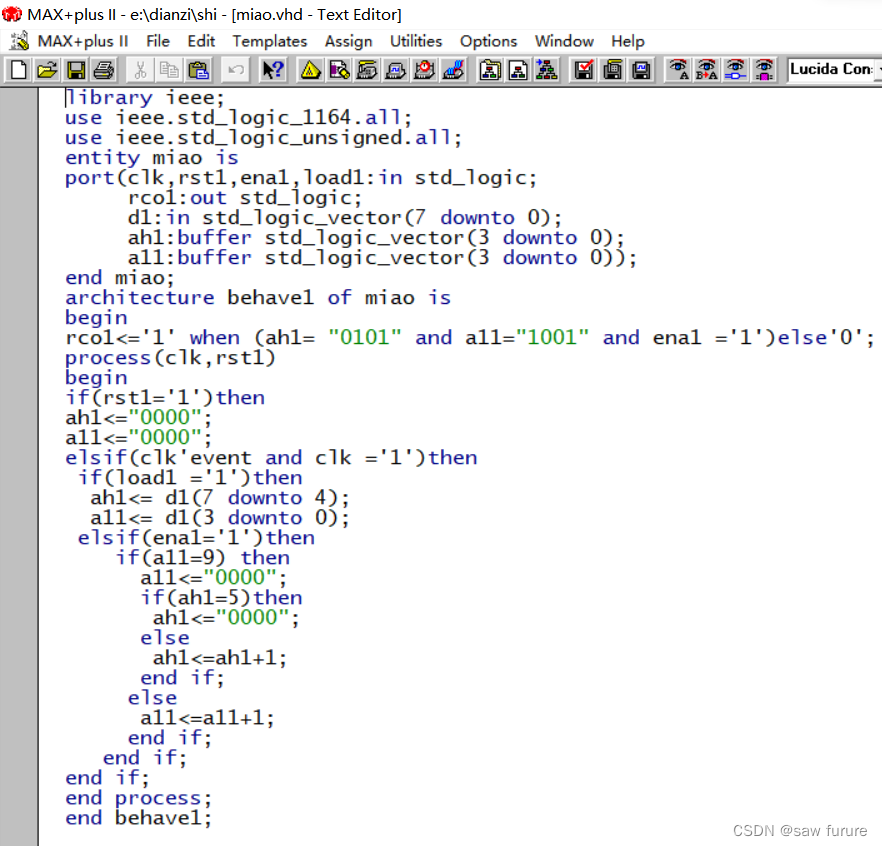

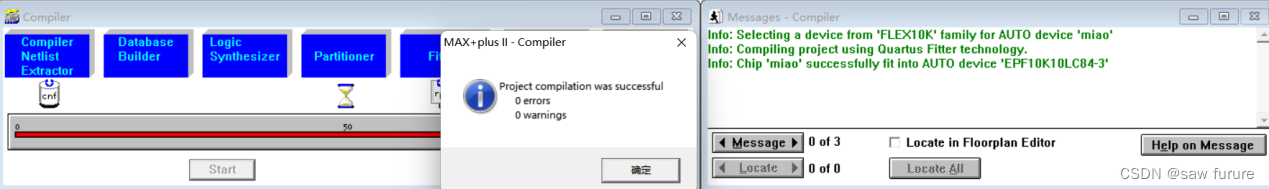

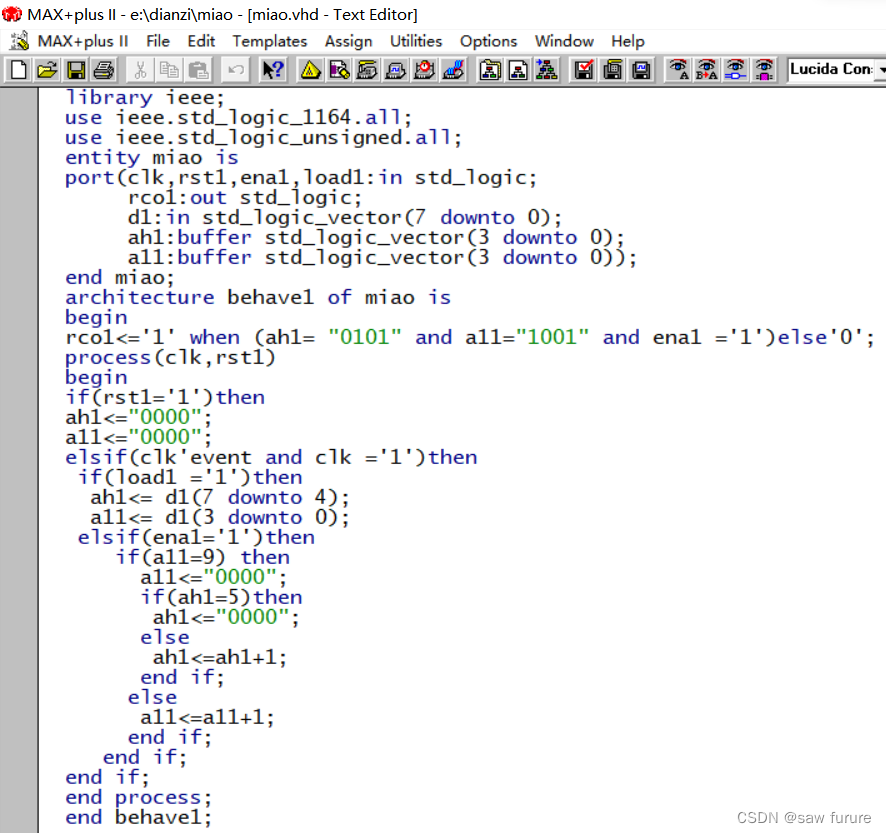

entity miao is

port(clk,rst1,ena1,load1:in std_logic;

rco1:out std_logic;

d1:in std_logic_vector(7 downto 0);

ah1:buffer std_logic_vector(3 downto 0);

a11:buffer std_logic_vector(3 downto 0));

end miao;

architecture behave1 of miao is

begin

rco1<='1' when (ah1= "0101" and a11="1001" and ena1 ='1')else'0';

process(clk,rst1)

begin

if(rst1='1')then

ah1<="0000";

a11<="0000";

elsif(clk'event and clk ='1')then

if(load1 ='1')then

ah1<= d1(7 downto 4);

a11<= d1(3 downto 0);

elsif(ena1='1')then

if(a11=9) then

a11<="0000";

if(ah1=5)then

ah1<="0000";

else

ah1<=ah1+1;

end if;

else

a11<=a11+1;

end if;

end if;

end if;

end process;

end behave1;秒”程序和“分”程序设计是一样的,都可以当成60进制计数来编译,在课本中有详细的介绍,我可以参考课本,不断改进我所编写的程序。

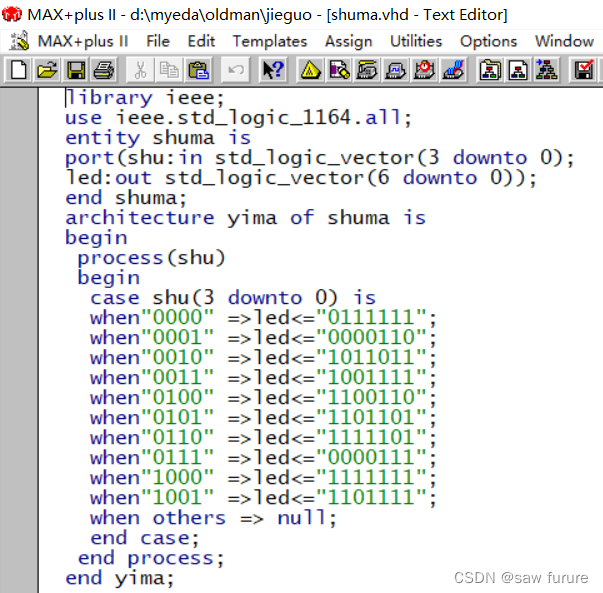

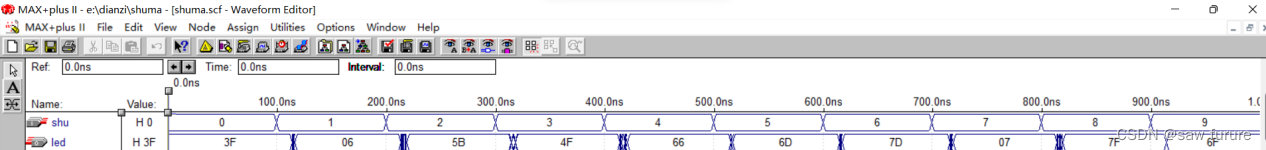

5.4七段显示译码器程序段设计

library ieee;

use ieee.std_logic_1164.all;

entity shuma is

port(shu:in std_logic_vector(3 downto 0);

led:out std_logic_vector(6 downto 0));

end shuma;

architecture yima of shuma is

begin

process(shu)

begin

case shu(3 downto 0) is

when"0000" =>led<="0111111";

when"0001" =>led<="0000110";

when"0010" =>led<="1011011";

when"0011" =>led<="1001111";

when"0100" =>led<="1100110";

when"0101" =>led<="1101101";

when"0110" =>led<="1111101";

when"0111" =>led<="0000111";

when"1000" =>led<="1111111";

when"1001" =>led<="1101111";

when others => null;

end case;

end process;

end yima;六.数字钟的系统设计

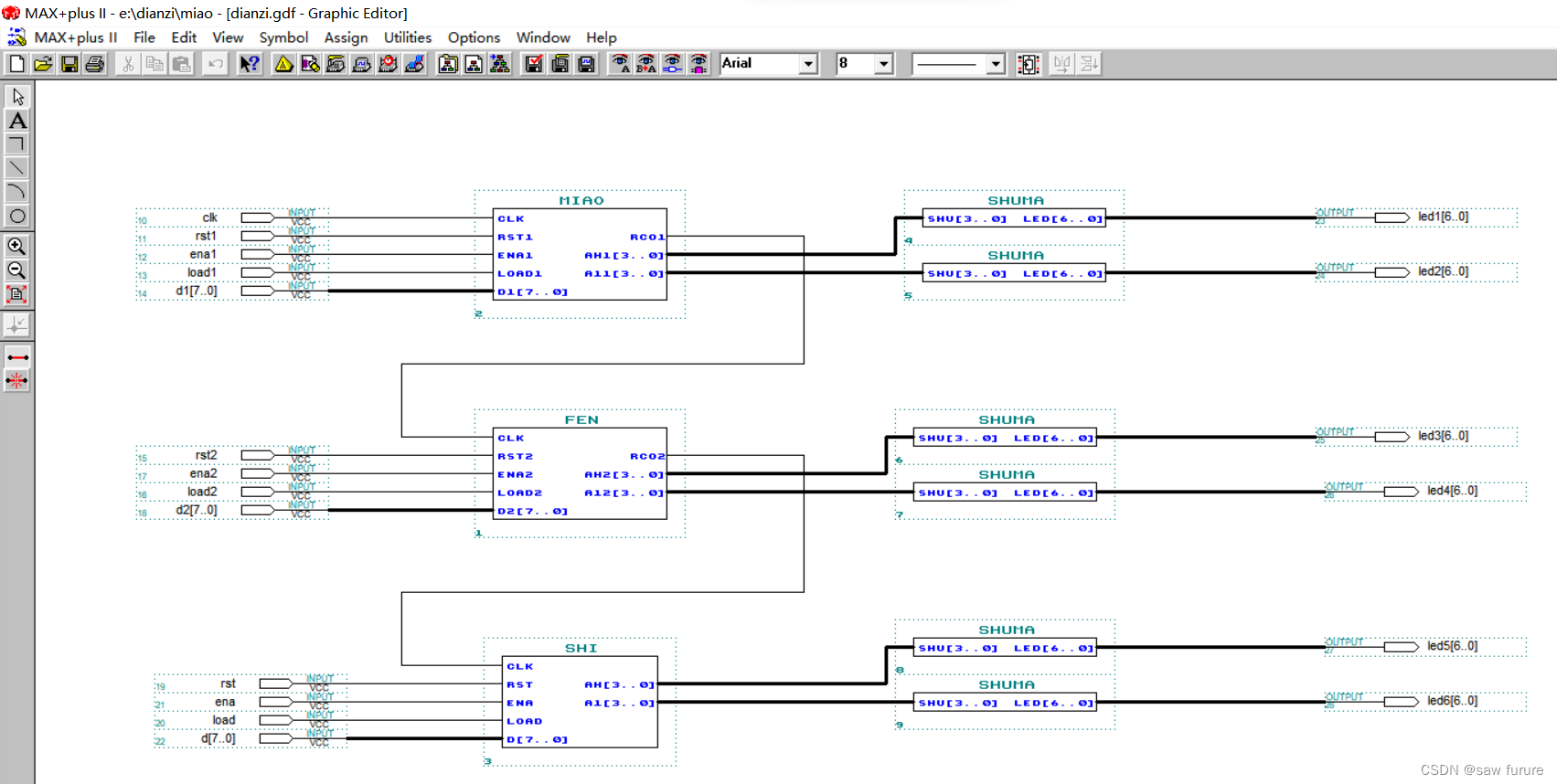

建立完数字钟的“时”“分”“秒”三部分的程序描述,接下来就是设计顶层。我们可以通过点击file下的create default symbol 将我们所编写的三个程序进行封装。将“时”“分”“秒”三个程序组成电路。

1.打开原理图编译器,完成数字钟的设计。

设计图如下:

2.点击ctrl+shift+j将设计项目设置成工程文件。

3.完成数字钟编译.

- 数字钟仿真调试过程

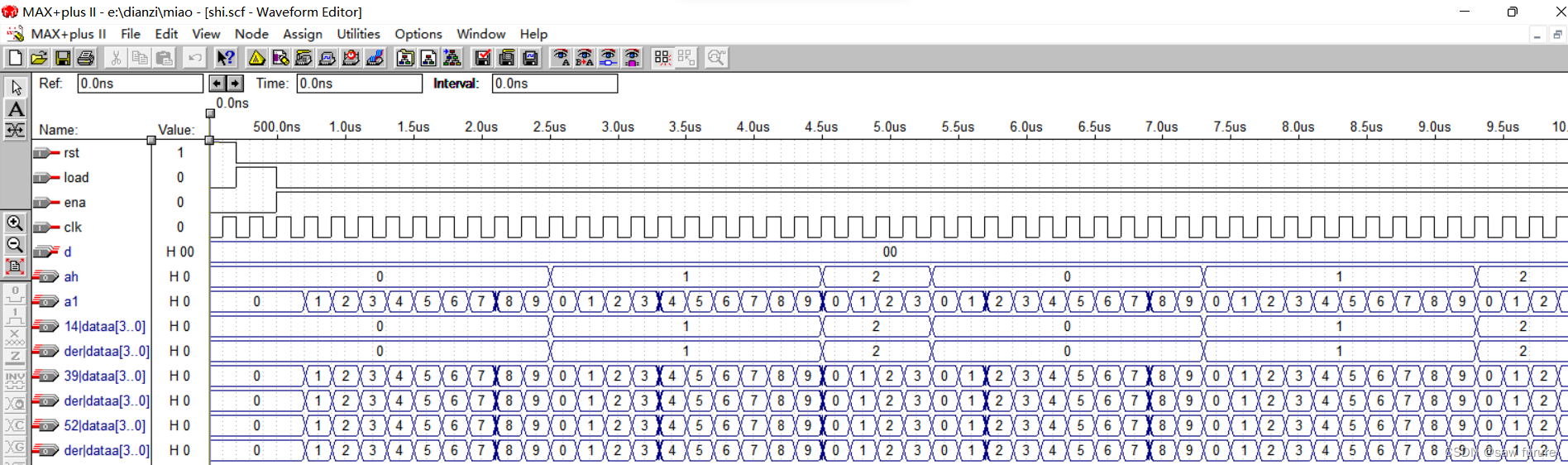

7.1“时”计数器

继续上面编译继续仿真,过程如下:

5.新建一个 Waveform Editor file ,准备仿真

6.点击NODE下的Enter Nodes form SNF,在弹出的窗口中点击list,这时将左窗口列出的设计所有信息节点利用中间的=>转移到右边

7.设置结束时间和时钟脉冲,点击ctrl+shift+j将设计项目设置成工程文件。

8.开始仿真

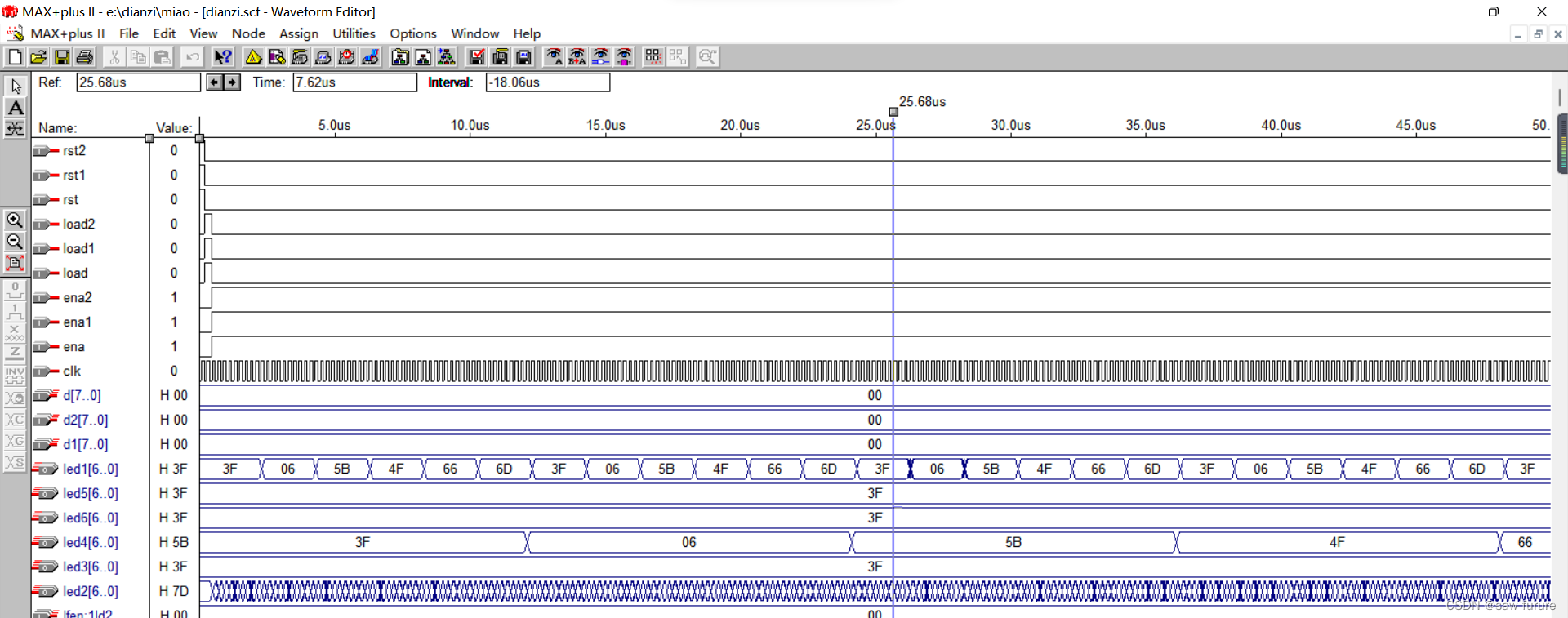

在时计数器的clk端口加入一个 1000ns的时钟信号;reset为高电平;进行仿真

“时”计数器在0-33之间循环,符合之前设计的程序,由此可见,我前面设计的程序是没有问题的。

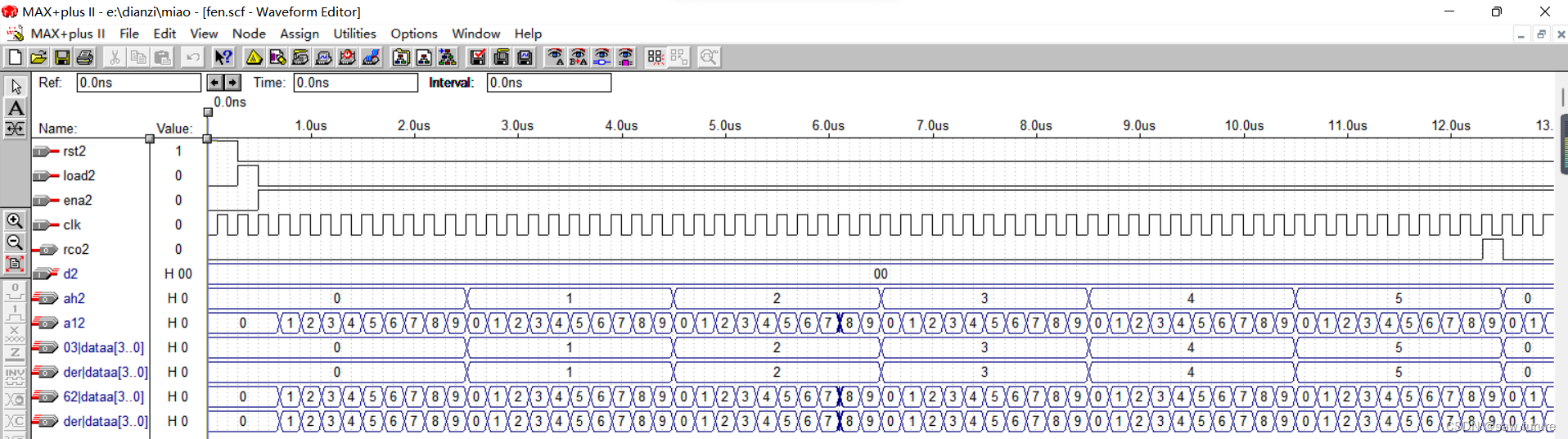

7.2“分”计时器

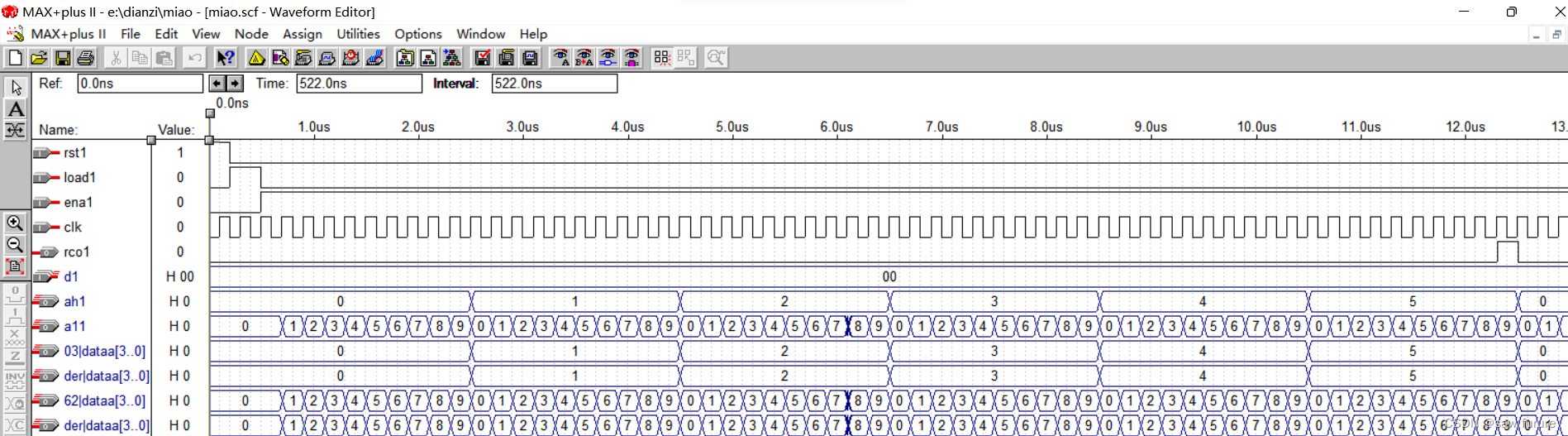

7.3“秒”计时器

7.4七段显示译码器

7.5系统总调试

由最终的仿真结果可以看出我做的数字钟是正确的,当“时”到11时跳转为00,重新开始执行程序,构成循环。“分”和“秒”都是为59时跳转。ena,load,reset是使能端,这三个端口为1时,程序执行。为0时,清零。

- 心得体会

8.1数字钟存在的问题

1 .数字钟采用的是静态译码显示方式,一个数码管需要8根I/O线,八个数码管,会占用很多的I/O线,导致I/O口资源不够用,同时会是成本加大,LED数码管的功耗较大,热量高,浪费资源。

2.随着累加计数的增加,延时的误差会一点点的累加,累加次数越多,技术误差就会越明显。

8.2数字钟改进意见

- 建议把LED静态显示改成动态显示,动态显示方式是通过一位一位地轮流点亮每位LED数码管,即每个数码管的位选被轮流选中,多个数码管公用一组段选,片选数据仅对位选选中的数码管有效。对于每一位数码管来说,每隔一段时间点亮一次。显示器的亮度通过导通电流,点亮时间和间隔时间的控制。通过调整电流和时间参数,可以既保证亮度,又保证显示。

- 增加自动校时模块,每隔一段时间对累加计数器进行校时,减少累加计数器误差的积累。

8.3数字钟开发过程中遇到的问题及解决的办法

刚开始做数字钟这个实验时,我认为这个实验做起来会很轻松,脑子中一下子出现了许多设计念头,刚开始的时候我认为的数字钟无非就是三个计数器分层累加实现计数,当听完安老师讲解之后,我发现数字钟需要设计复位,预置,使能的功能,在顶层如何将三级计数器连接嵌套问题 ,数码管如何显示问题都没有细细考虑到。

对于数字钟的复位,预置,使能的功能,通过对EDA这门课程的学习,根据参考书上的计数器例题,学习掌握了计数器的复位,预置,使能各种功能的嵌套,并通过if语句将各功能分层嵌套起来,最终实现了计数器各功能的实现和运用。

对于三级计数器如何在顶层连接问题,通过请教老师,一共有两种方式可以实现顶层的连接,第一种就是每一级的进位给到下一级的CLK上,通过每一级的进位,就会使下一级的CLK产生一个矩形脉冲,下一级通过产生的矩形脉冲进行计数,当每产生一个进位,下一级就会计数一次,以此循环,完成三级累加计数器。第二种是通过每一级的进位给到下一级的使能,通过将三级的CLK端口并联,构造分频器原理,就会使下一级的使能为1,计数一次,当每产生一个进位,下一级的使能为1,计数一次,以此循环,完成三级累加计数器。

对于数码管如何显示问题,通过译码器可以有两种实现方式,分别为静态显示和动态显示。静态显示主要的优点是显示稳定,在发光二极管导通电流一定的情况下显示器的亮度大,系统运行过程中,在需要更新显示内容时,CPU才去执行显示更新子程序,这样既节约了CPU的时间,又提高了CPU的工作效率。动态显示优点就是一位一位地轮流点亮各位显示器,对于每一位显示器来说,每隔一段时间点亮一次。显示器的亮度既与导通电流有关,也与点亮时间和间隔时间的比例有关。调整电流和时间参数,可以实现亮度较高、较稳定地显示、如果显示器的位数不大于8位,则控制显示器公共极点位只需一个8位口,控制各位显示器所显示的字形也需一个8位口。通过比较,我选择的是静态显示译码方式。

通过本次实验,我不仅学到了关于EDA的许多专业知识,同时也让我感觉到了思考的重要性。

不管是现在还是未来,我们不要遇到一点困难就退缩,就去向老师同学寻求帮助,自己是自己最好的老师,只有我们靠自己的不断修改出正确结果,才会对这个只是掌握的更加透彻,我们不要惧怕犯错,只有不断的犯错,从错误中发现问题,改正错误,才能取得进步通过思考、发问、自己解惑并动手、改进的过程,才能真正的完成课题。

- 参考文献

EDA技术与应用(第2版) 清华大学出版社

V H D L实用教程 电子科技大学出版社

最后

以上就是犹豫水蜜桃最近收集整理的关于基于FPGA的数字钟设计实验报告的全部内容,更多相关基于FPGA内容请搜索靠谱客的其他文章。

发表评论 取消回复