数字电子技术基础1——数字逻辑概论

1.1 数字信号与数字电路

衡量电路的两个主要参数:

-

集成度: 每一芯片所包含门的个数

分类 门的个数 典型集成电路 小规模 最多12个 逻辑门、触发器 中规模 12~99 计数器、加法器 大规模 100~9999 小型存储器、门阵列 超大规模 10000~99999 大型存储器、微处理器 甚大规模 106以上 可编程逻辑器件、多功能专用集成电路 -

特征尺寸: 指集成电路中半导体器件加工的最小线条宽度

数字集成电路特点

- 稳定性高,抗干扰能力强

- 易于设计

- 便于集成,成本低廉

- 可编程性

- 高速度,低功耗

- 便于存储、传输和处理

数字电路的分析、设计和测试

-

分析方法

(1) 逻辑代数:真值表、功能表、逻辑表达式或波形图

(2) EDA工具

-

设计方法

(1) 传统设计方式

(2) 基于EDA软件设计

EDA包括: ·原理图输入 ·HDL文本输入 ·测试平台 ·仿真和综合工具

-

测试技术

(1) 数字电压表

(2) 数字示波器

数字信号的描述方法

-

二值数字逻辑和逻辑电平

-

逻辑0:低电平

-

逻辑1:高电平

-

逻辑0和逻辑1:只有两种对立逻辑状态的逻辑关系称为二值数字逻辑或简称数字逻辑

-

-

数字波形

-

定义: 逻辑电平对时间的图形标识

-

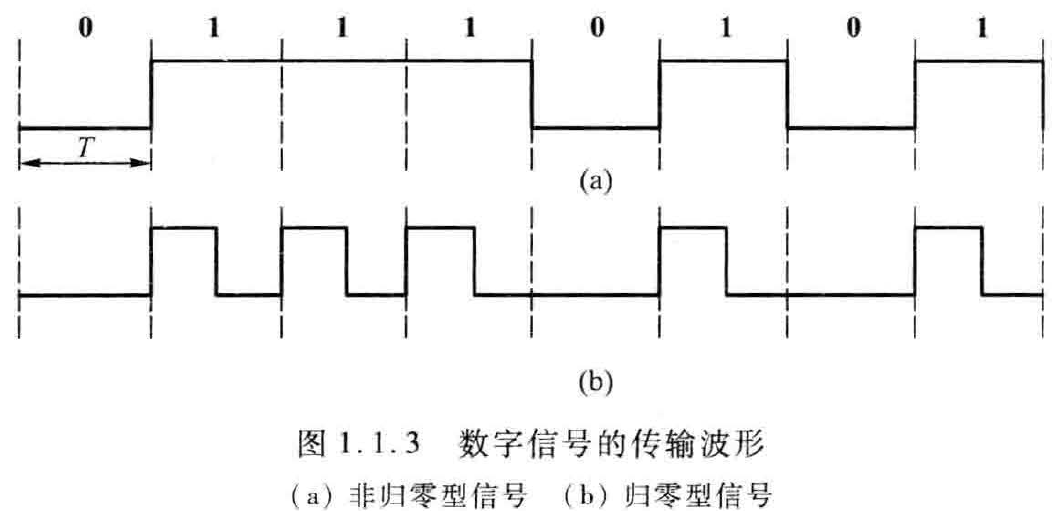

分类:

(1)非归零型:一个时间拍内高电平代表1,低电平代表0

(2)归零型:有脉冲代表1,无脉冲代表0

-

数据率、比特率: 秒钟传输数据的位数

-

占空比 q q q : 表示脉冲宽度t, 占整个周期T 的百分数,常用下式来表示

q ( % ) = t w T × 100 % q(%)={frac{t_w}T}×100% q(%)=Ttw×100%当占空比为50 % 时,称此时的矩形脉冲为方波,即0 和1 交替出现并持续占有相同的时间。

-

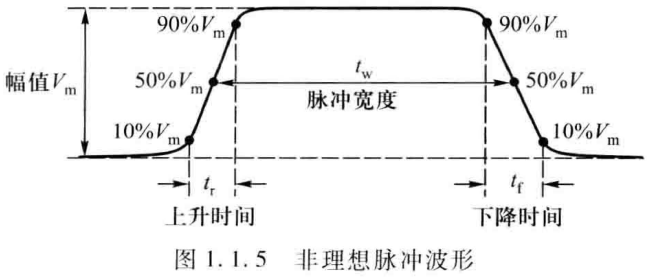

上升时间 t r t_r tr : 若脉冲幅值为 V m V_m Vm 将矩形脉冲从 10 % V m 10% V_m 10%Vm 到 90 % V m 90% V_m 90%Vm 时所经历的时间称为上升时间

-

下降时间 t f t_f tf : 下降时间则相反

-

脉冲宽度 t w t_w tw : 将脉冲上升沿的 50 % V m 50% V_m 50%Vm 到下降沿的 50 % V m 50% V_m 50%Vm 两个时间点所跨越的时间称为脉冲宽度

不同类型的器件和电路,其上升和下降时间各不相同。一般数字信号上升和下降时间的典型值约为几纳秒(ns) 。

-

波形图(Waveform): 将数字电路输入变量的每一种取值与相应的输出值按照时间顺序依次排列得到的图形

-

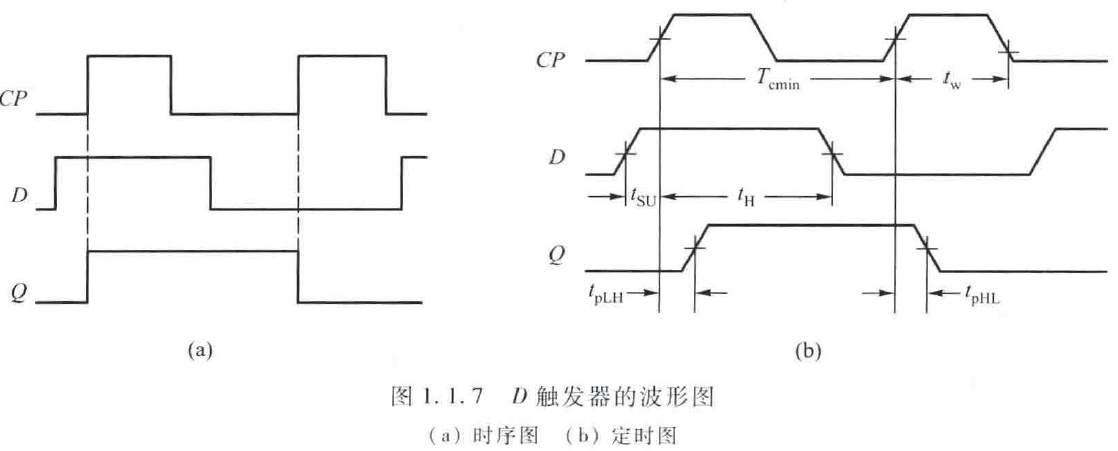

时序图与定时图(Timing Diagram): 在时序电路中,电路的状态和输出对时钟脉冲序列和输入信号响应的波形图

时序图: 时序图用来表示多个输入信号的先后顺序, 以及输出如何对输入信号产生响应的过程。通常时序图侧重描述电路逻辑功能

定时图: 侧重各个信号的先后顺序以及时间量。为便于比较

-

1.2 数制

-

定义: 多种数码的构成方式以及从低位到高位的进位规则称为数制

-

任意进制数表达式:

( N ) R = ∑ i = − ∞ ∞ K i × R i (N)_R=sumlimits_{i = -infty}^{infty}K_i×R^i (N)R=i=−∞∑∞Ki×Ri

式中 K i K_i Ki 是第 i i i 次幂的系数,根据基数 R R R 的不同,它的取值为 0 0 0 到 R − 1 R-1 R−1 个不同的数码。

1.2.2 二进制

- 表示方法: 0和1两个数码,计数规律为 “逢二进一”

- 优点:

- 二进制的数字电路简单可靠,所用元件少

- 二进制的基本运算规则简单,运算操作方便

- 缺点: 用二进制表示一个数时,位数太多

- 波形表示: 在数字电路中, 二值数据常用数字波形来表示

- 数据的传输: 采用串行的方式或并行的方式

1.2.3 十~二进制之间的转换

-

二进制数转换为十进制数: 将每位二进制数与其权相乘, 然后相加便得到相应的十进制数

-

十进制数转换为二进制数:

-

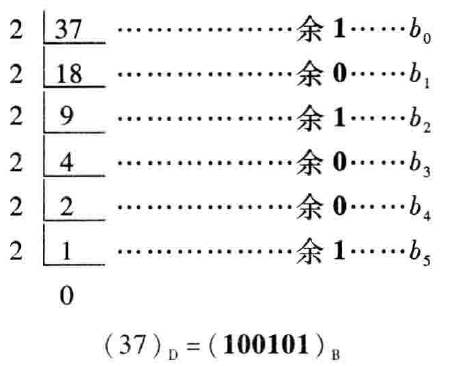

整数部分:

将十进制整数每除以一次2,就可根据余数得到二进制数的1 位数字。因此,只要连续除以2 直到商为0 , 就可由所有的余数求出二进制数。

当十进制数较大时,不必逐次除2 , 而是将十进制数和与其相当的2 的幕项对比,使转换过程得到简化。

-

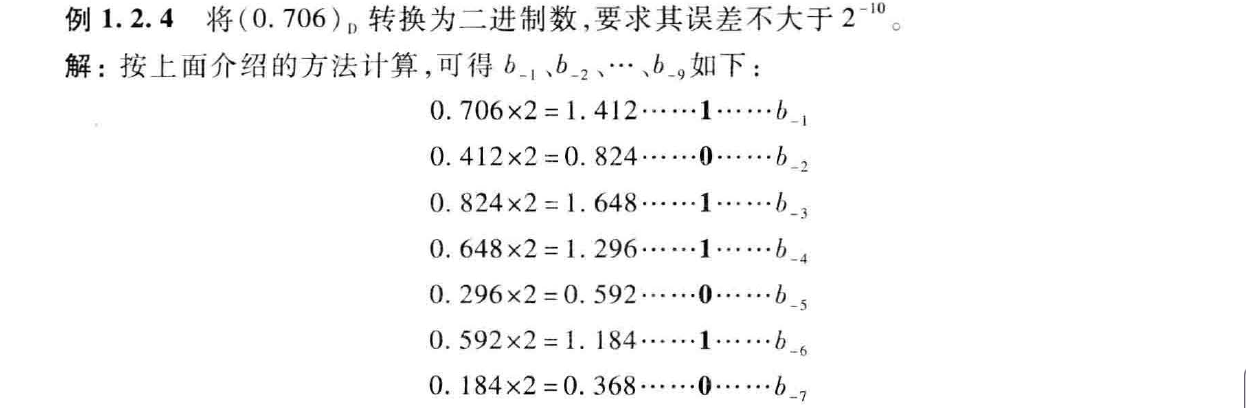

小数部分:

将十进制小数每次去掉上次所得积中的整数再乘以2, 直到满足误差要求进行“四舍五入“为止,就可完成将十进制小数转换成二进制小数。

-

1.2.4 十六进制和八进制

-

十六进制:

十六进制数采用16 个数码,分别为0, 1, 2, 3, 4, 5 , 6, 7, 8, 9, A, B, C, D, E, F 。其中 A、B 、C 、D 、E 、F 依次相当于十进制数中的10 、11 、12 、13 、14 、15 。十六进制数是"逢十六进一”,

-

十六~二进制之间的转换

4 位二进制数有16 个状态,而1 位十六进制数有16 个不同的数码, 因此二进制转换成为十六进制非常简单,以小数点为基准,整数部分从右到左每4 位一组,不足4 位的在高位补0 ; 小数部分从左到右每4 位一组,不足4 位的在低位补0 。每4 位一组的二进制数就表示1 位十六进制数。

-

八进制

同样,八进制数由0~7 共 8 个数码表示,且“逢八进一" 。

-

八~二进制之间的转换

同理,对于八进制数, 可将3 位二进制数分为一组,对应于1 位八进制数。

至于十进制数变换为十六进制数,可先将十进制数变换为二进制数,再由二进制数转换为十六进制数。

-

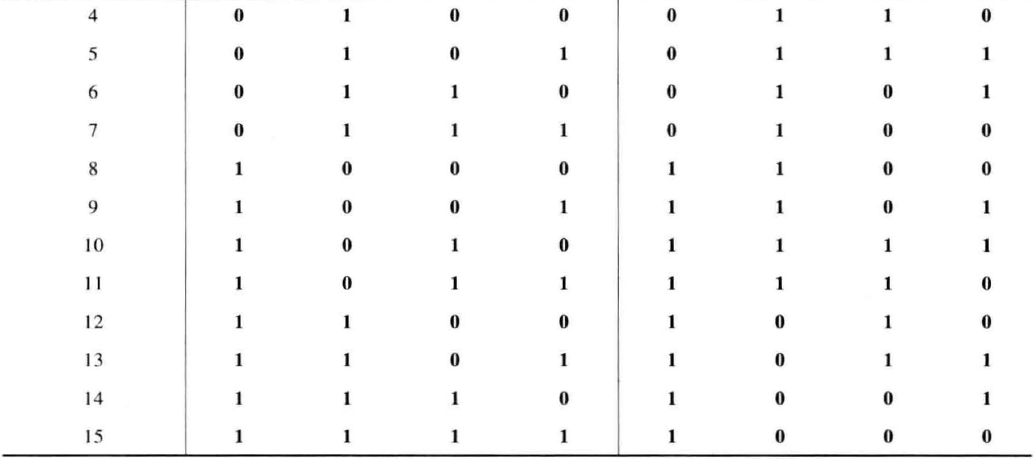

总对照表:

1.3 二进制数的算术运算

1.3.1 无符号二进制数的算术运算

-

加法:

0 + 0 = 0 , 0 + 1 = 1 , 1 + 1 = 1 0 0+0=0 , 0+1=1 , 1+1= fbox{1}0 0+0=0,0+1=1,1+1=10

方框中的1 是进位位,表示两个1 相加“逢二进一” 。 -

减法:

0 − 0 = 0 , 1 − 1 = 0 , 1 − 0 = 1 , 0 − 1 = 1 1 0-0=0 ,1-1 =0,1-0=1 ,0-1 = fbox{1}1 0−0=0,1−1=0,1−0=1,0−1=11

方框中的 1 是借位位, 表示 0 减 1 时不够减,向高位借1。 -

乘法运算和除法运算:

-

无符号二进制数的乘法规则是:

0 × 0 = 0 , 0 × 1 = 0 , 1 × 0 = 0 , 1 × 1 = 1 0×0=0 ,0×1=0,1×0=0 , 1×1=1 0×0=0,0×1=0,1×0=0,1×1=1 -

无符号二进制数的除法规则是:

0 ÷ 1 = 0 , 1 ÷ 1 = 1 0÷1=0,1÷1=1 0÷1=0,1÷1=1

注意,除数不能为0, 否则无意义

-

1.3.2 带符号二进制数的减法运算

当涉及负数时,就要用有符号的二进制数表示。在定点运算的情况下, 二进制数的最高位(即最左边的位)表示符号位,且用 0 表示正数,用 1 表示负数。其余部分为数值位。

(

+

11

)

D

=

(

0

1011

)

B

(

−

11

)

D

=

(

1

1011

)

B

(+11)_D=(fbox{0}1011)_B\ \ (-11)_D=(fbox{1}1011)_B

(+11)D=(01011)B(−11)D=(11011)B

-

原码: 是最简单的机器数表示法。用最高位表示符号位,‘1’表示负号,‘0’表示正号。其他位存放该数的二进制的绝对值。

原码最大的问题就在于一个数加上他的相反数不等于零。

例如:0001+1001=1010 (1+(-1)=-2)0010+1010=1100 (2+(-2)=-4) -

反码: 正数的反码还是等于原码,负数的反码就是他的原码除符号位外,按位取反。

则:

0001+1110=1111 (1+(-1)= - 0)互为相反数相加等于0,解决。虽然是得到的结果是1111也就是 -0但是:

1110(-1)+1100(-3)=1010(-5)相反数问题是解决了,但是却让两个负数相加的出错了。

但是实际上,两个负数相加出错其实问题不大。我们回头想想我们的目的是什么?是解决做减法的问题,把减法当成加法来算。

-

补码: 正数的补码等于他的原码负数的补码等于反码+1。(这只是一种算补码的方式,只不过是补码正好就等于反码加1罢了。)

详细解释参考这个网站: https://blog.csdn.net/afsvsv/article/details/94553228

-

二进制数的补码表示:

在数字电路或系统中,为简化电路,常将负数用补码表示,以便将减法运算变为加法运算。

若基数为 R R R , 位数为 n n n 的原码 N N N , 其补码为

N 补 = R n − N N_补=R^n-N N补=Rn−N

当考虑负数情况时,带符号二进制数补码的计算方法如下:- 补码或反码的最高位为符号位,正数为0 , 负数为1 。

- 当二进制数为正数时,其补码、反码与原码相同。

- 当二进制数为负数时,将原码的数值位逐位求反( 即得到反码),然后在最低位加1得到补码。

-

二进制补码的减法运算

采用补码的形式,可以很方便地进行带符号二进制数的减法运箕。减法运算的原理是减去一个正数相当于加上一个负数,即 A − B = A + ( − B ) A-B=A+(-B) A−B=A+(−B), 对 ( − B ) (-B) (−B) 求补码,然后进行加法运算。至于乘法和除法运算,可以采用移位与加法或减法的组合完成。

进行二进制补码的加法运算时,必须注意被加数补码与加数补码的位数相等,即让两个二进制数补码的符号位对齐。通常两个二进制数的补码采用相同的位数表示。

-

溢出

-

溢出的判别

两个符号相反的数相加不会产生溢出,但两个符号相同的数相加有可能产生溢出。

1.4 二进制代码

编码: 以一定的规则编制代码,用以表示十进制数值、字母、符号等的过程

译码: 以一定的规则编制代码,用以表示十进制数值、字母、符号等的过程

若所需编码的信息有N 项, 则需要的二进制数码的位数n 应满足如下关系

2

n

≥

N

2^n≥N

2n≥N

1.4.1 二~十进制码

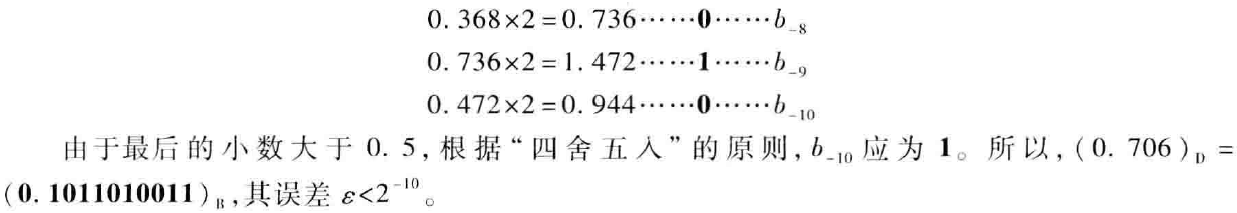

二~十进制码就是用 4 位二进制数来表示 1 位十进制数中的 0 ~ 9 十个数码,即二进制编码的十进制码(Binary - Coded-Decimal , BCD码)。4 位二进制数有 16 种不同的组合方式, 即 16 种代码,根据不同的规则从中选择10 种来表示十进制的 10 个数码。其方案有很多种。下面列出几种常用的BCD 码。

有权码和无权码区别是每一位是否有权值。

-

8421码

如典型的8421码为有权码,其编码中每位的值都是固定数,称为位权“8421”表示从高到低各位二进制位对应的权值分别为8、4、2、1,将各二进制位与权值相乘,并将乘积相加就得相应的十进制数。例如,8421BCD码“0111”,0×8+1×4+1×2+1×1=7D,其中D表示十进制(Decimal)数。

-

2421 码

也是有权码。对应b3、b2、b1和b0 的权分别是2、4、2和 1 。它的特点是,将任意一个十进制数N 的代码各位取反,所得代码正好表示N 的9 的补码。例如2 的代码0010 各位取反所得代码I 101 正好是9 -2 = 7 的代码。这种特性称为自补性。具有自补特性的代码称为自补码 。

有权码十~二进制转换公式(W为各位的权):

( N ) D = W 3 b 3 + W 2 b 2 + W 1 B 1 + W 0 b 0 (N)_D=W_3b_3+W_2b_2+W_1B_1+W_0b_0 (N)D=W3b3+W2b2+W1B1+W0b0

-

余 3 码

是自补码,与 2421 码有类似的自补性。当两个十进制数之和是 10 时, 相应的二进制数之和是16 。例如 1 和 9、2和8 、……、6 和4 。该特点便于求 10 的补码,其编码可以由8421 码加3( 0011) 得出。

-

余 3 循环码

也是一种无权码,它的特点是具有相邻性,任意两个相邻代码之间仅有1 位取值不同,余 3 循环码可以看成是将格雷码首尾各3种状态去掉后得到的。

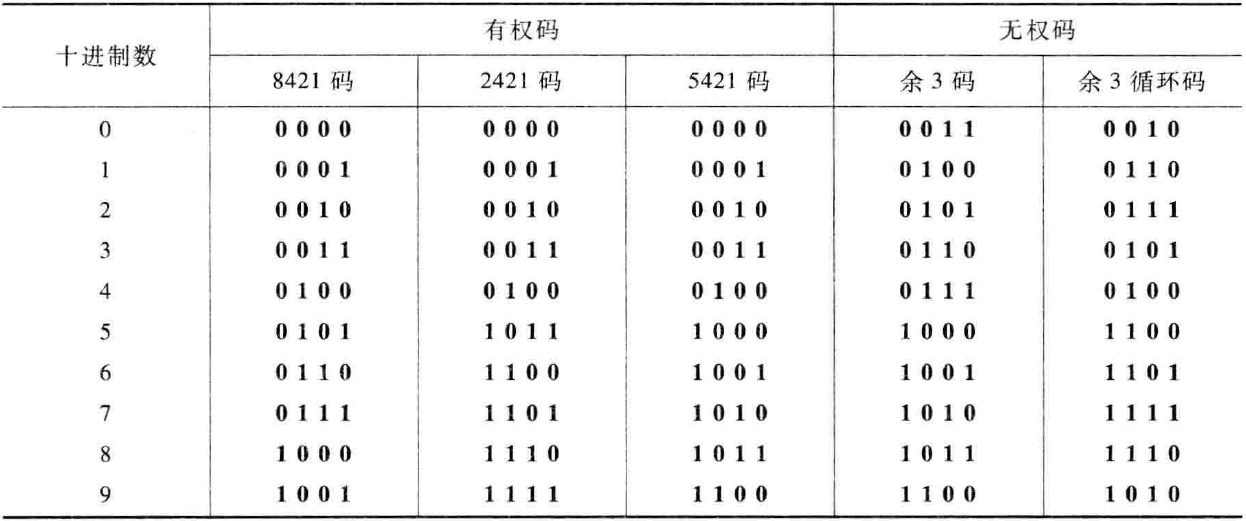

1.4.2 格雷码(Gray code)

是一种常见的无权码,也具有相邻性,即两个相邻代码之间仅有1 位取值不同,并且0 和最大数(22 - 1 ) 之间也只有1 位不同,因此它是一种循环码,这个特点使它在代码形成和传输时引起的误差较小。因而常用于将模拟量转换成用连续二进制数序列表示数字量的系统中。可以避免错误数码的出现。

缺点: 格雷码的缺点是不能直接进行算术运算。这是因为格雷码是无权码,其每一位的权值不是固定的。

-

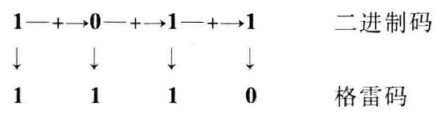

二进制码到格雷码的转换

(1)格雷码的最高位(最左边)与二进制码的最高位相同。

(2)从左到右,逐一将二进制码相邻的2 位相加(舍去进位),作为格雷码的下一位。

-

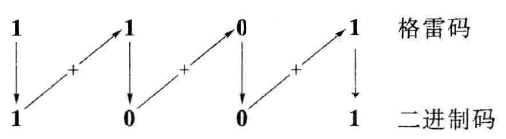

格雷码到二进制码的转换

(1) 二进制码的最高位(最左边) 与格雷码的最高位相同。

(2) 将产生的每一位二进制码, 与下一位相邻的格雷码相加(舍去进位),作为二进制码的下一位。

1.4.3 ASCII 码

https://asciichart.com/ascii_hexadecimal.html

1.5 二值逻辑变量与基本逻辑运算

-

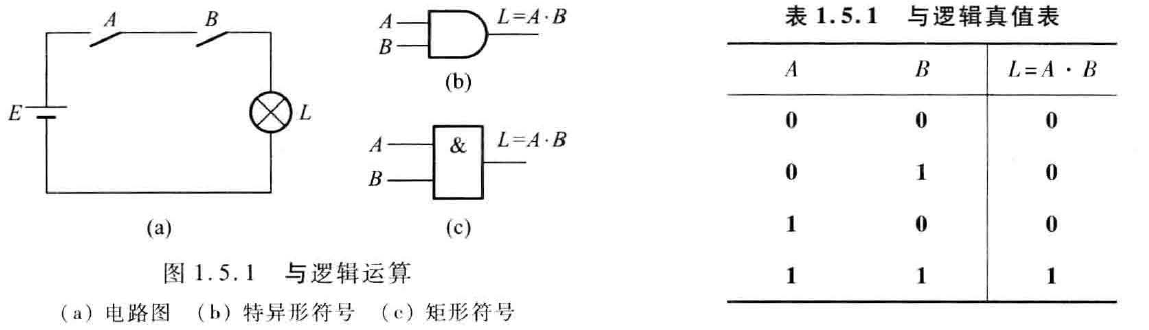

与运算

L = A ⋅ B L=A·B L=A⋅B

-

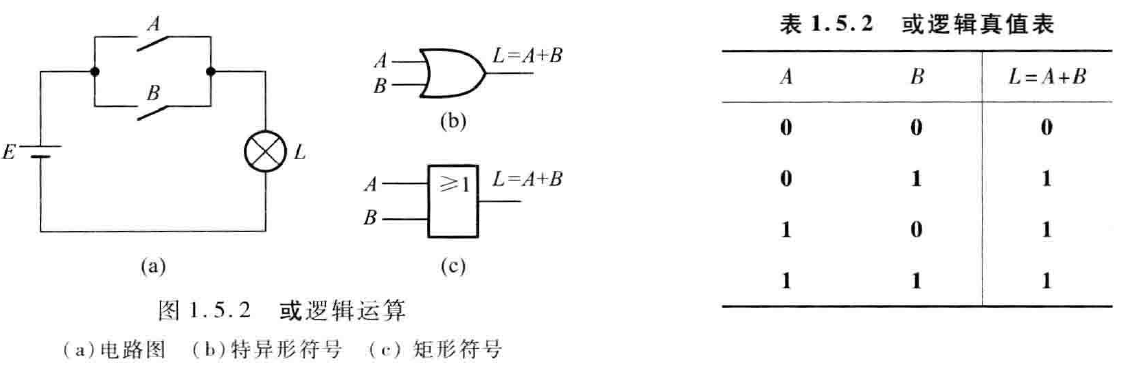

或运算

L = A + B L=A+B L=A+B

-

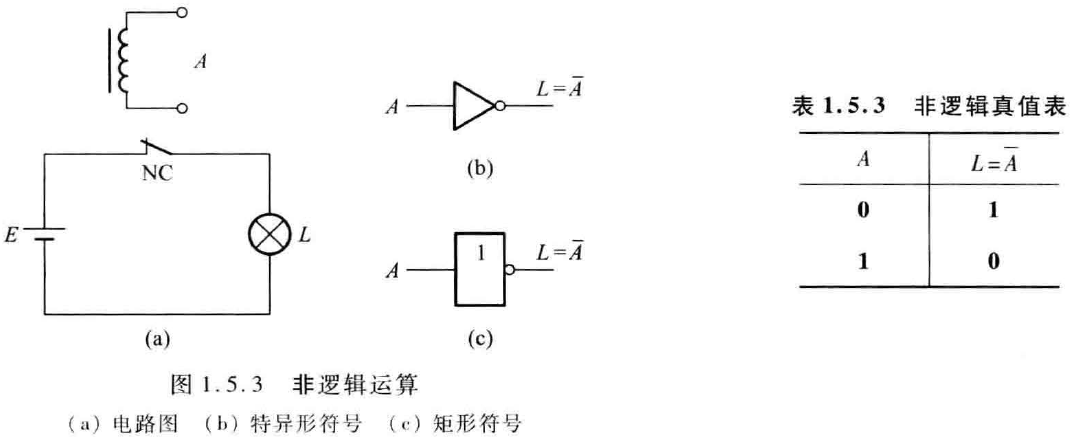

非运算

L = A ‾ L=overline A L=A

-

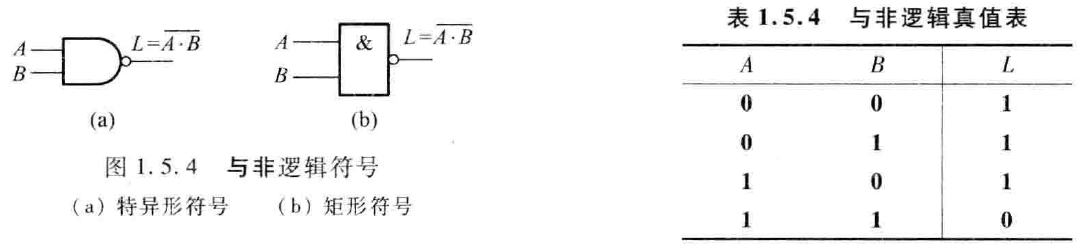

与非

L = A ⋅ B ‾ L=overline{A·B} L=A⋅B

-

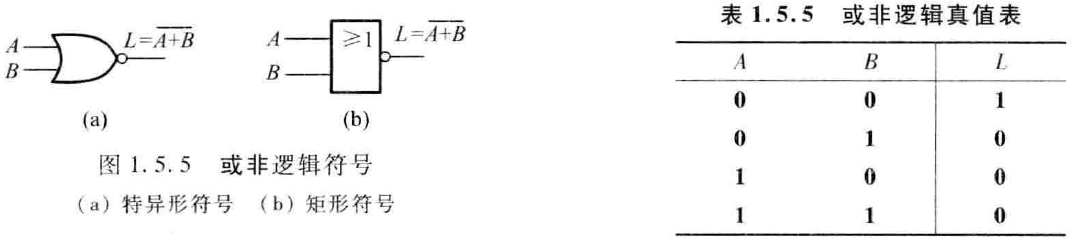

或非

L = A + B ‾ L=overline{A+B} L=A+B

-

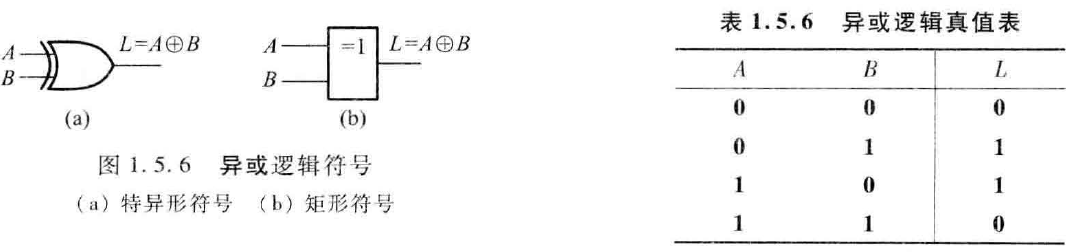

异或

当两个输入状态相同时, 输出为O ; 当两个输入状态不同时,输出为1 。

L = A ‾ B + A B ‾ = A ⊕ B L=overline AB+Aoverline B=Aoplus B L=AB+AB=A⊕B

-

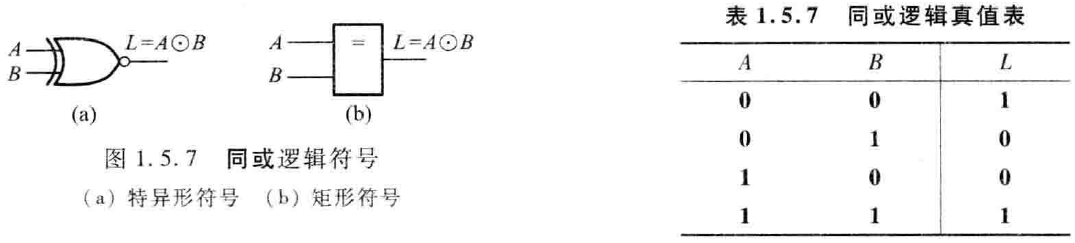

同或 (同或和异或的逻辑关系刚好相反)

当两个输入状态相同时,输出为1,当两个输入状态不同时,输出为0

L = A B + A ‾ B ‾ = A ⊙ B L=AB+overline A overline B=Aodot B L=AB+AB=A⊙B

1. 6 逻辑函数及其表示方法

1.6.1 逻辑函数的几种表示方法

- 真值表: 将输入变量所有可能的取值与相应的函数值列成表格,就得到真值表。

- **逻辑函数表达式: ** 逻辑表达式是用与、或、非等运货组合起来,表示逆辑函妏与逻辑变从之间关系的逻辑代

数式。 - 逻辑图: 用与或、非等逻辑符号表示逻辑函数中各变釐之间的逻辑关系所得到的图形称为逻辑图。

- 波形图: 对输入变量随时间变化的每一种取值`求出相应的输出值。并将输入和输出关系按时间顺序依次排列得到的图形,称为波形图。

1.6.2 逻辑函数表示方法之间的转换

- 真值表到逻辑图的转换

- 逻辑图到真值表的转换

最后

以上就是合适小蝴蝶最近收集整理的关于数字电子技术基础1——数字逻辑概论数字电子技术基础1——数字逻辑概论的全部内容,更多相关数字电子技术基础1——数字逻辑概论数字电子技术基础1——数字逻辑概论内容请搜索靠谱客的其他文章。

发表评论 取消回复