《可编程数字逻辑电路设计》课程中Quartus II软件的使用说明

VHDL和Verilog HDL不一样。

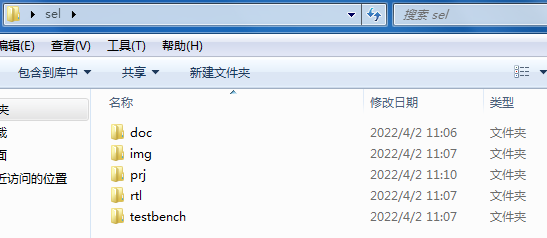

1.新建文件夹,里面包含5个子文件夹(doc/img/prj/rtl/testbench)

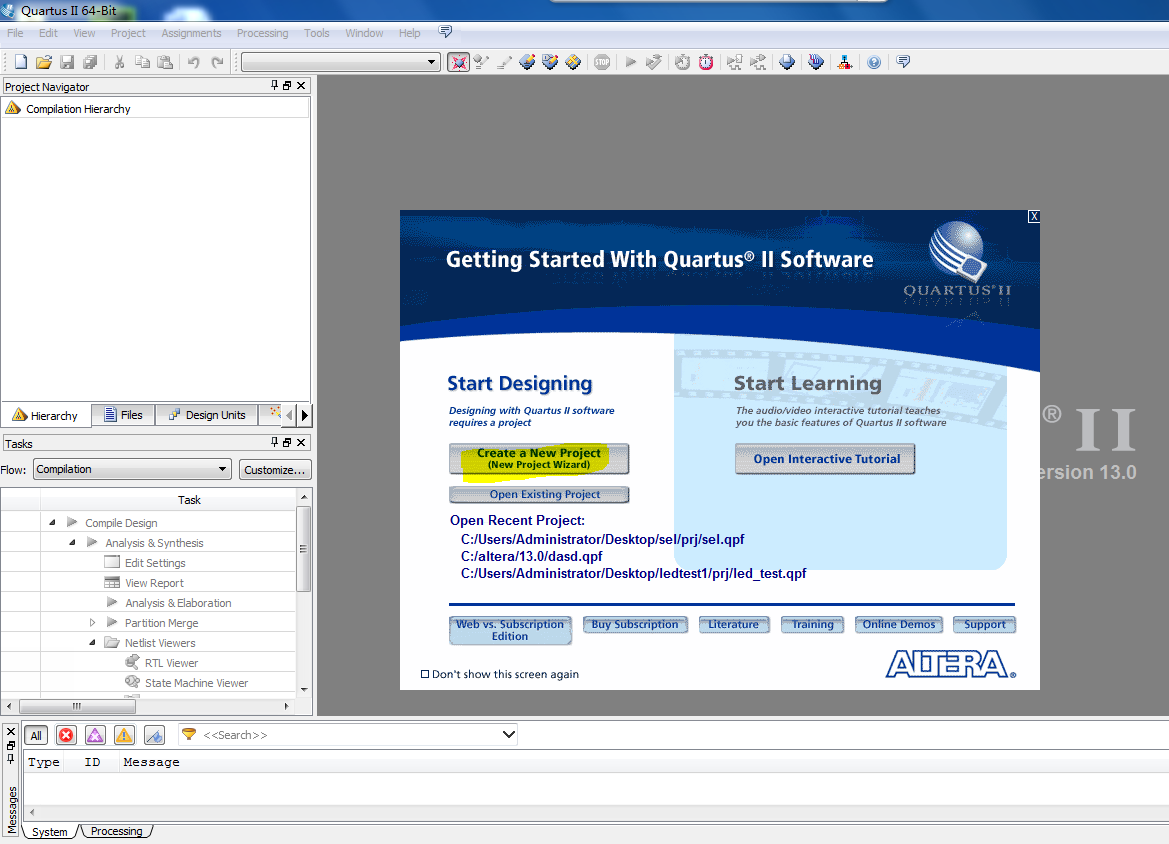

2.打开Quartus II软件 ,创建新工程。

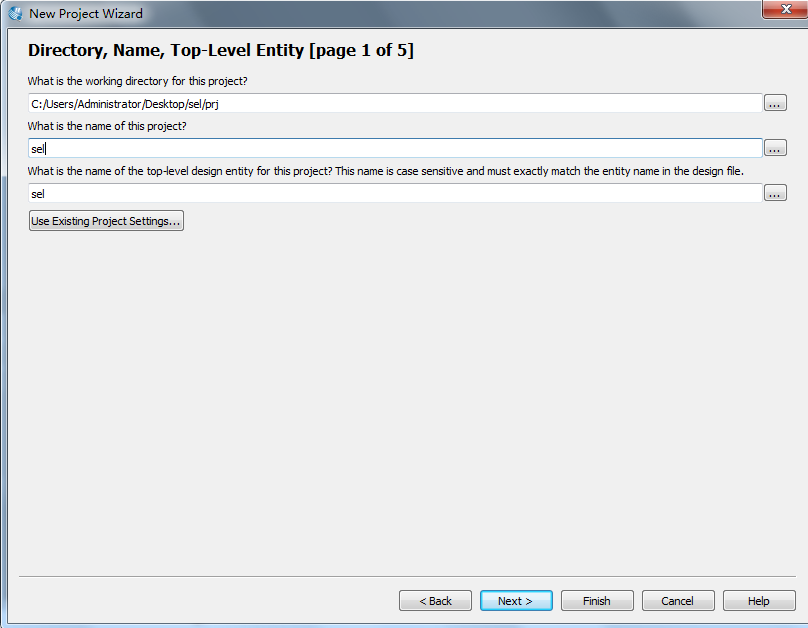

3. 选择工程目录为步骤1新建的文件夹的路径;为这个工程起个名字(sel)。

3. 选择工程目录为步骤1新建的文件夹的路径;为这个工程起个名字(sel)。

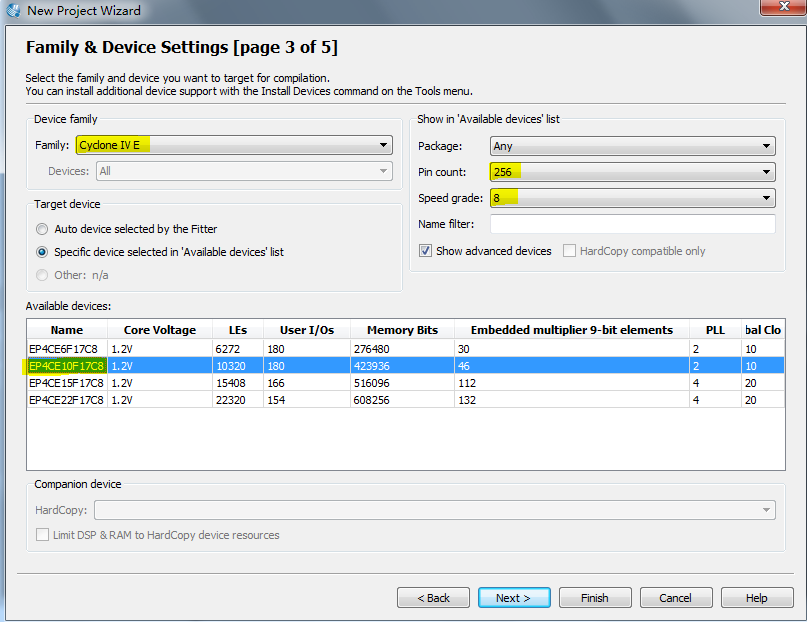

4.设置为Cyclone IV E,引脚数256,速度8,选择设备为EP4CE10F...

4.设置为Cyclone IV E,引脚数256,速度8,选择设备为EP4CE10F...

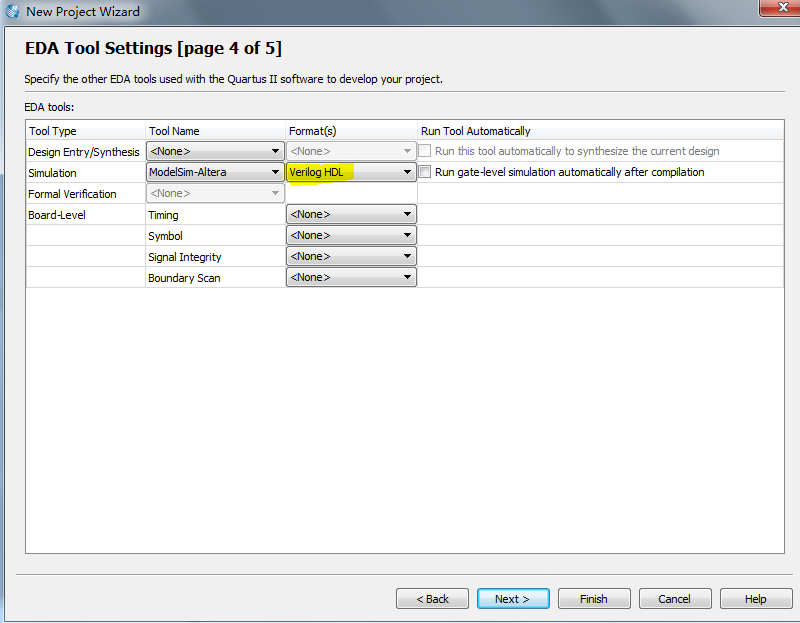

5.仿真环境:Verilog HDL

5.仿真环境:Verilog HDL

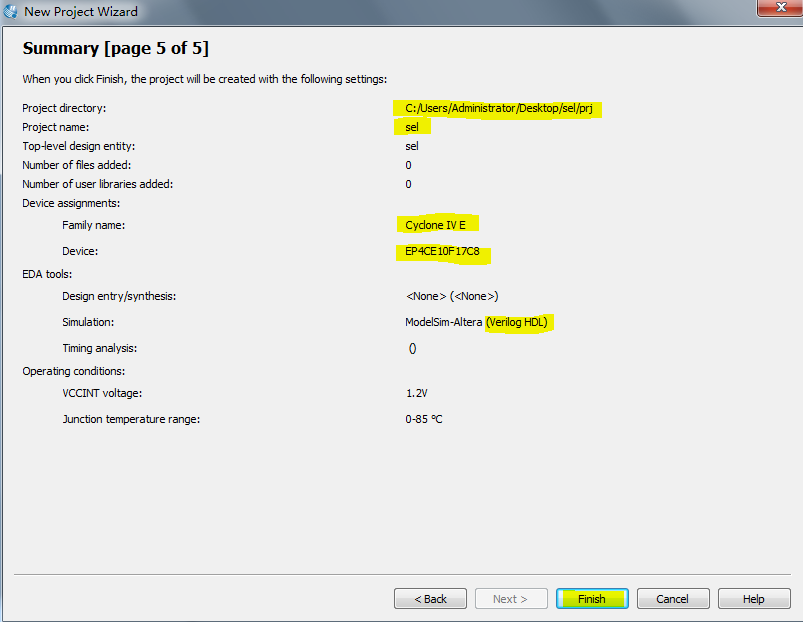

6.完成。Finish!

6.完成。Finish!

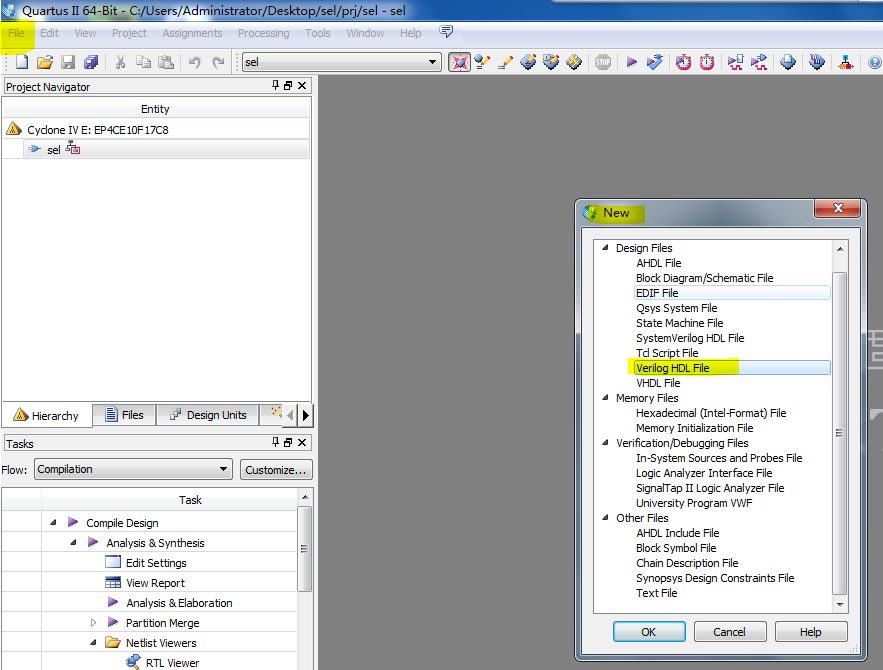

7.文件-新建-Verilog HDL 文件。

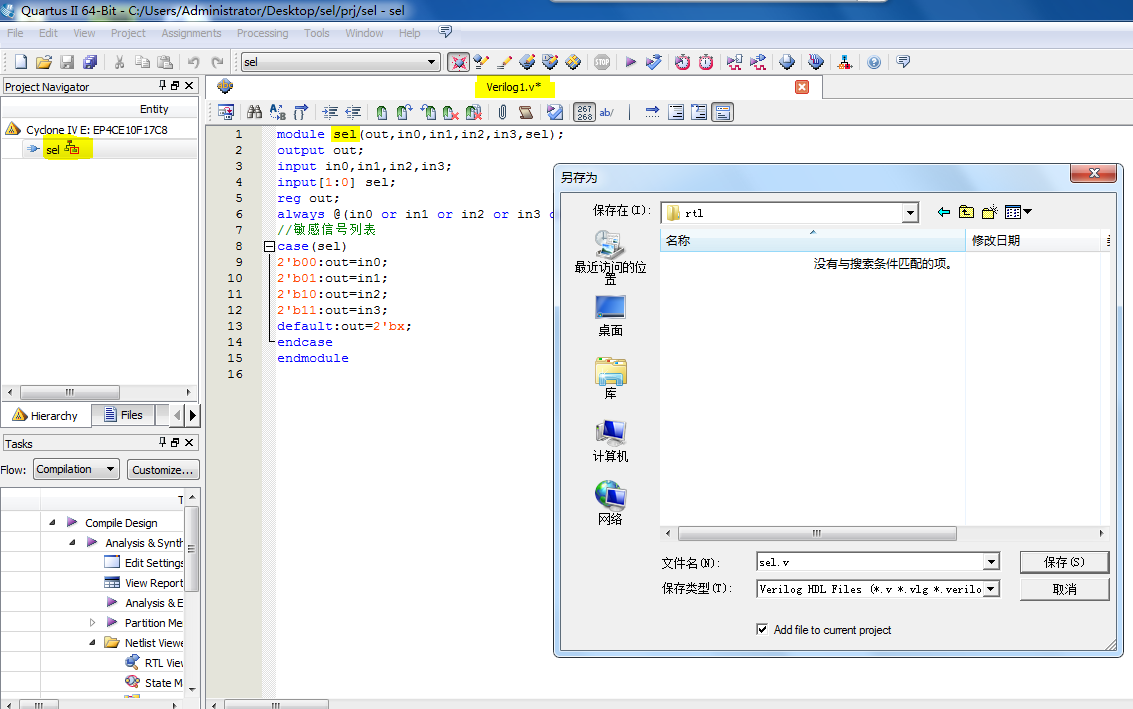

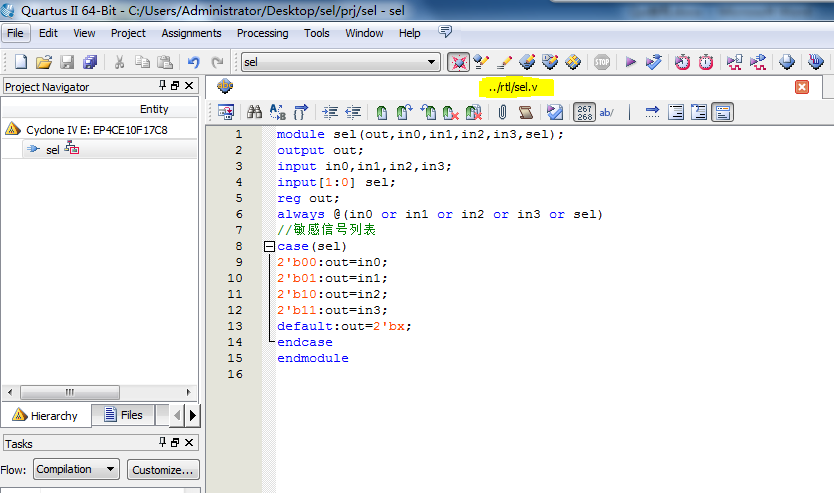

8.编写代码:二选一数据选择器

8.编写代码:二选一数据选择器

module sel(out,in0,in1,in2,in3,sel);

output out;

input in0,in1,in2,in3;

input[1:0] sel;

reg out;

always@(in0 or in1 or in2 or in3 or sel);

//敏感信号列表

case(sel)

2'b00:out=in0;

2'b01:out=in1;

2'b10:out=in2;

2'b11:out=in3;

default:out=2'bx;

endcase

endmodule

Verilog

1.模块语句及表达式(module)

2.端口语句、端口信号名、端口模式

3.逻辑操作符,等式操作符

4.连续赋值语句(assign)

延时6个时间单元,再把A&B的结果赋值给R1

5.关键字(input/output)

6.标识符

7.注释符号(//)

8.规范的程序书写格式(Tab空格)

9.文件取名和存盘(*.v)

(文件名与模块名字一致)

(1)reg寄存器变量

(2)always过程语句,还有initial也是过程语句

always(敏感信号)

(3)begin...end块语句,相当于花括号 { }

(4)case条件语句,一半放在always语句中使用。

(5)Verilog的4种状态:0,1,z,x

(6)并位操作运算符: { }

(7)Verilog的数字表达形式:<位宽><进制><数字>

b表示二进制;o表示八进制数;d表示十进制数;h表示十六进制数;9.工程名和模块名得一致。

保存在rtl文件夹中,就可得到新的文件名(sel.v):

保存后,未保存的文件名Verilog1.v变为sel.v的文件名。

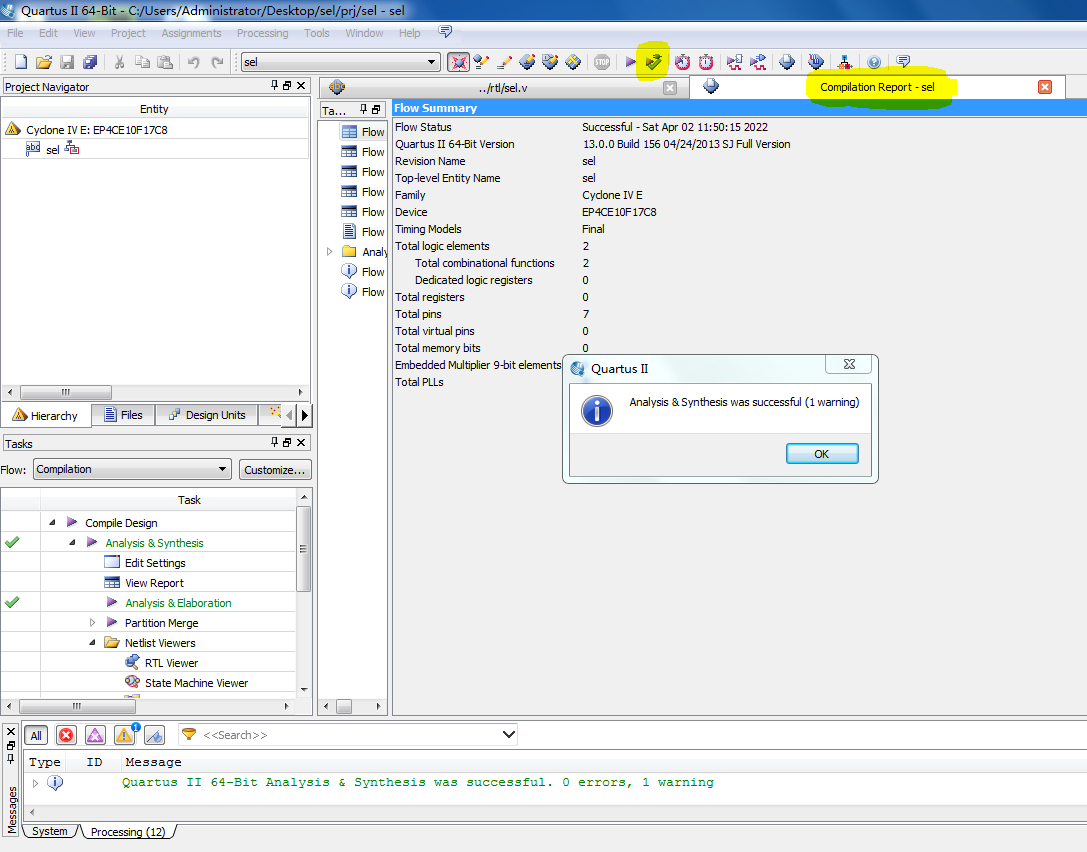

10.编译

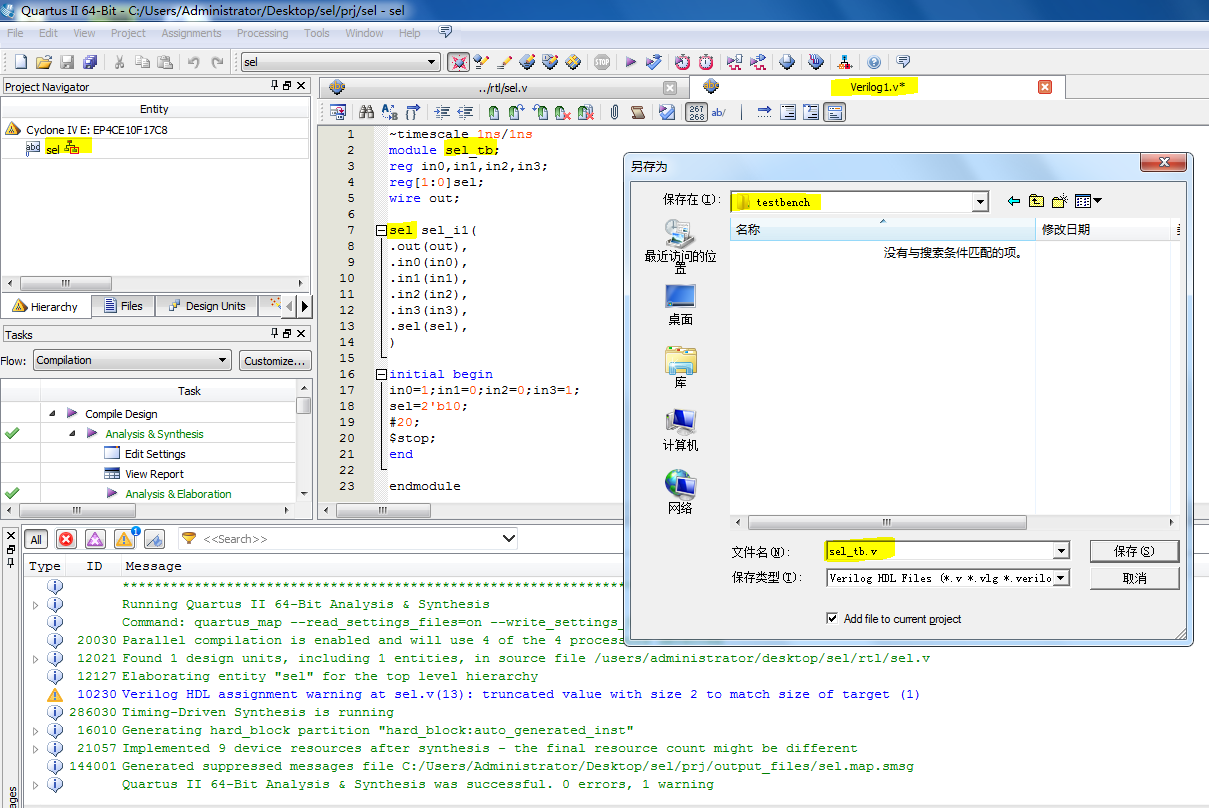

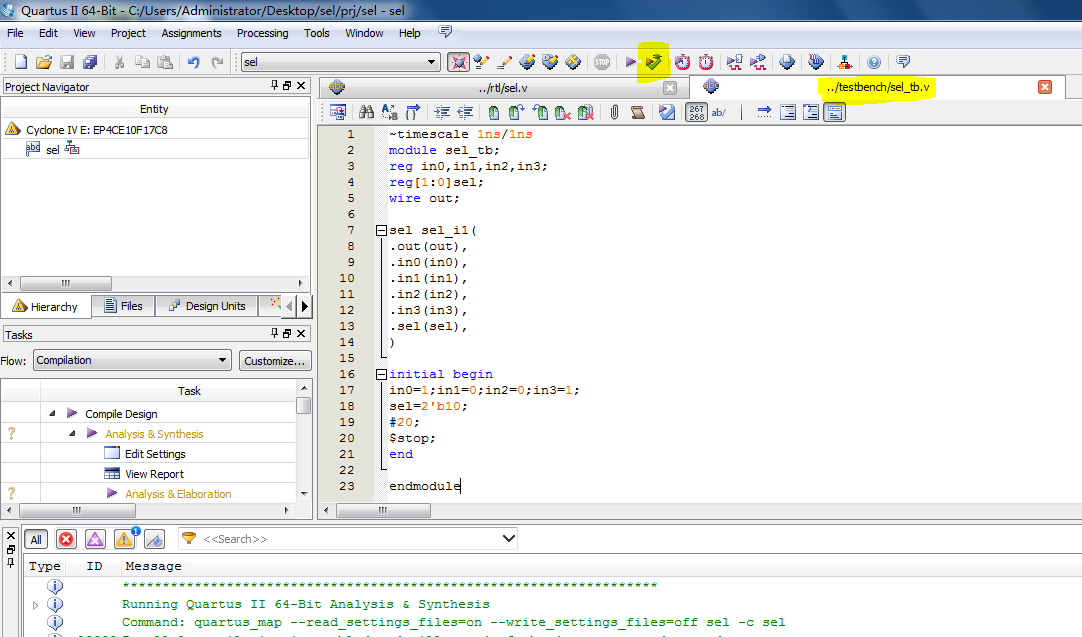

11.编写测试代码:保存时为之命名(sel_tb.v),并保存在testbench文件夹中,

11.编写测试代码:保存时为之命名(sel_tb.v),并保存在testbench文件夹中,

12.编译测试代码

13.建立代码和测试代码之间的链接

Assignments--Setting

待补充……

最后

以上就是时尚时光最近收集整理的关于Quartus II使用说明(Verilog HDL二选一数据选择器 )的全部内容,更多相关Quartus内容请搜索靠谱客的其他文章。

发表评论 取消回复