content:

- shift register

- attribute

- counter and timer

- VHDL type and operator

1. shift register: copy one bit to the bit with sequential index. one thing that we should take into consideration is that the value of signals in the process will change at the point of process' end. which can be different to variables.

the standard 4-bit shift register is as shown below:

...

process(clk)

begin

if (clk='1' and clk'event) then

if (rst='1') then

q<="0000";

elsif (shr='1') then

r(3)<=shr_in;

r(2)<= r(3);

r(1)<= r(2);

r(0)<= r(1);

end if;

end if;

end process;

...if the project requires for more bits output, we can use a 'for' statement to meet this requirement.

...

process(clk)

begin

if(clk='1' and clk'event) then

if(rst='1') then

r<=(others=>'0')

elsif (shr='1') then

r(31)<=shr_in;

for index in 0 to 30 loop

r(index)<=r(index+1);

end loop;

end if;

end if;

end process;

... some times we need to read data from '.txt' file in the testbench.

1> tell the compiler which kind of file do we need to read

...

file 在工程中的文件名: 文件类型

...

e.g

...

file vectorfile: txt

...2> open the file in the process

file_open(vectorfile, "vector.txt", read_mode);3> implementing elements in the file(for example it can be used to control the while loop)

while not endfile(vectorfile) loop;

readline(vectorfile,inputline);--读取每一行放到inputline中

for i in inputline'range loop

read(inputline, inputbit);--读取每一行中的每一个元素放到inputbit中

...

end loop

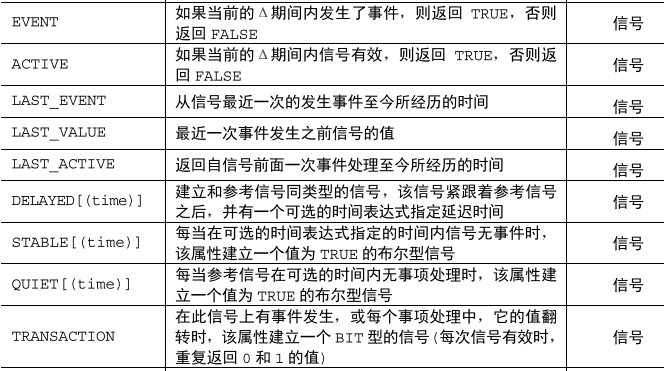

end loop;2. attributes

these items can have attributes:

-value

-function

-signal:

-type

-interval

for signal:

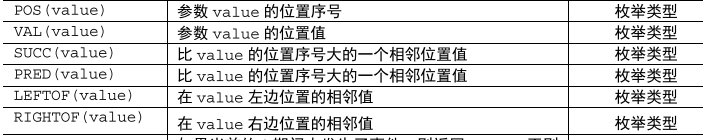

for enumerate type:

implementation example:

type state_type is (init,hold,strobe,read,idle);

VARIABLE P: integer:= state_type’POS(Read);--variable P should be '3'

VARIABLE V: state_type:= state_type’VAL(2);--variable V should be 'hold'3. counter and timer

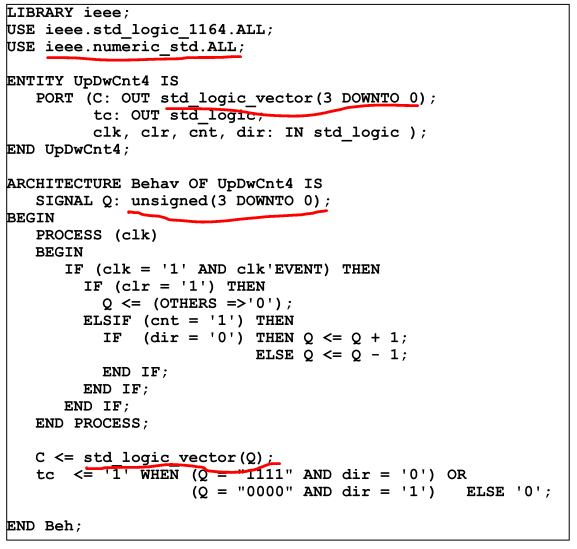

the module of the counter is based on the character of processes that the signals update when the process is finished. to simplify the process of adding '1's to the previous value we have to use the 'unsigned' type which is located in 'numeric_std' rather than 'std_logic_vector'. for the purpose of matching the previous type in the port definition, we force the changing of type in assignment statement at the end of the architecture.

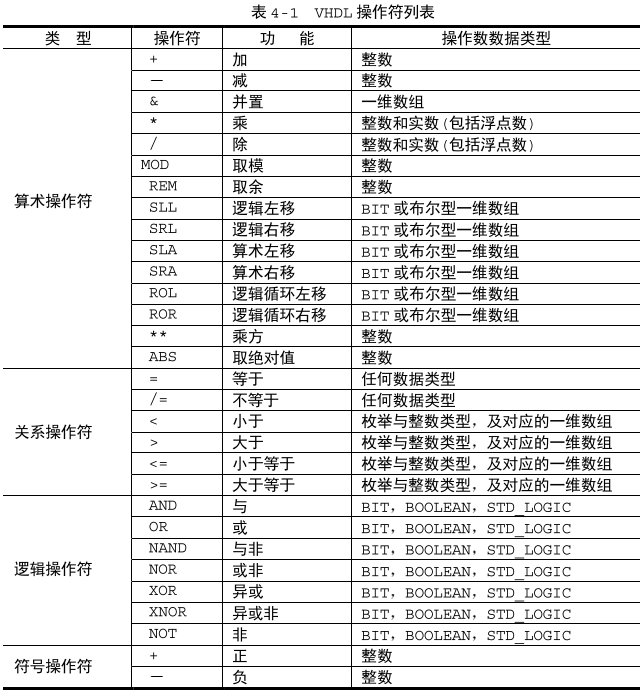

4. VHDL type and operator

type:

(no need to declare package)boolean, bit, bit_vector, character, integer, nature, positive, real, string, time, severity level

(std_logic_1164) std_logic, std_logic_vector

(std_logic_arith) unsigned, signed

(defined by user)

enumerate type:

type name is (a,b,c,d)

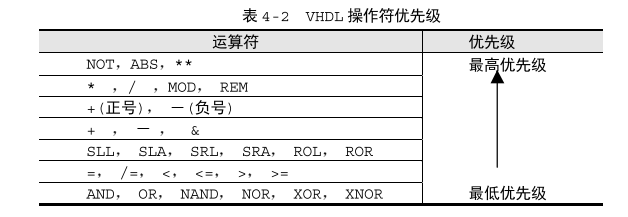

operator:

最后

以上就是粗犷小鸽子最近收集整理的关于学习日记之VHDL(2)的全部内容,更多相关学习日记之VHDL(2)内容请搜索靠谱客的其他文章。

发表评论 取消回复