设计门电路进行D触发器仿真,时序波形验证。

关于D触发器

D触发器的基本功能是在复位信号为1的时候,CLK的上升沿会引起Q值的变化

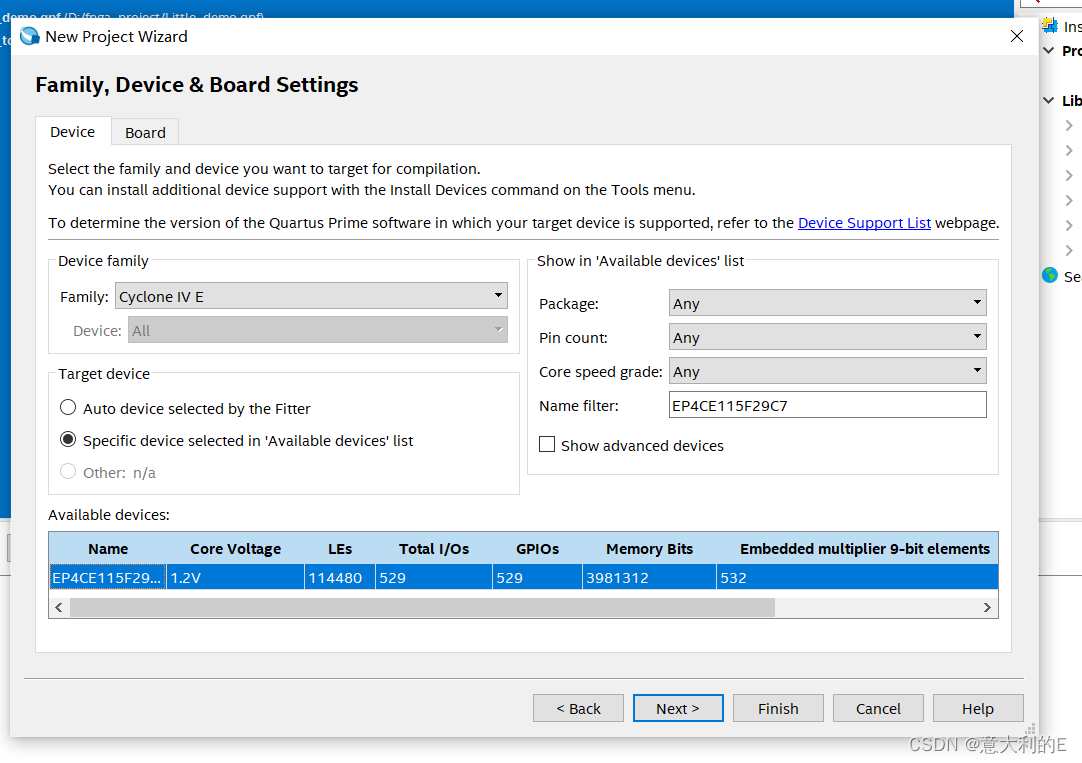

先创建项目,在这里我们可以选择想用的芯片:

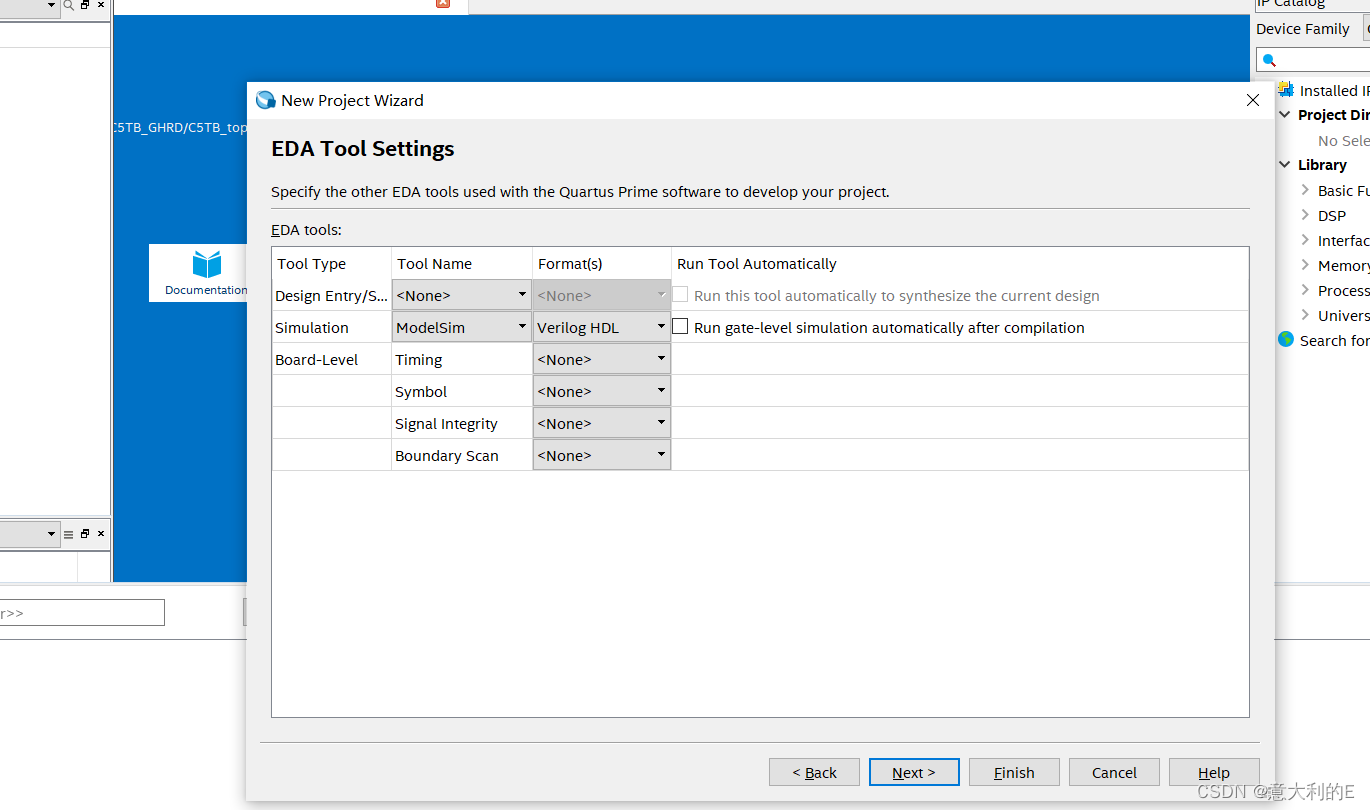

设置仿真软件为modelsim,语言为verilog

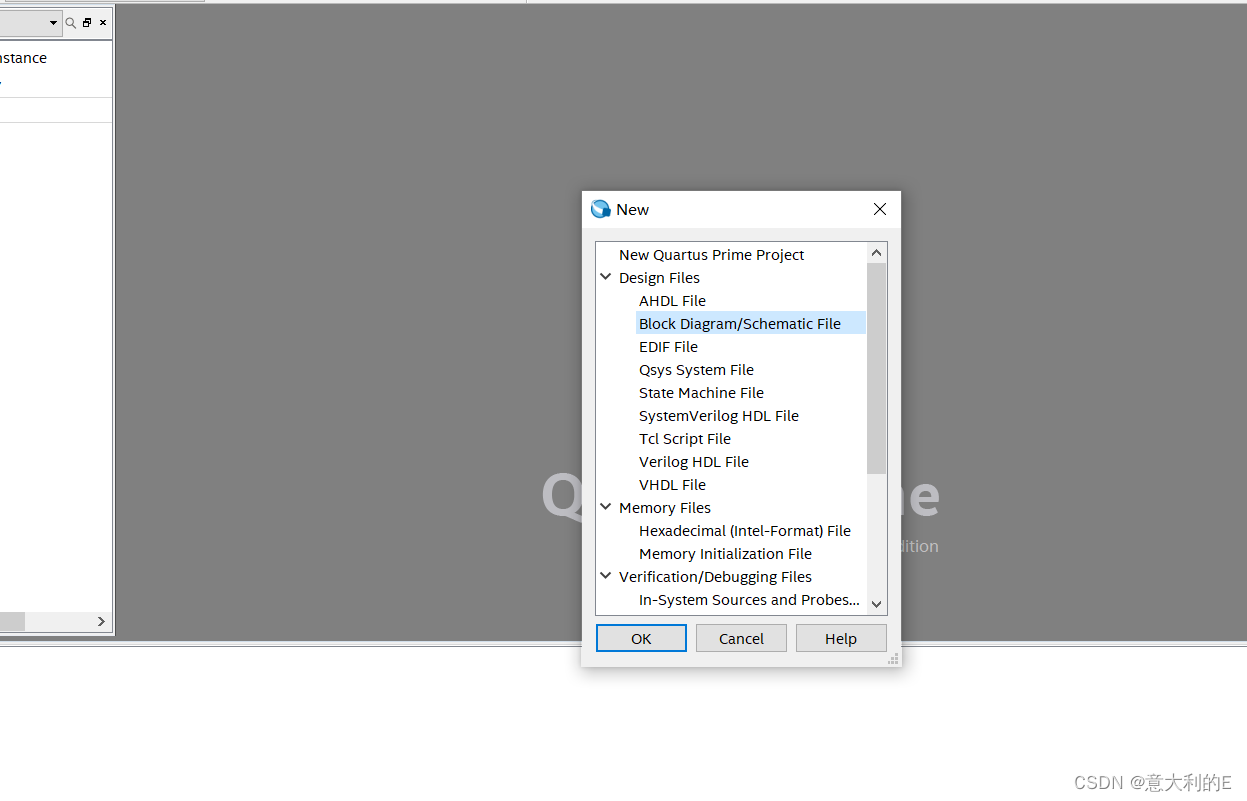

new一个block diagram文件

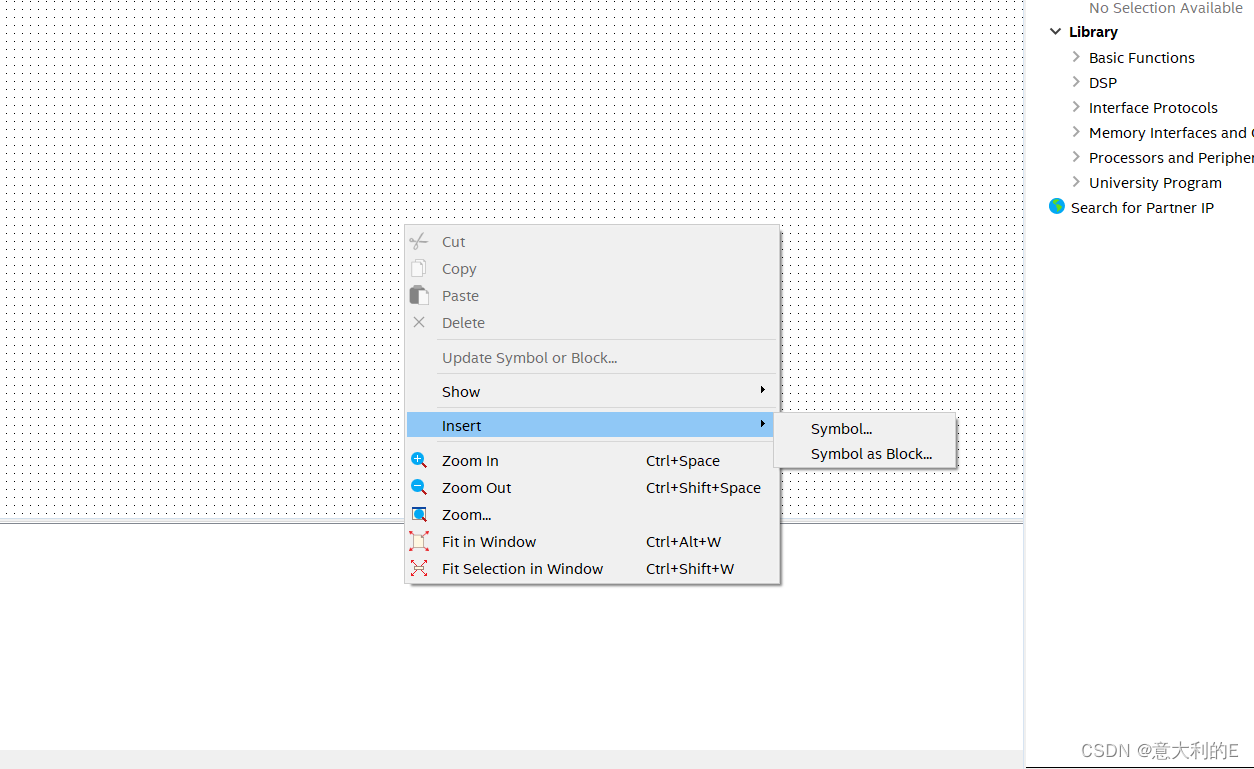

鼠标右键insert

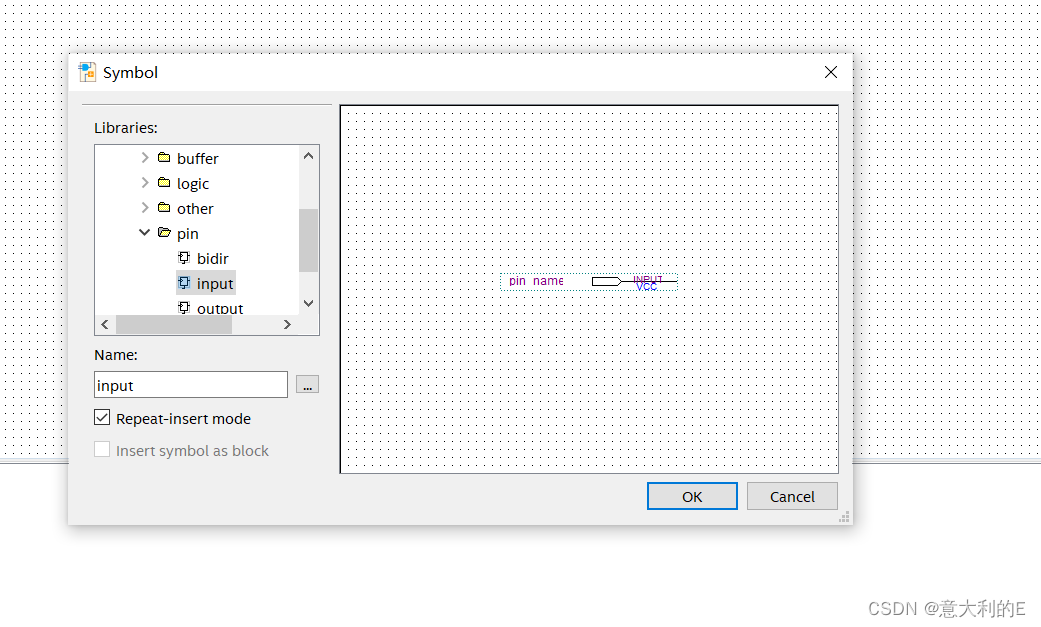

分别输入input(2),output(2),nand2(4),not(1),注意勾选repeat-insert mode

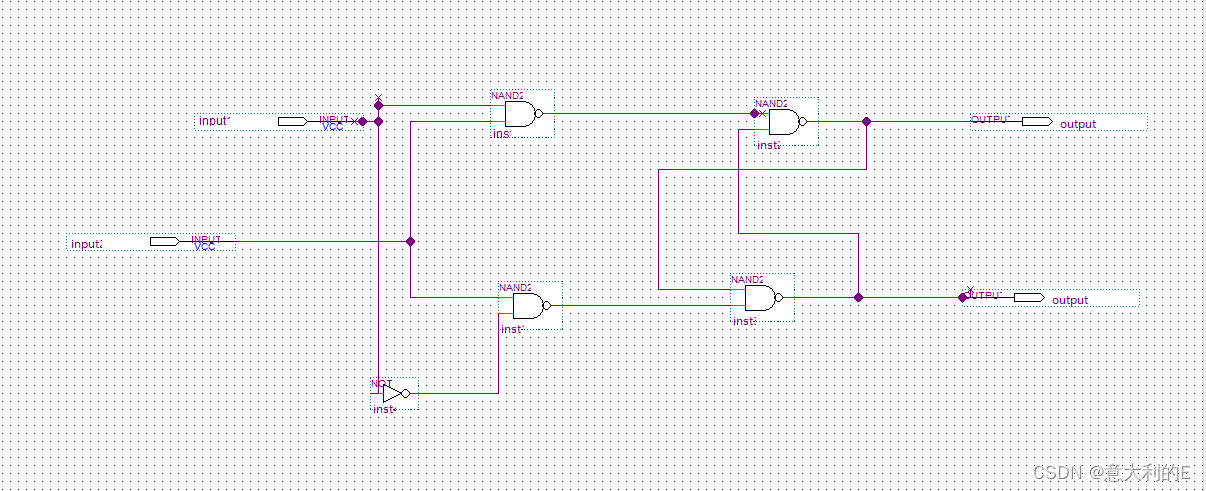

接线如下:

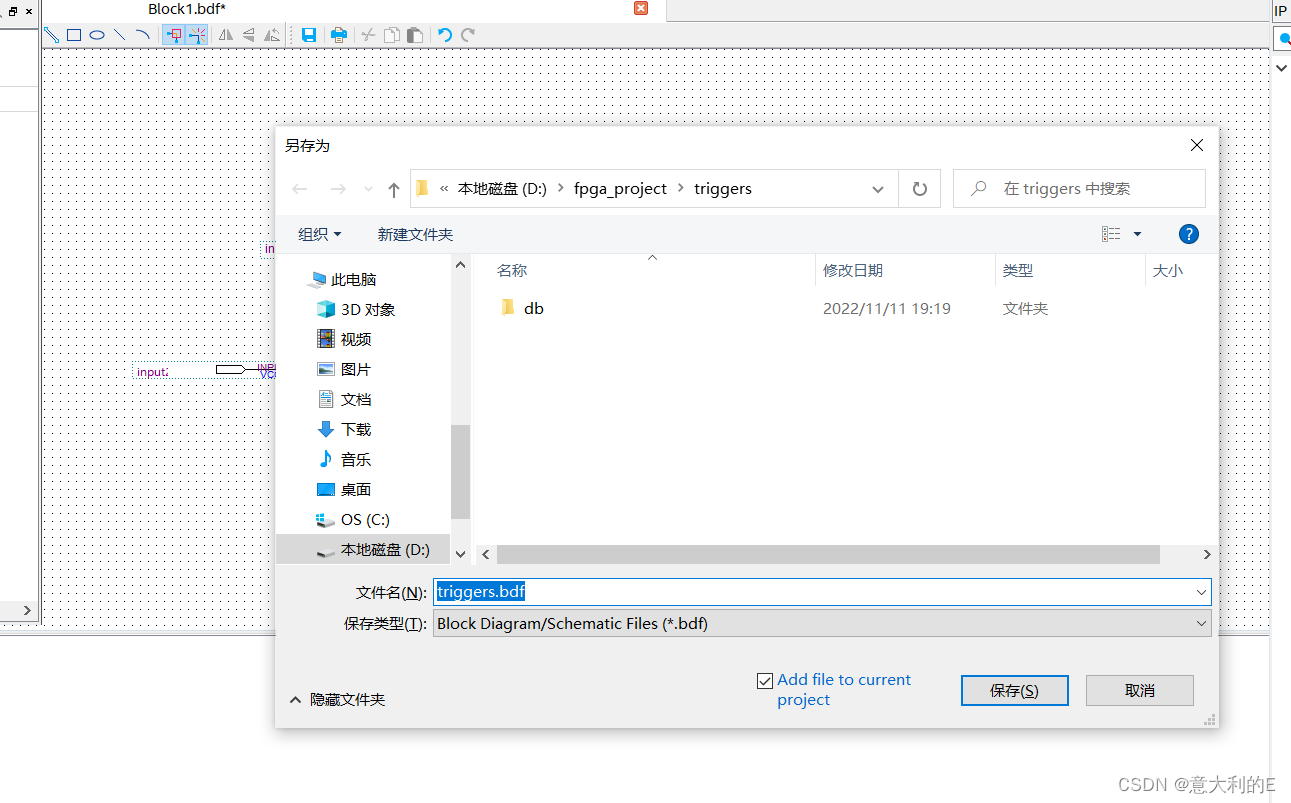

ctrl+s保存

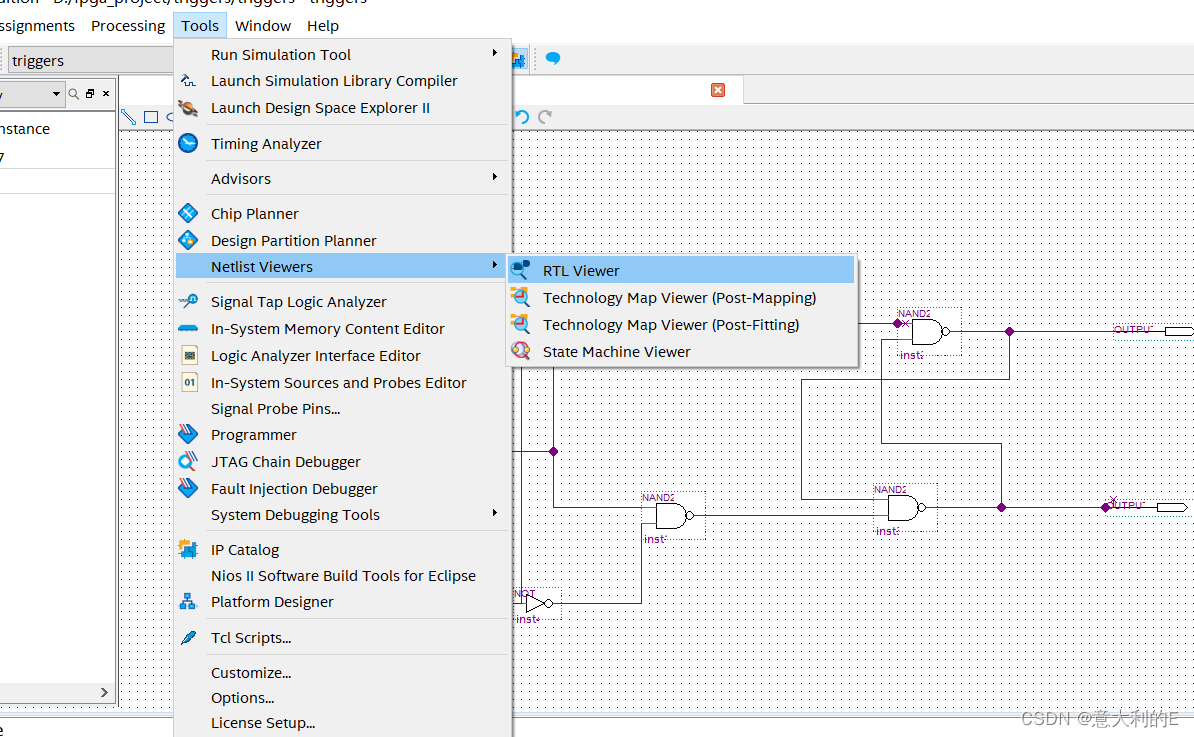

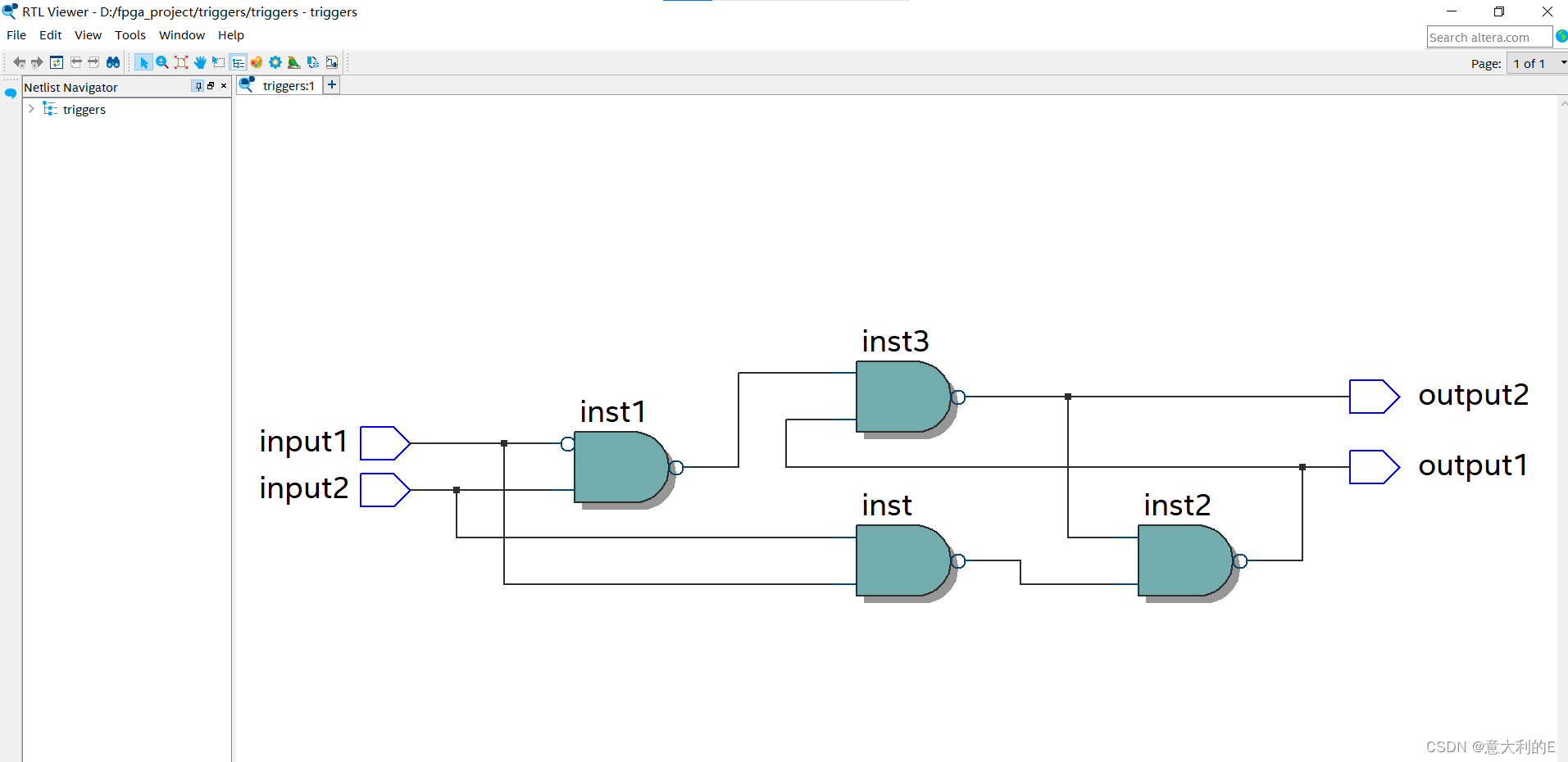

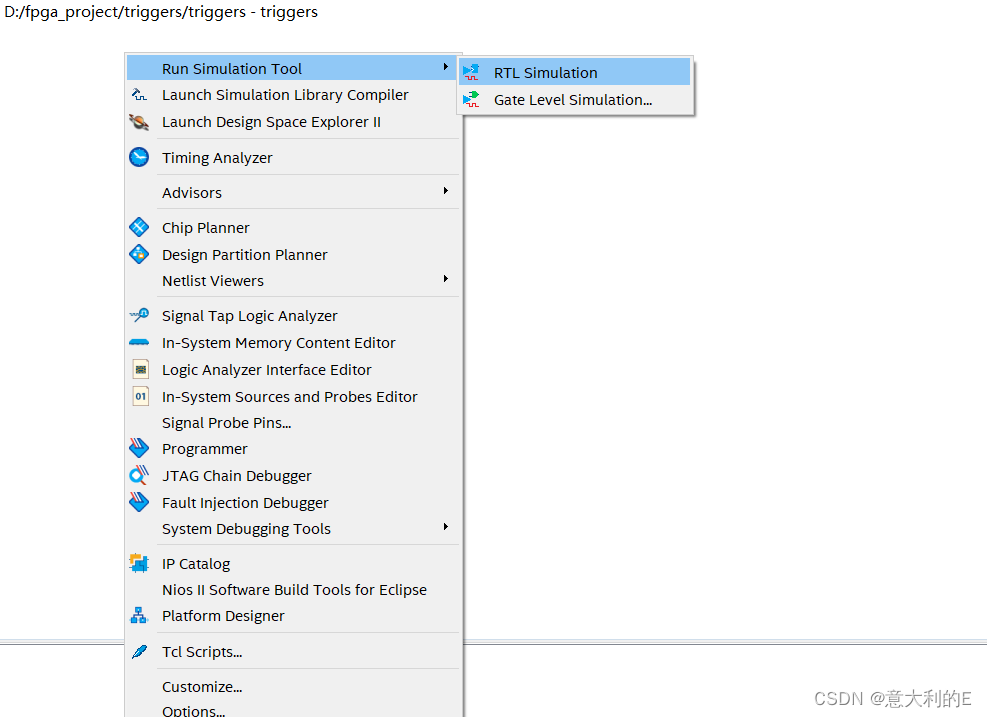

编译通过后选择RTL仿真

针不戳

quartus 18自带的仿真不好用,这里我们用modelsim做时序和功能仿真

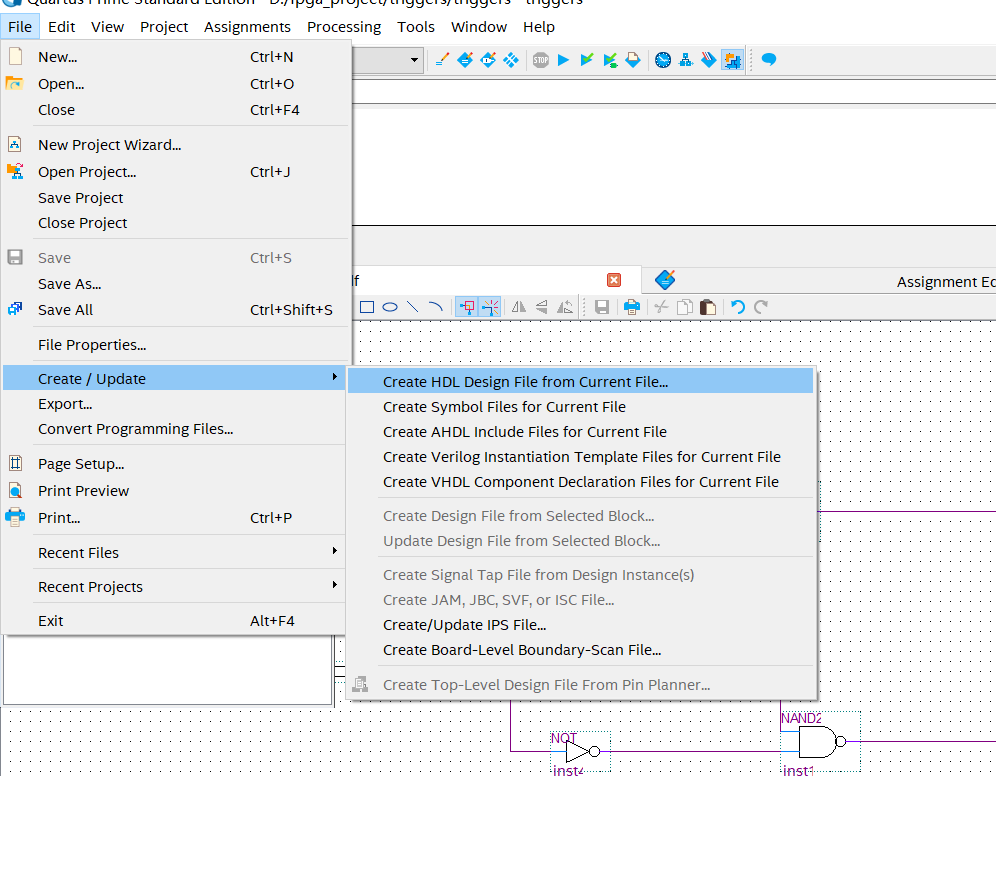

用原理图生成verilog文件,然后添加,注意如果新生成文件和bdf重名了要改变bdf文件名:

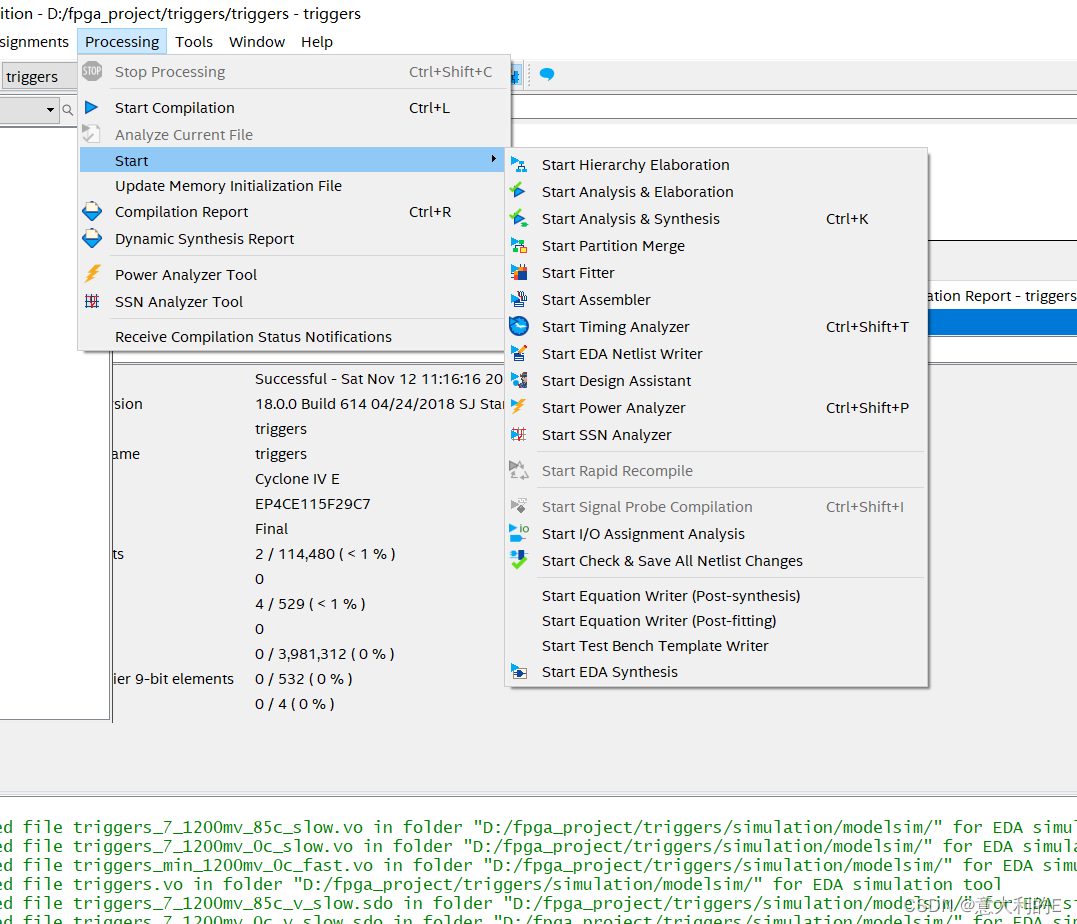

然后生成testbench:

要进行功能仿真,把vt代码修改如下:

// Copyright (C) 2018 Intel Corporation. All rights reserved.

// Your use of Intel Corporation's design tools, logic functions

// and other software and tools, and its AMPP partner logic

// functions, and any output files from any of the foregoing

// (including device programming or simulation files), and any

// associated documentation or information are expressly subject

// to the terms and conditions of the Intel Program License

// Subscription Agreement, the Intel Quartus Prime License Agreement,

// the Intel FPGA IP License Agreement, or other applicable license

// agreement, including, without limitation, that your use is for

// the sole purpose of programming logic devices manufactured by

// Intel and sold by Intel or its authorized distributors. Please

// refer to the applicable agreement for further details.

// *****************************************************************************

// This file contains a Verilog test bench template that is freely editable to

// suit user's needs .Comments are provided in each section to help the user

// fill out necessary details.

// *****************************************************************************

// Generated on "11/13/2022 09:22:32"

// Verilog Test Bench template for design : triggers

//

// Simulation tool : ModelSim (Verilog)

//

`timescale 1 ps/ 1 ps

module triggers_vlg_tst();

// constants

// general purpose registers

reg eachvec;

// test vector input registers

reg clk1;

reg inpin1;

// wires

wire out1;

wire out2;

// assign statements (if any)

triggers i1 (

// port map - connection between master ports and signals/registers

.clk1(clk1),

.inpin1(inpin1),

.out1(out1),

.out2(out2)

);

initial

begin

clk1 = 1;

inpin1 <= 0;

forever

begin

#60 inpin1 <= 1;

#22 inpin1 <= 0;

#2 inpin1 <= 1;

#2 inpin1 <= 0;

#16 inpin1 <=0;

end

end

always

begin

#20 clk1=~clk1;

end

endmodule

添加.vt文件

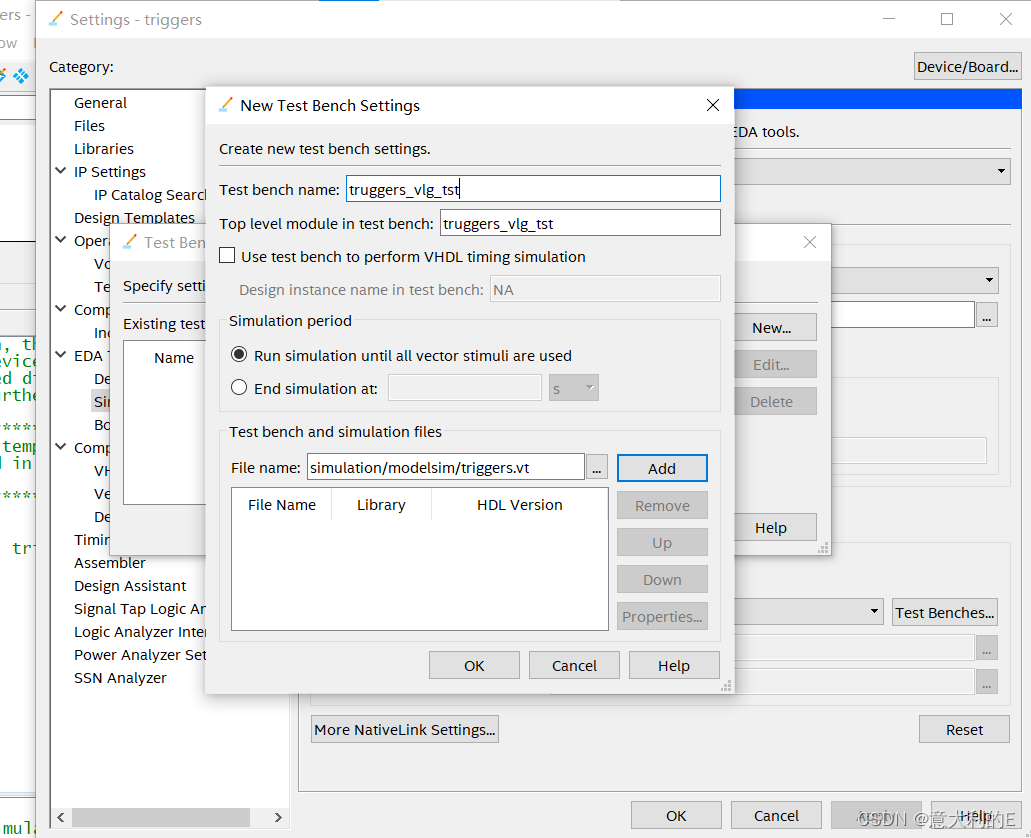

在settings里面添加testbench:

name就是.vt文件的模块名

点这里跳到modelsim:

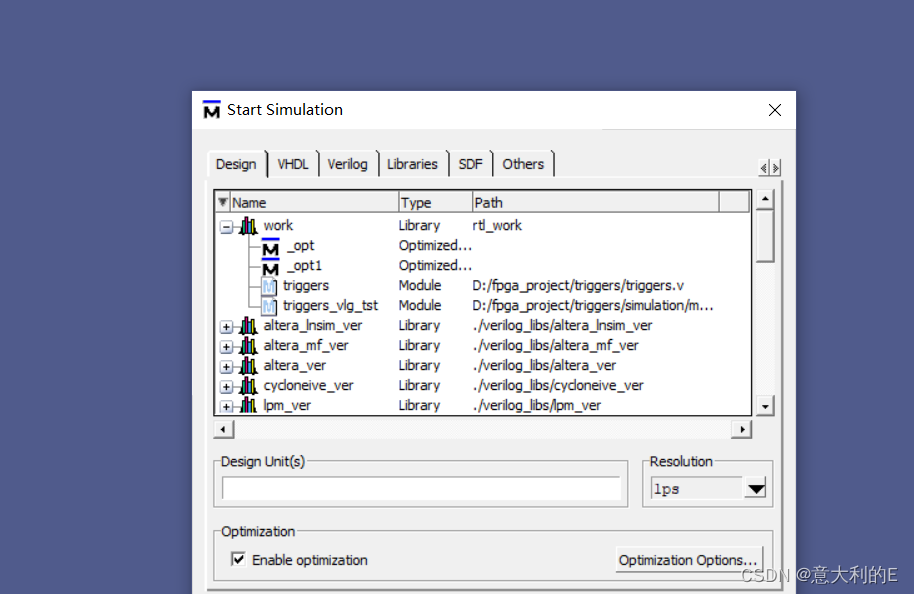

点simulate,在work目录下找到testbench文件:

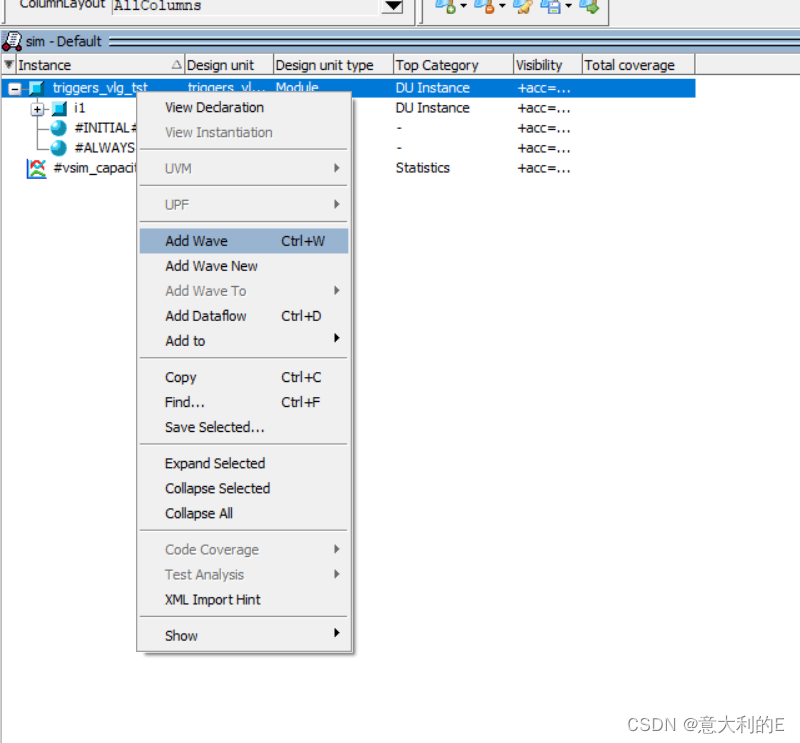

点击模块添加:

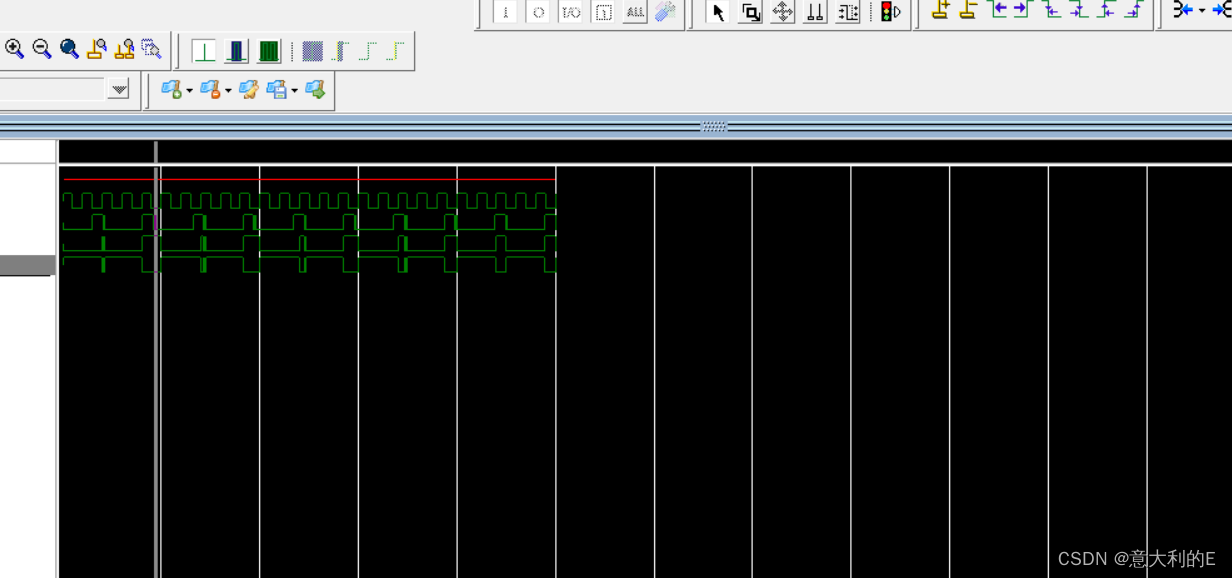

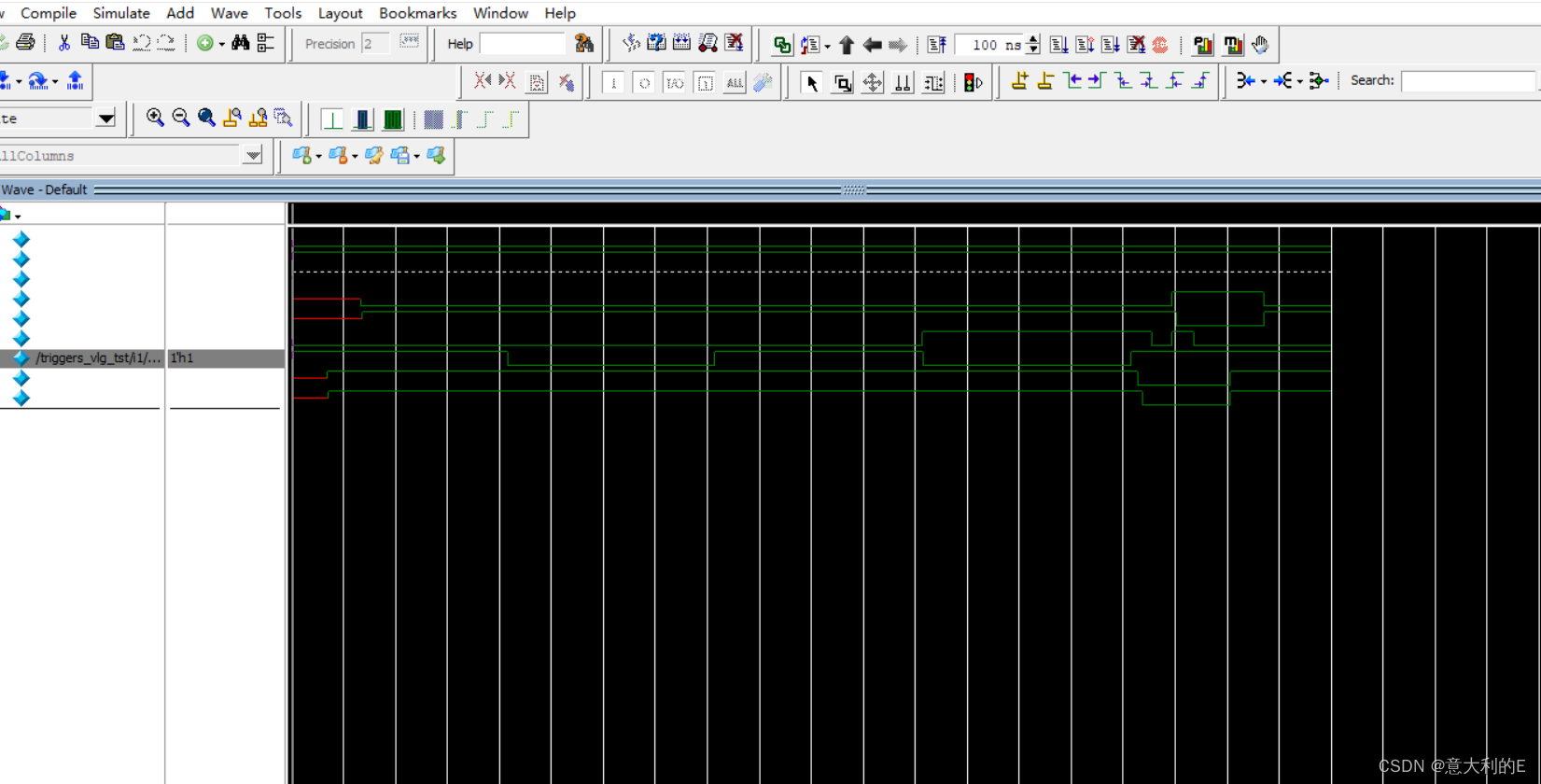

运行输出波形如下,out1和out2是最下面2个:

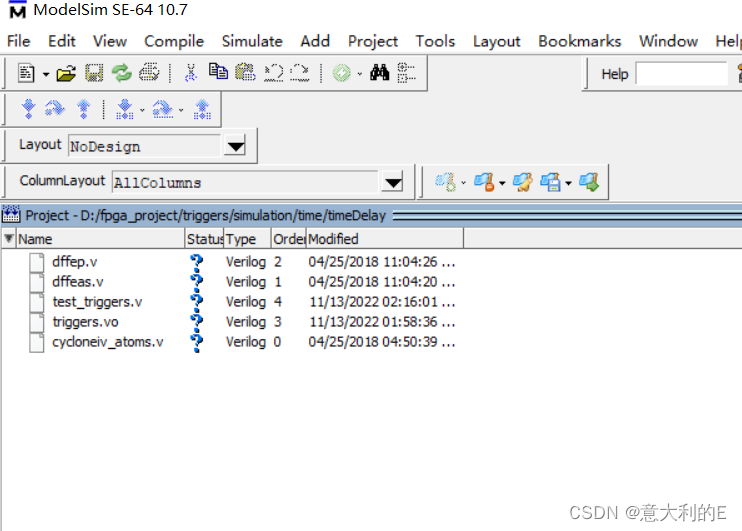

时序仿真稍微麻烦点,创建新项目目录如下:

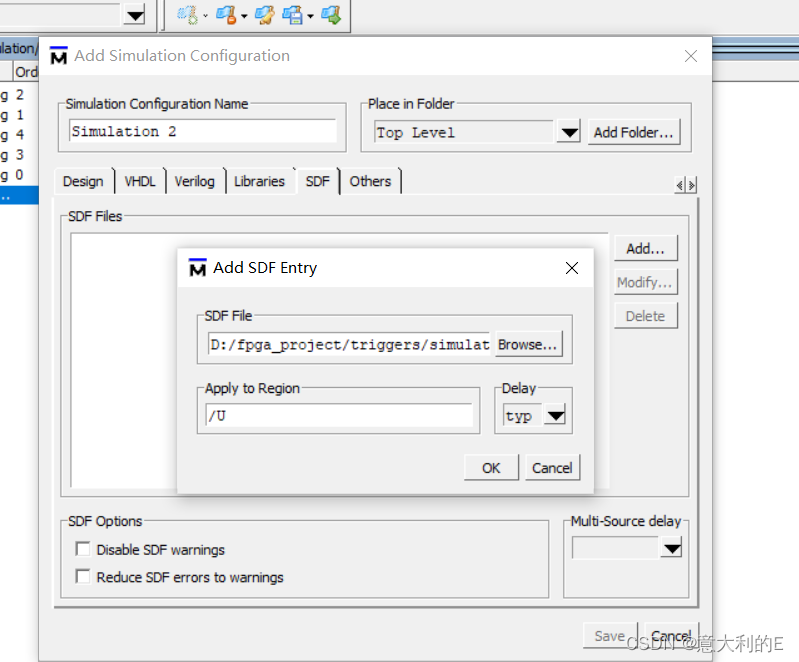

添加sdf选项卡

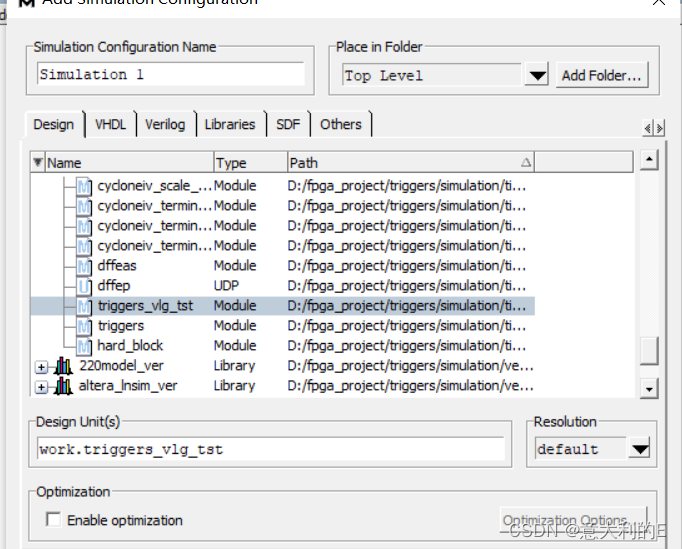

找到testbench文件

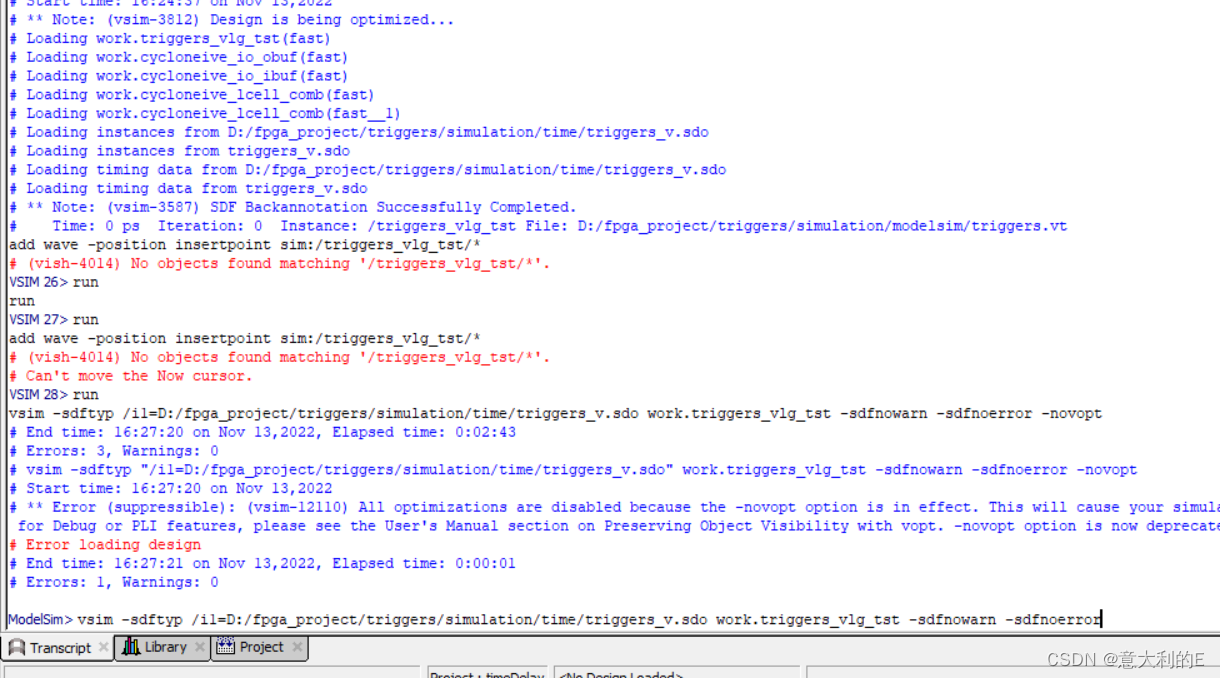

transcript命令行去掉最后的novopt执行

得到如下波形:

然后编写D触发器的代码:

module ddtrigger(D,CLK,Q);

input D;

input CLK;

output Q;

reg Q;

always @ (posedge CLK)

begin

Q <= D;

end

endmodule

vscode用testbench生成.vt文件内容如下:

`timescale 1ns / 1ps

module tb_ddtrigger;

// ddtrigger Parameters

parameter PERIOD = 10;

// ddtrigger Inputs

reg D ;

reg CLK ;

// ddtrigger Outputs

wire Q ;

ddtrigger u_ddtrigger (

.D ( D ),

.CLK ( CLK ),

.Q ( Q )

);

initial

begin

CLK = 1;

D <= 0;

forever

begin

#60 D <= 1;

#22 D <= 0;

#2 D <= 1;

#2 D <= 0;

#16 D <= 0;//维持16ns的低电平,然后让它做周期性的循环

end

end

always #(PERIOD/2) CLK=~CLK;

endmodule

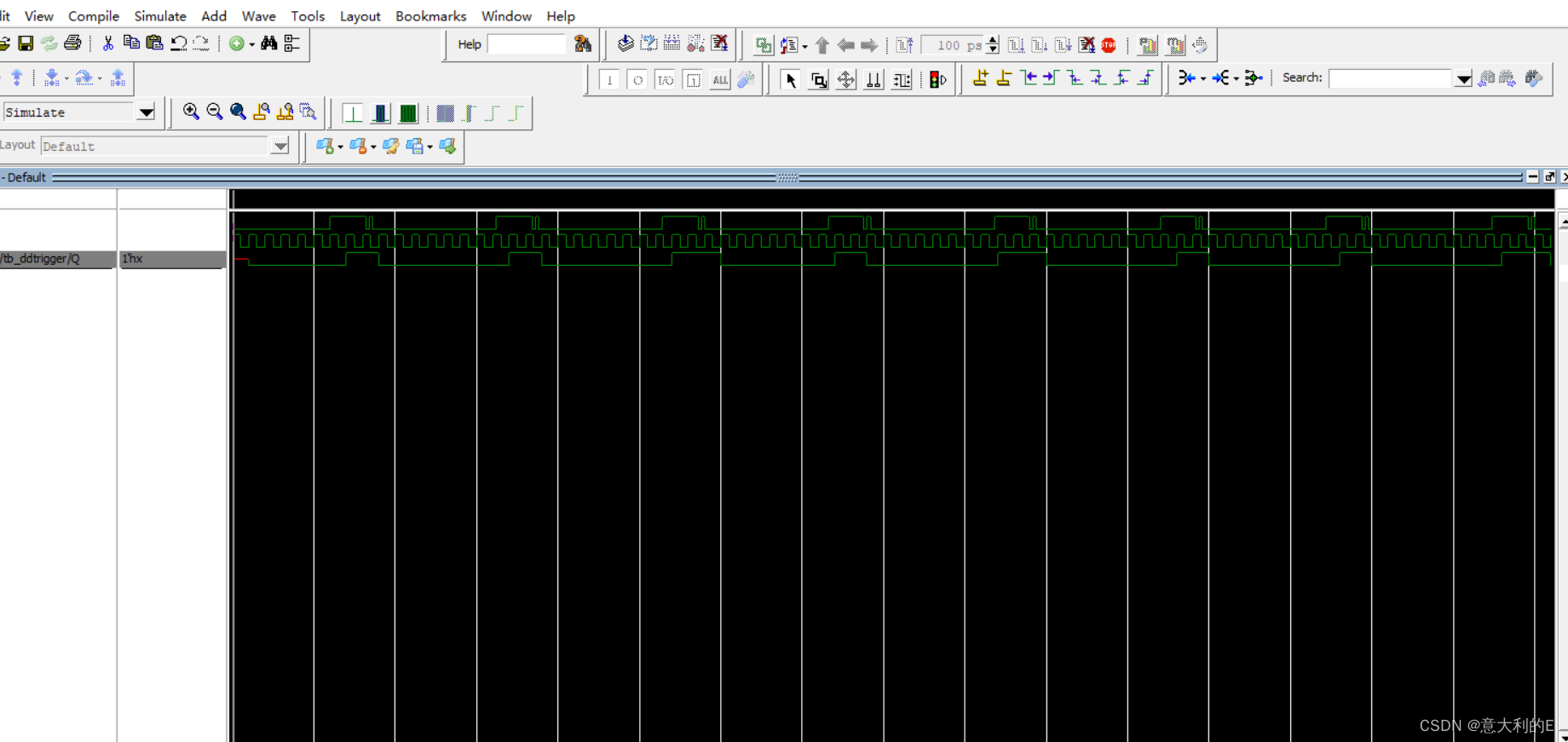

生成波形如下:

最后

以上就是受伤洋葱最近收集整理的关于Quartus-II编写触发器的全部内容,更多相关Quartus-II编写触发器内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

![[附源码]Python计算机毕业设计SSM开放性实验室网上预约管理(程序+LW)第四章 数据库设计](https://www.shuijiaxian.com/files_image/reation/bcimg17.png)

发表评论 取消回复