Abstract:文章内容来自于:哈工大计算机组成原理刘宏伟

主要介绍了静态RAM和动态RAM。

------------------------------------------------------------------------------------

一、静态RAM(SRAM):

(1)保存 0 和 1 的方式;

(2)基本单元电路构成;

(2)如何读入和写出?

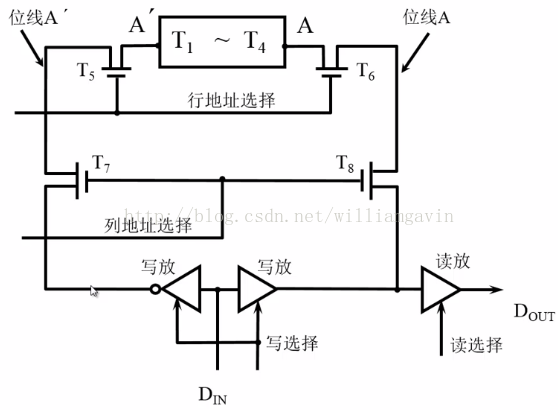

(1)静态RAM是利用四个触发器来保存 0 和 1 的(下图的 T1 ~ T4), 数据保存在 A' 和 A 端。

(2) 基本电路如下图。

(3)如何读写?

(3.1)读·:

行地址信号经过行译码之后行地址选择线有效, 打开T5 和 T6.

列地址信号经过列译码之后列地址选择线有效, 打开T7和T8.

A‘ 和 A 端的沿着导线读出, 其中当A’ 端信号到达左边那个写放大器截止, A 端信号通过读放大器输出到数据总线上。

(3.2)写:

信号从DIN输入,左边的写放大器是反向放大器, 即存储在A' 端的 与 存储到A端的信号相反。

DIN左 -> 反相 -> T7 -> T5 -> A'; DIN右 -> T8 -> T6 -> A;

二、动态RAM:

(1)保存0和1的原理;

(2)基本单元电路的构成。

(3)—对单元电路的读出和写入;

(1)动态RAM是利用电容来保存0和1的,电容有电荷为 1, 无电荷为 0;

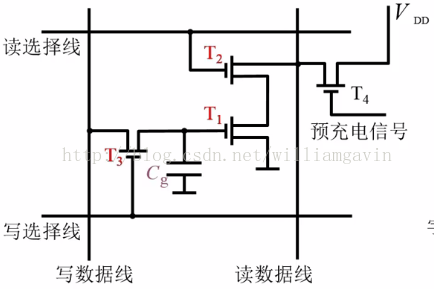

(2)基本单元电路有两种, 第一种如下

(3)由Cg存储 0 和 1. T1、T2、T3三个管子来控制读写。

(3.1)如果进行读操作,首先预充电信号将T4管子充电导通, 然后VDD电压会将读数据线上电平拉高。如果Cg没有 电荷, 此时渎选择线有效, T2管子导通;即存储的 是 0, 那么 T1 管子截止, 那么此时读数据线上为高电平, 即当Cg上存储 0 时, 读数据线为 1. 如果Cg为1时,T1导 通, 读数据线上电平被拉低, 即当Cg为1时,读数据线为 0;也就是说, 你读出的电平与实际电平是相反的。 此时需要加一个非门。

(3.2)如果是写入的话, 那么写选择线有效, T3导通, 如果写数据线为 1,那么Cg有电荷为 1, 反之则为 0. 也就是说 写入的电平和实际的相同。

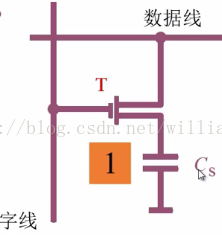

第二种电路

进行读操作, 设置字线为高电平, T 导通, 那么如果Cs为1, 那么数据线为高电平, 如果为 0, 那么数据线为低电平。如果写入的话也是一样的。 这种方法比上面

那种简单很多、

动态RAM(DRAM)刷新问题:可以参考:点击打开链接 和 点击打开链接

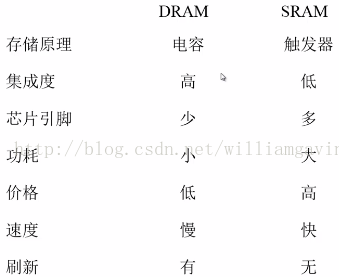

三、动态RAM和静态RAM的比较:

DRAM适合做主存, SRAM适合做缓存。

最后

以上就是甜美鸡最近收集整理的关于存储器(三) - 主存(二)的全部内容,更多相关存储器(三)内容请搜索靠谱客的其他文章。

发表评论 取消回复