嵌入式系统中,不同芯片之间通常使用串行总线的方式进行连接,根据器件行业规范、应用场景,不同芯片通常选择不同的串行通信接口进行通信。常用的串行通信接口有:1-Wire、I2C、SPI、UART。

一、1-Wire

1-wire单总线是Maxim的全资子公司Dallas的一项专有技术。该技术支持使用单线(加地线)实现通信和电力传输(但大部分单总线器件电力传输还是使用独立的电源线)。单个总线主机可以通过单双绞线电缆连接单总线设备。这项技术的一个重要方面是,每个从机都有一个全球唯一的64bit数字地址。

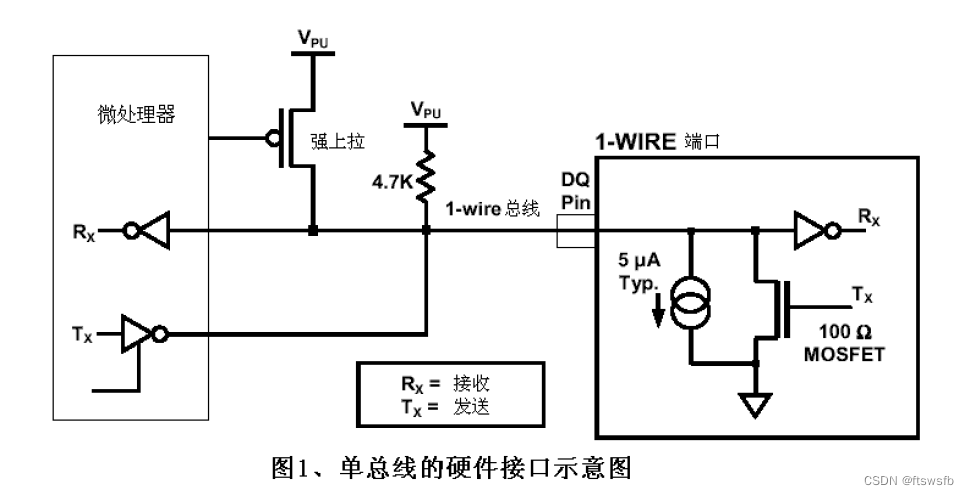

什么是1-Wire总线?1-Wire总线是一种基于PC机或微控制器的低成本总线,通常使用双绞线与1-Wire器件连接进行通信。设备(主机或从机)通常使用一个漏极开路或三态端口连接至该数据线,这样允许设备在不发送数据时释放数据总线,以便总线被其他设备所使用。

一般来说,1-Wire总线设备的总线上需要外接一个4.7k的上拉电阻,以保证总线空闲时为高电平。对于使用总线提供电源的设备,为了保证器件工作期间能够有足够的电源电流,必须在总线上提供强上拉(通常使用MOSFET)。

一般来说,1-Wire总线设备的总线上需要外接一个4.7k的上拉电阻,以保证总线空闲时为高电平。对于使用总线提供电源的设备,为了保证器件工作期间能够有足够的电源电流,必须在总线上提供强上拉(通常使用MOSFET)。

另外1-Wire总线系统规定·:除了主节点主动请求通信,从节点不允许主动发起通讯;并且除了通过主节点,从节点之间不允许通信。1-Wire协议使用传统的CMOS/TTL逻辑电平,允许在2.8v到6v的电源电压范围内操作。主从设备都可以被配置为收发器,允许位数据向任意一个方向流动,但是一次只能向一个方向流动,并且首先读取和写入最低有限位(LSB)。

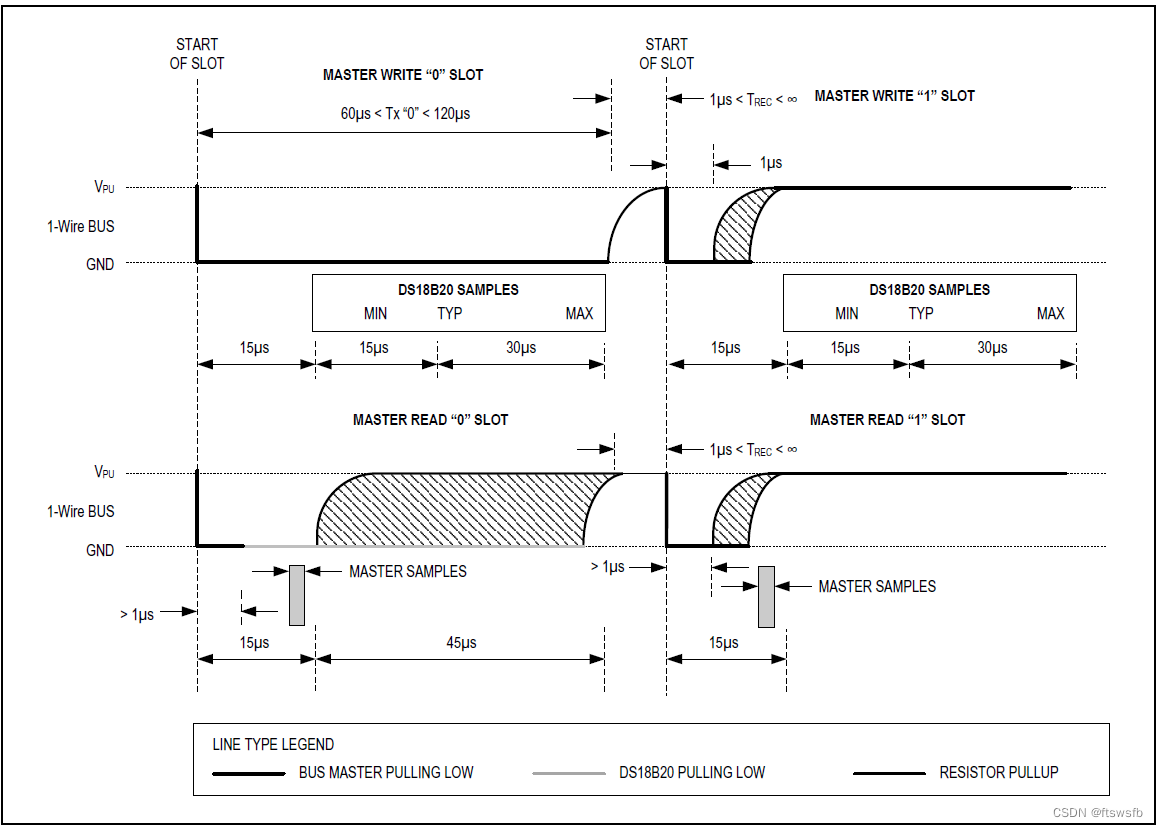

- 读写时序

在1-Wire总线上数据是按照时隙进行传输的。例如:要向从机写入逻辑1,主机需要将总线拉低15us或更少;为了写入一个逻辑0,主机需要将总线拉低至少60us,以为最坏的情况提供事件阈值。在通信期间1-Wire从机内部的振荡器时钟与下降沿进行同步,因此不需要同步的系统时钟。

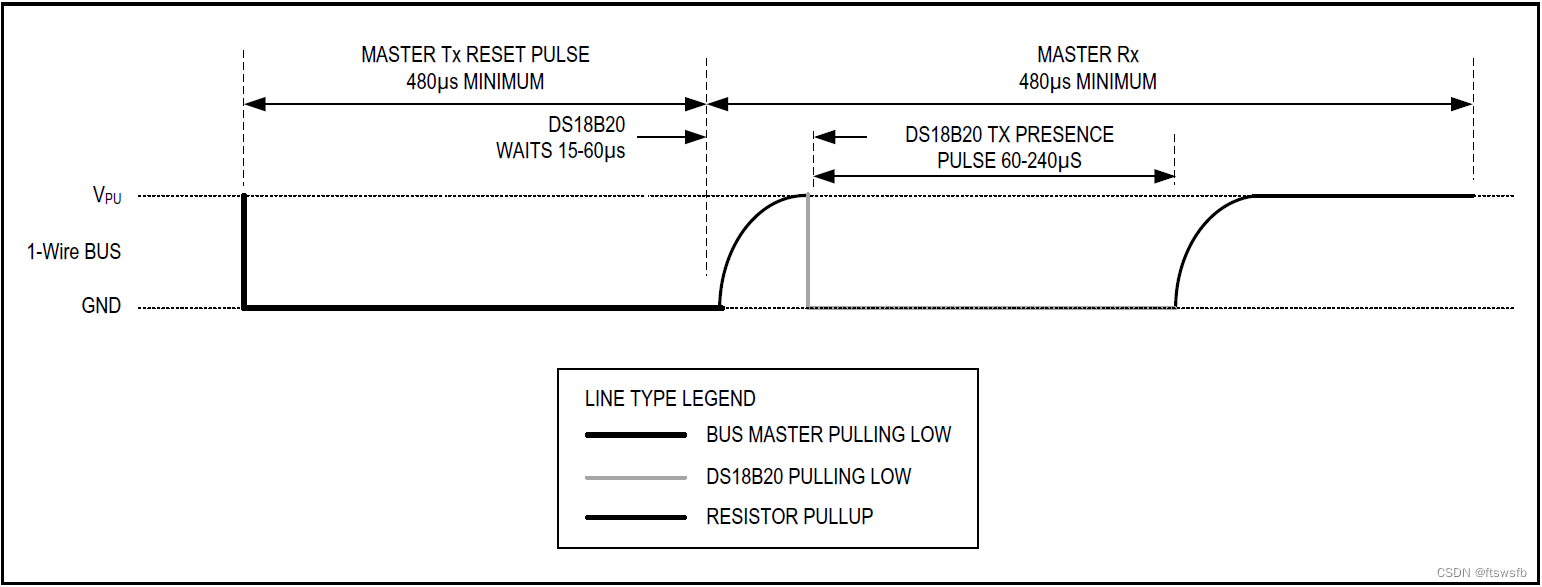

- 初始化时序

在设备初次握手时,主机通过保持总线低电平至少480us来重置网络,然后释放总线,再从总线中寻找从机响应的脉冲。一定握手成功,主机就可以发出特定的设备命令,与从机之间进行任何所需的数据传输。

1-Wire主机可以从总线上选择一个任意设备,因为每个1-Wire设备都有唯一的数字地址。 * 电源

* 电源

对于电源,在数据线处于高电平的空闲通信期间,通过1-Wire设备上面的半波整流器后向片内电容进行充电,从而实现总线供电(这种从网络中“窃取”电力的概念被称为“寄生电力”,但目前接触到的设备,都有独立的VCC接口,可能是基于成本的考虑吧)。

典型器件:温度传感器DS18B20、温湿度传感器DHT11

通信速率:< 16.7Kbit/s

二、I2C

I2C为飞利浦定义的器件间同步通信协议,规范版本变动如下:

-

Version 1.0 - 1992

- 移除从机地址可软件编程。该特性实现十分复杂并且还未使用过。

- “低速模式”被移除。实际上,这种模式是整个i2c总线规范的一个子集,不需要明确指定。

- 增加快速模式。这将使比特率提高了四倍,最高可达400kbit/s。快速模式的器件向下兼容,即他们可以用于0到100kbit/s的I2C总线系统。

- 增加10bit设备地址。这将允许扩展到1024个从机地址。

- 快速模式的设备支持斜率控制和输入滤波,以改善EMC行为。

-

Version 2.0 - 1998

- 增加高速模式。这将支持将比特率提高到3.4Mbit/s。高速模式的器件向下兼容,即他们可以用于0到3.4Mbit/s的I2C总线系统。

- 调整电源电压为2v及以下的器件的输出低电平迟滞现象,以满足所需的噪声裕度,并与更高的电源电压器件保持兼容。

- 快速模式下输出6mA时0.6V电压的要求被移除。

- 新设备输入固定电平使用总线相关电压电平代替。

- 增加双向电平移位器的应用信息。

-

Version 2.1 - 2000

- 高速模式下,RESTART后可以拉伸时钟信号SCLH。

- 高速模式下,一些定时参数放宽。

标准规范中,定义了I2C设备需要遵讯的电气特性(主要为设备设计人员所关心)和I2C总线、时序特性(主要为I2C设备应用人员所关心)。

-

总线结构

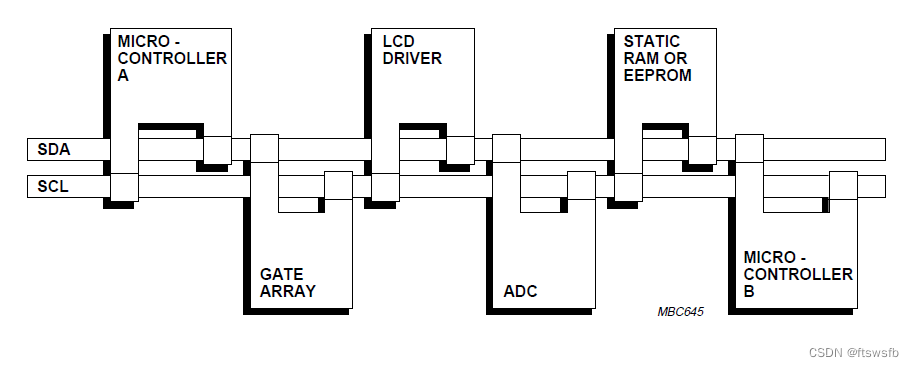

I2C总线时序双线方式(SDA和SCL)进行通信,总线上支持挂载多个器件(每个器件需要有唯一的设备ID)。

I2C总线上所挂载设备的I2C接口均应为开漏输出的设备,总线上使用通常使用4.7k的上拉电阻将总线在空闲时拉高至电源电平。

I2C总线上所挂载设备的I2C接口均应为开漏输出的设备,总线上使用通常使用4.7k的上拉电阻将总线在空闲时拉高至电源电平。

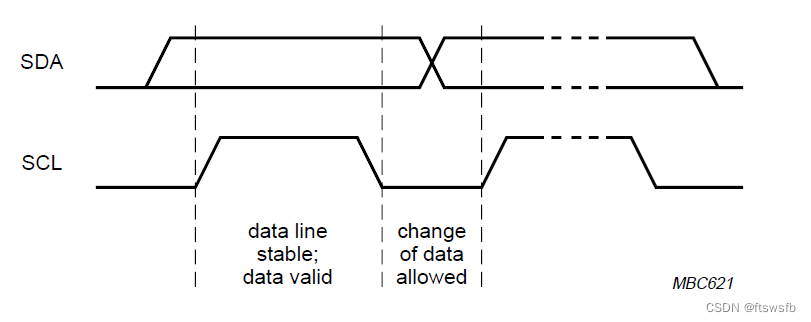

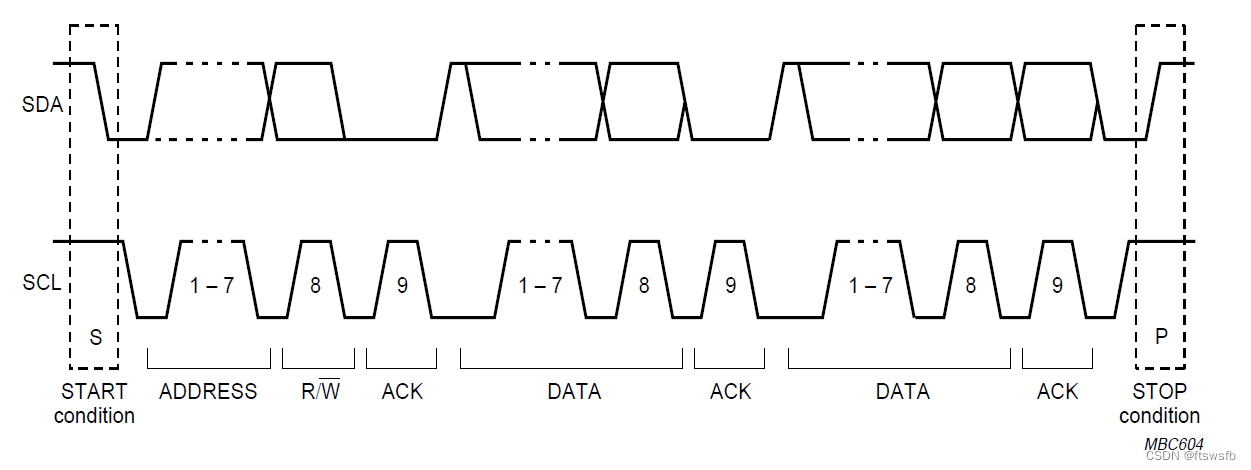

在总线传输数据时,SCL为低电平时,允许SDA电平(数据)改变;在SCL为高电平时,SDA电平(数据)应保持稳定。

在总线传输数据时,SCL为低电平时,允许SDA电平(数据)改变;在SCL为高电平时,SDA电平(数据)应保持稳定。

-

启停时序

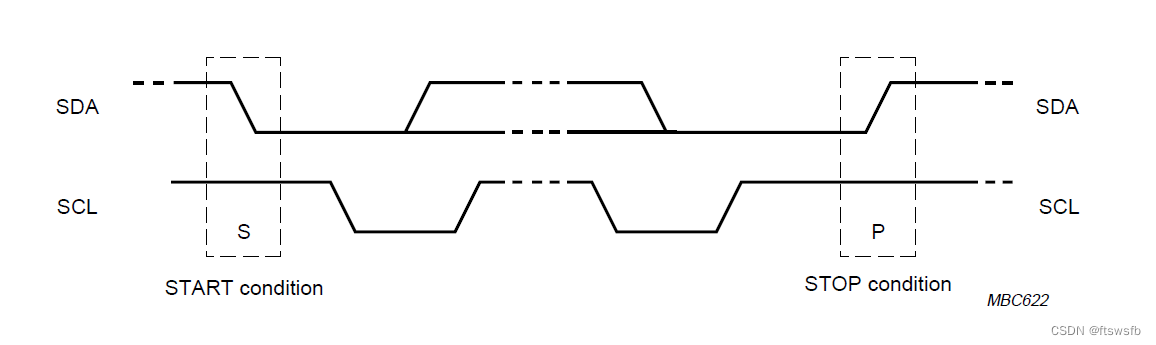

I2C规范定义了在总线上传输信息的启停信号。上面提到,在I2C总显示在SCL高电平时,SDA应保持稳定已完成数据的传输。而在SCL为高电平时,SDA的数据变化,被定义为I2C的启停信号:

当SCL为高电平时,SDA从高电平向低电平跳变为启动时序;

当SCL为高点评时,SDA从低电平向高电平跳变为停止时序。

-

读写时序

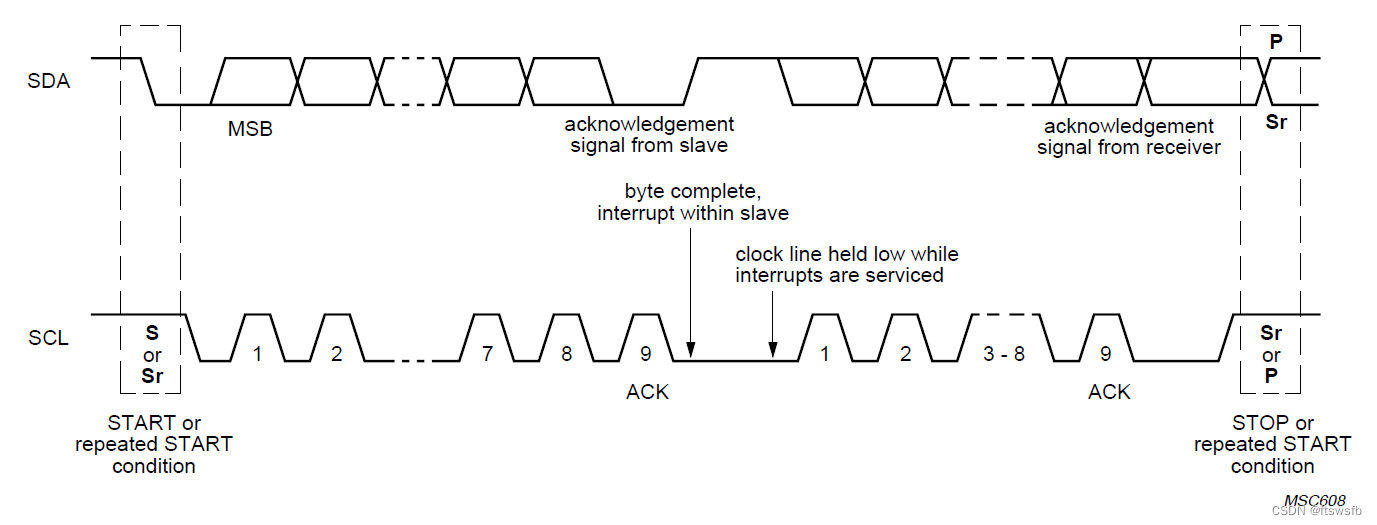

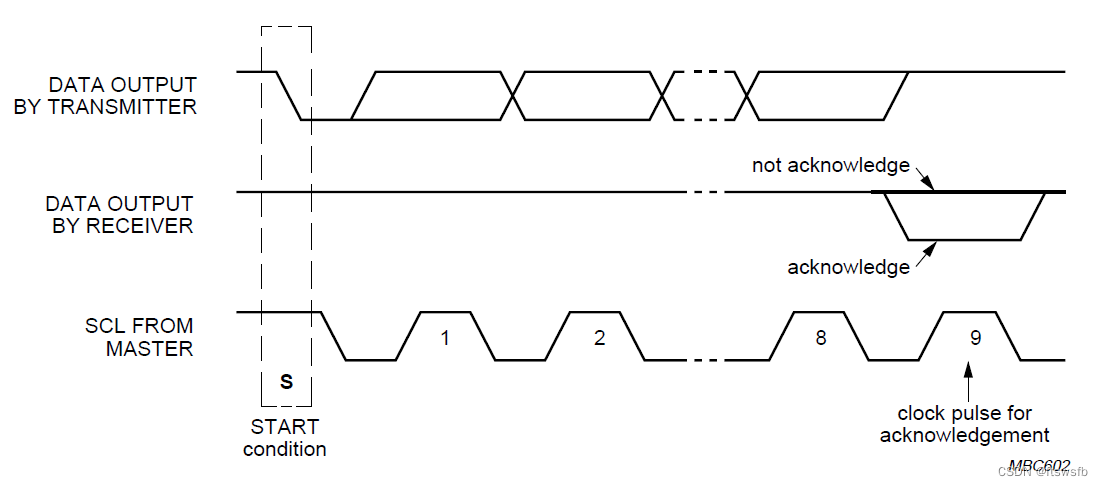

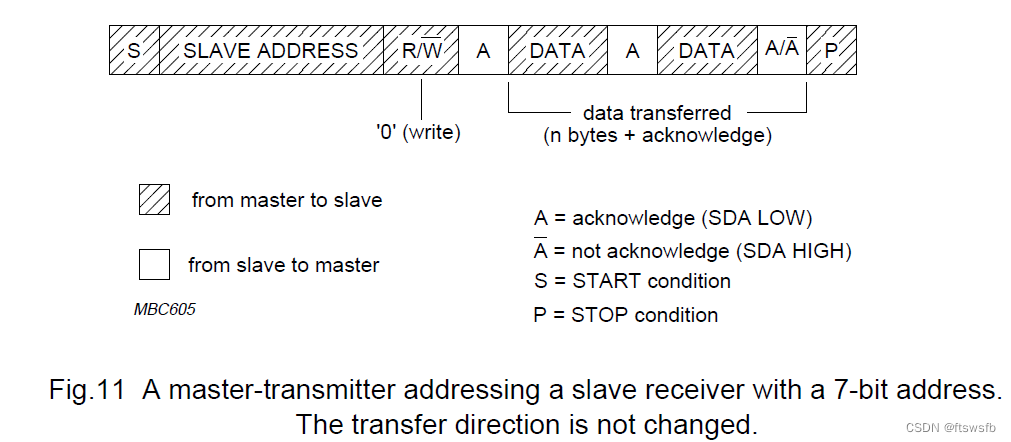

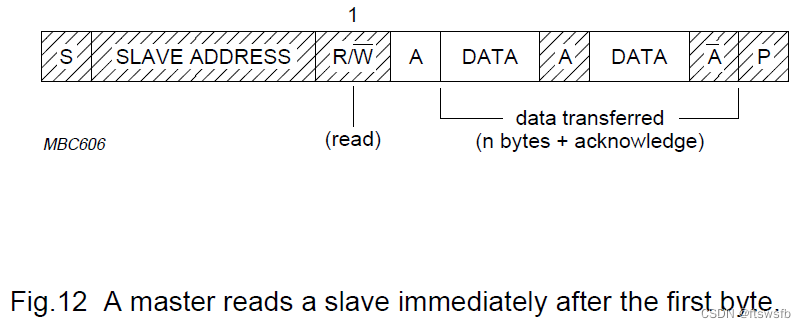

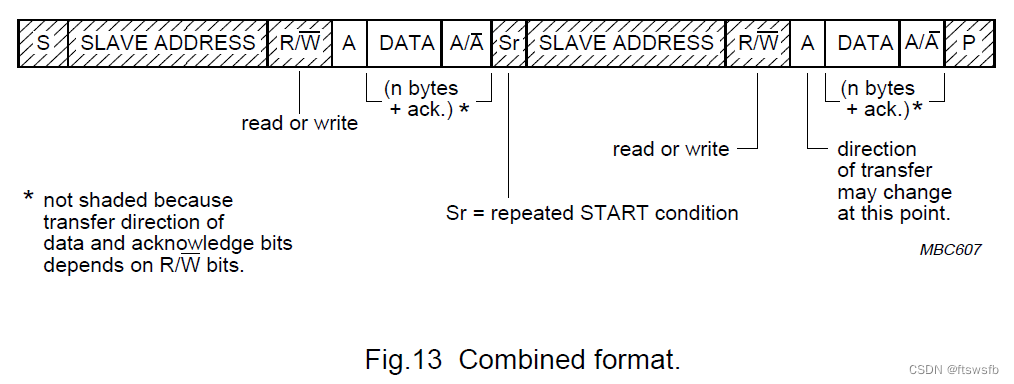

在I2C总线传输数据时,SDA线的数据必须固定为8bit的长度(MSB在前)。当主机向I2C从机写入8bit数据时,从机应给予访问主机ACK/NACK信号;相反,当主机从I2C从机读取8bit数据时,主机应给予访问的从机ACK/NACK信号。

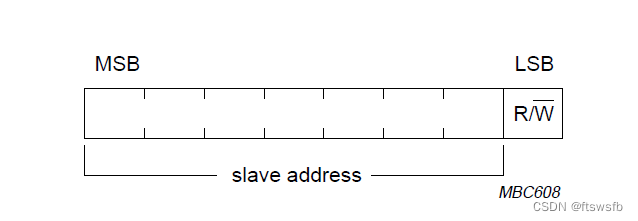

I2C规范除了定义了链路层的时序,也定义了应用层的时序,用于I2C设备数据的读写控制。如下图,I2C设备地址为7bit,在传输过程中另外一个bit用于 表示对I2C设备的读写操作(0为写,1为读)。

I2C规范除了定义了链路层的时序,也定义了应用层的时序,用于I2C设备数据的读写控制。如下图,I2C设备地址为7bit,在传输过程中另外一个bit用于 表示对I2C设备的读写操作(0为写,1为读)。

-

设备地址

根据规范,I2C设备支持7bit地址和10bit地址,7bit地址比较容易理解:7bit地址+1bit控制,组曾1byte数据进行传输。

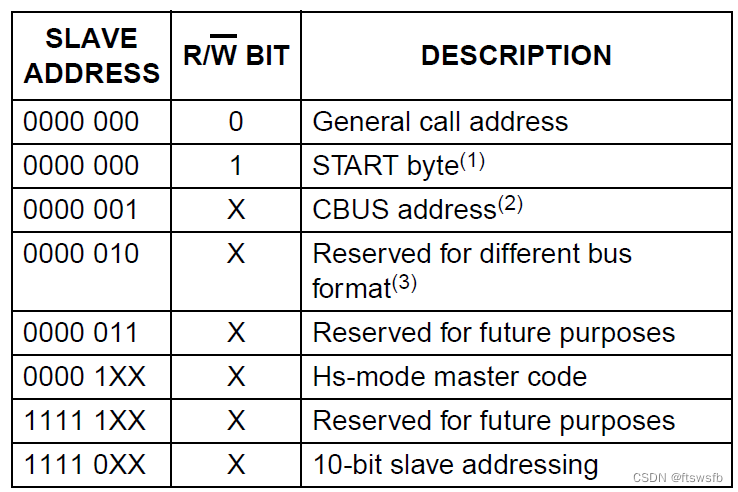

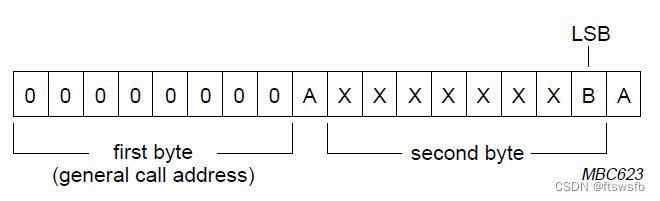

对于10bit地址,I2C规范额外定义了地址范围规范:

基于对I2C规范的理解,就可以开发I2C主机程序,但对于具体的I2C器件,还要结合手册具体的调试,因为某些I2C器件在设计上可能不是很符合标准规范。

典型器件:EEPROM存储器AT24Cxx

通信速率:标准模式100Kbit/s,快速模式400Kbit/s,高速模式3.4Mbit/s

三、SPI

SPI,Serial Peripheral interface的缩写,为Motorola定义的串行外围设备接口,一种高速、全双工、同步的通信总线。

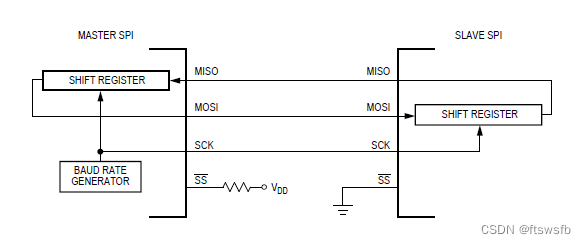

SPI使用主从机通信的方式,一个SPI总线系统中,仅支持一个主机设备。SPI设备通信时,使用4根线进行交付:SSN,片选,用于选择通信的设备;SCK,时钟线,由主机发出从机接收,数据传输过程中的同步时钟;MOSI,数据线,主机设备的输出,从机设备的输入;MISO,数据线,主机设备的输入,从机设备的输出。

每个SPI主机,可以通过使用多个SSN管脚控制不同的SPI设备,从而实现SPI总线挂载多个SPI设备,节约通信用IO。

相对于I2C,SPI总线比较简单,SPI规范仅定义了链路层的时序,而应用层协议为使用SPI接口的器件自行定义实现。

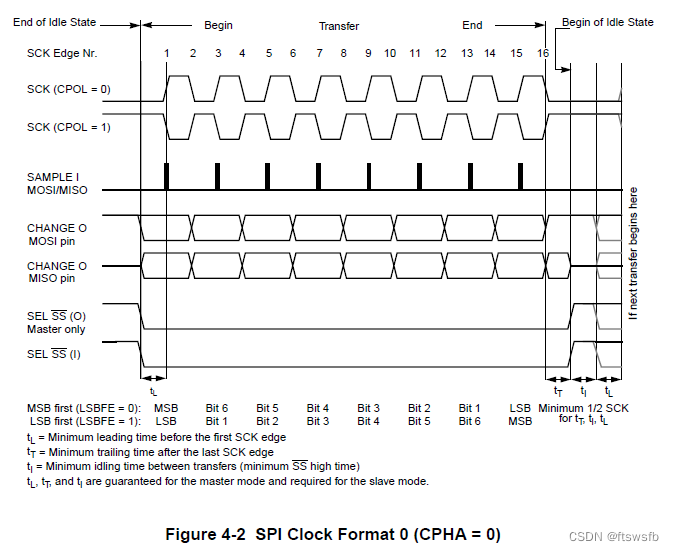

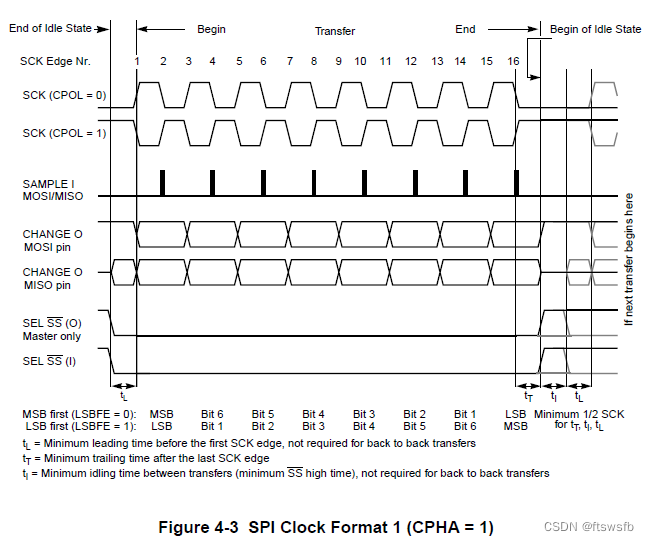

对SPI总线来说,需要注意的是CPOL(时钟的极性)和CPHA(数据采样时的时钟边沿)两个属性,主机和从机需要保持统一一致。

典型器件:NorFlash存储器W25Qxx

通信速率:未规定,最高已达到50Mbit/s

四、UART

UART,通用异步收发器(Universal Asynchronous Receiver/Transmitter),是一种串行、异步、全双工的通信协议,在嵌入式领域应用可以用于板件通信,调试日志输出等,应用十分广泛。

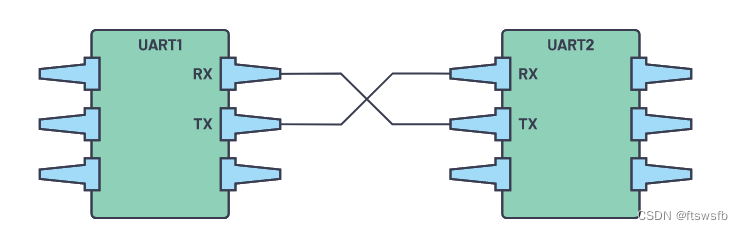

UART全双共通信时,仅需两条数据线RX和TX(当然通信的两个器件需要共地),两个设备的RX和TX管脚,需要彼此交叉连接,如下图。

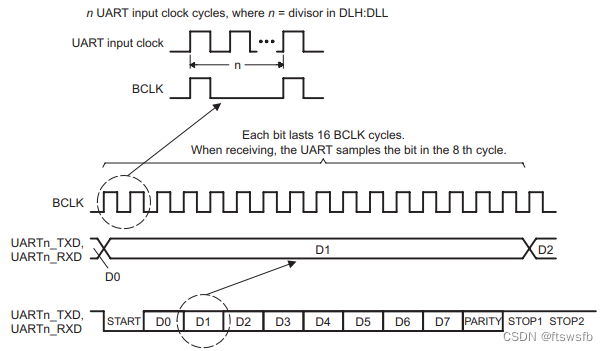

在UART中,传输模式为数据包形式。连接发送器和接收器的机制包括串行数据包的创建和物理硬件线路的控制。数据包由起始位、数据帧、奇偶校验位和停止位组成。

其中,StartBit占用一个波特率周期(实际通信约定的时钟周期),数据线的下降沿,表示数据传输的开始;DataFrame按协议定义支持5-9bit的数据,但通常配置为8bit的数据;ParityBits部分,一般支持5种校验方式的配置:无校验(无该bit位),奇校验(加上校验位保证传输数据中bit 1的个数为奇数)、偶校验(加上校验位传输数据中bit 1的个数为偶数)、1校验(MARK,校验位总为1)、0校验(SPACE,校验位总为0);StopBits通常支持设置1bit、1.5bit、2bit的配置,通常配置位1bit。

其中,StartBit占用一个波特率周期(实际通信约定的时钟周期),数据线的下降沿,表示数据传输的开始;DataFrame按协议定义支持5-9bit的数据,但通常配置为8bit的数据;ParityBits部分,一般支持5种校验方式的配置:无校验(无该bit位),奇校验(加上校验位保证传输数据中bit 1的个数为奇数)、偶校验(加上校验位传输数据中bit 1的个数为偶数)、1校验(MARK,校验位总为1)、0校验(SPACE,校验位总为0);StopBits通常支持设置1bit、1.5bit、2bit的配置,通常配置位1bit。

典型器件:Wifi模组、蓝牙模组、GNSS模组

通信速率(bps):1200、9600(9.6Kbit/s)、19200(19.2Kbit/s)、57600、115200(115.2Kbit/s)、921600(921.6Kbit/s)

附:参考资料

http://hamblen.ece.gatech.edu/489X/1-wire.pdf

http://i2c2p.twibright.com/spec/i2c.pdf

https://www.nxp.com/files-static/microcontrollers/doc/ref_manual/S12SPIV4.pdf

https://www.analog.com/cn/analog-dialogue/articles/uart-a-hardware-communication-protocol.html

最后

以上就是朴素裙子最近收集整理的关于嵌入式串行通信协议的全部内容,更多相关嵌入式串行通信协议内容请搜索靠谱客的其他文章。

发表评论 取消回复