伪随机码又称伪随机序列,它是具有类似于随机序列基本特性的确定序列。通常广泛应用二进制序列,因此我们仅限于研究二进制序列。二进制独立随机序列在概率论中一般称为贝努利(Bernoulli)序列,它由两个元素(符号)0, 1或1, -1组成。序列中不同位置的元素取值相互独立取0取1的概率相等等于1/2:我们简称此种系列为随机系列。

随机序列具有以下三个基本特性:

1)在序列中“0”和“1”出现的相对频率各为1/2。

2)序列中连0或连1称为游程连0或连1的个数称为游程的长度,序列中长度为1的游程数占游程总数的1/2;长度为2的游程数占游程总数的1/4;长度为3的游程数占游程总数的1/8;长度为n的游程数占游程总数的1/2n(对于所有有限的n)。此性质我们简称为随机序列的游程特性。

3)如果将给定的随机序列位移任何个元素,则所得序列的和原序列的对应的元素有一半相同,一半不同。

如果确定序列近似满足以上三个特性则称此确定序列为伪随机序列。

原理可以自行百度,给出Verilog hdl的实现代码:

本原多项式知识点补充:

m序列周期为2n-1,由移位寄存器和异或门构成,n表示移位寄存器的个数。

Verilog源码(选取本原多项式为(f(x)=x8+x4+x3+x2+1):

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 14:24:27 04/26/2018

// Design Name:

// Module Name: rangen

// Project Name:

// Target Devices:

// Tool versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module rangen(

input clk,

input rst_n,

input[7:0] data_in,

input load,

output reg[7:0] data_out

);

reg[7:0] cnt;

integer i;

always @(posedge clk or negedge rst_n)

begin

if(!rst_n) begin

data_out<=8'd0;

cnt<=0;

end

else if(load) begin

data_out<=data_in;

cnt<=0;

end

else if(cnt==8'hff)

cnt<=0;

else begin

for(i=1;i<8;i=i+1)

data_out[i]<=data_out[i-1];//移位寄存器

//根据本原多项式的线性反馈逻辑

data_out[0]<=((data_out[7]^data_out[3])^data_out[2])^data_out[1]; cnt<=cnt+1;

end

end

reg data_en;

always @(posedge clk or negedge rst_n)

begin

if(!rst_n)

data_en<=1'b0;

else if(data_out==data_in)

data_en<=1'b1;

else

data_en<=1'b0;

end

endmodule

Testbench

`timescale 1ns / 1ps

// Company:

// Engineer:

//

// Create Date: 14:38:21 04/26/2018

// Design Name: rangen

// Module Name: D:/ise ex/seed/rangen/rangen_tsb.v

// Project Name: rangen

// Target Device:

// Tool versions:

// Description:

//

// Verilog Test Fixture created by ISE for module: rangen

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

module rangen_tsb;

// Inputs

reg clk;

reg rst_n;

reg [7:0] data_in;

reg load;

// Outputs

wire [7:0] data_out;

// Instantiate the Unit Under Test (UUT)

rangen uut (

.clk(clk),

.rst_n(rst_n),

.data_in(data_in),

.load(load),

.data_out(data_out)

);

initial begin

// Initialize Inputs

clk = 0;

rst_n = 0;

data_in = 0;

load=0;

// Wait 100 ns for global reset to finish

#100;

rst_n = 1;

#100;

load=1;

data_in = 8'b1000_1000;

// Add stimulus here

#100;

load=0;

end

always #10 clk=~clk;

endmodule

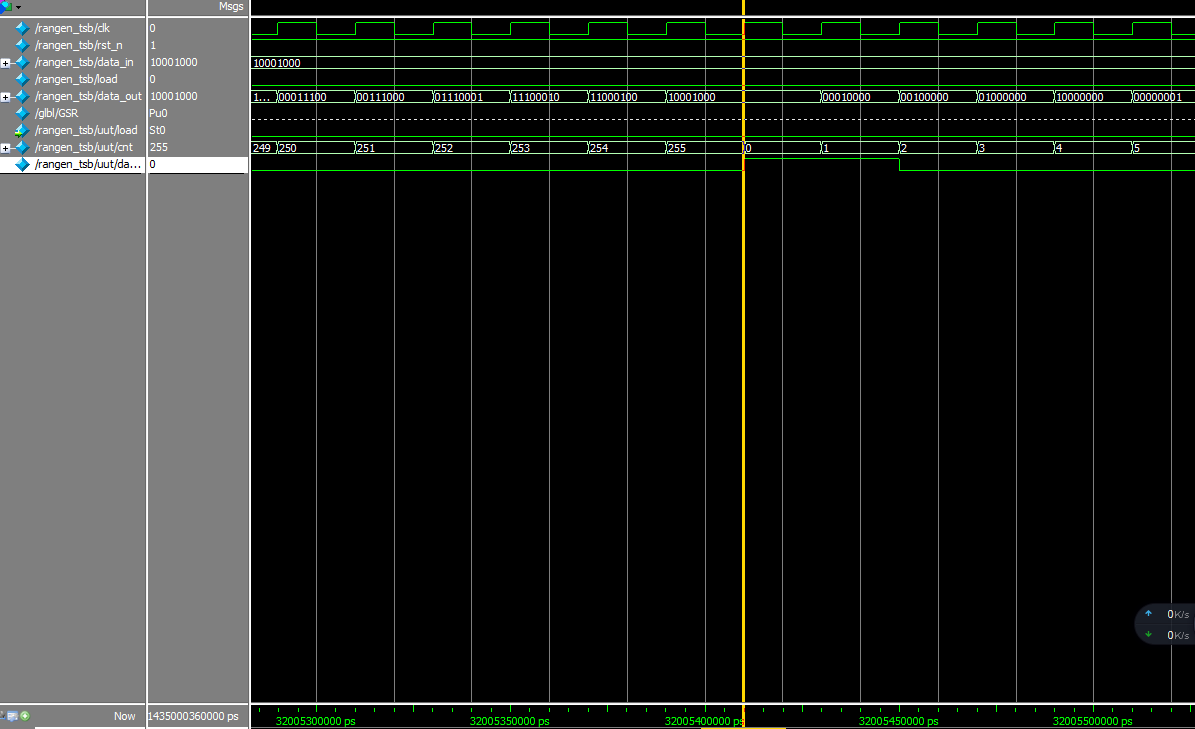

仿真截图:初始值为10001000,周期为 255 ,在cnt计数到255是输出10001000;

最后

以上就是含糊大山最近收集整理的关于8位伪随机序列(m序列verilog HDL源码 )的全部内容,更多相关8位伪随机序列(m序列verilog内容请搜索靠谱客的其他文章。

发表评论 取消回复