1. 概述

本文用于讲解xilinx FPGA中的RAPIDIO的DRP的配置情况,用实例演示配置过程,实现动态调节RAPIDIO的线速率的方案。

名词解释:

GTXE2_CHANEL :FPGA的高速bank 信号模块;

MMCM:模式时钟管理器;

DRP:Dynamic Reconfiguration Port,动态重配置端口,允许动态修改设备的参数。

2.依据文件及参考资料

Xilinx开发文档:

《pg065-clk-wiz》

《ug476_7Series_Transceivers》

《xapp888_7Series_DynamicRecon》

《pg007_srio_gen2》

《pg168 7 Series FPGAs Transceivers Wizard v3.5》

参考资料:

Xilinx FPGA GTX的DRP速率配置详解

3.功能性能要求

| 1 | SRIO支持1.25Gbps,2.5Gbps,3.125GBPS,5GBPS,6.25GBPS |

| 2 | 每路SRIO接口速率看动态配置 |

| 3 | 链路宽度兼容1X、2X、4X |

4.方案设计

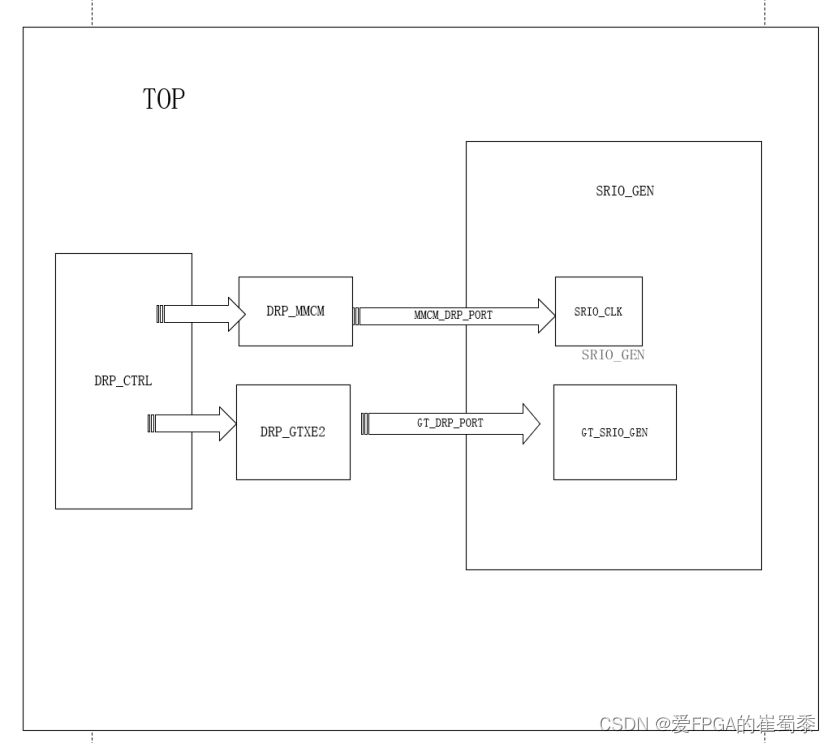

项目要求动态调节SRIO的IP核线速度,实际上是要修改GTX收发器的收发速度,所以需要对SRIO内部IP核的GTXE2_CHANEl源语进行DRP配置;另外由于收发速率需要和SRIO 内部总线数据传输速率相匹配,故需要在动态调节收发速率的同时,相应动态配置时钟,故需要对SRIO内部的时钟模块进行DRP操作。

4.1逻辑框图

4.2GTXE2_CHANEL DRP设计

4.2.1GTXE2_CHANEL DRP寄存器和地址分配

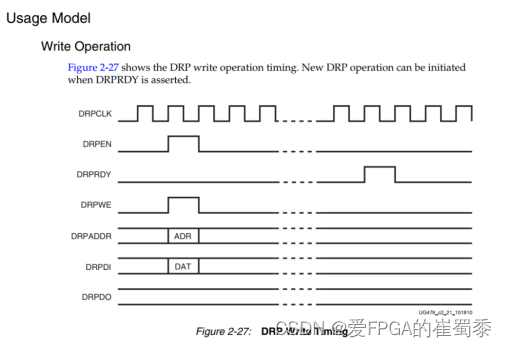

4.2.2GTXE2_CHANEL DRP时序图

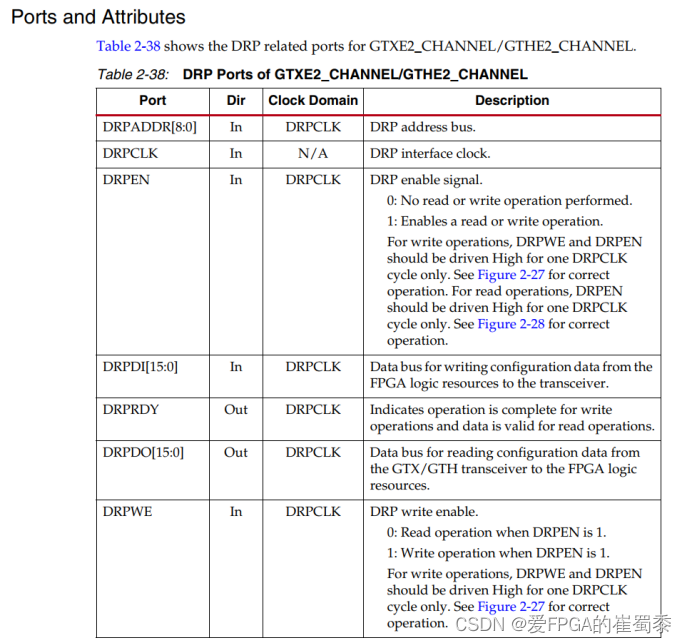

4.2.3GTXE2_CHANEL DRP配置端口

4.2.4GTXE2_CHANEL DRP原理分析

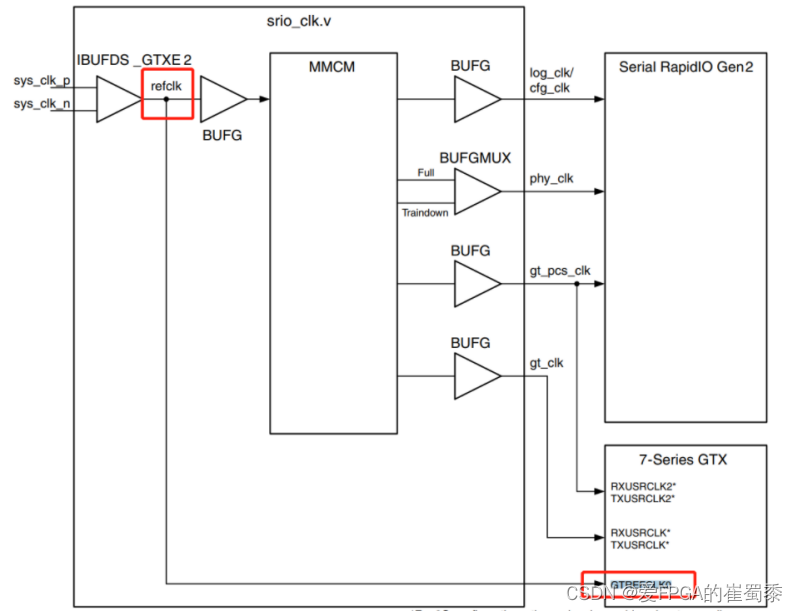

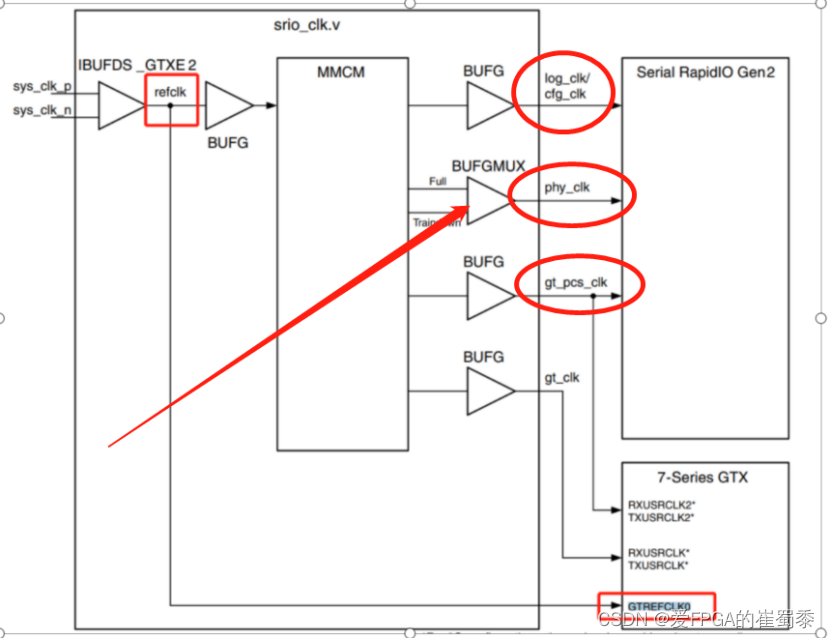

4.2.4.1 GTXE2_CHANEL DRP原理:下图展示了RAPIDIO内部时钟分配流程图,从图中可以得知:GTREFCLK0=refclk,即系统时钟。通过drp端口控制gtxe_chanel内的GTREFCLK0分频系数,进而改变gtx的速率。

4.2.4.2 GTXE2_CHANEL速率配置关系:

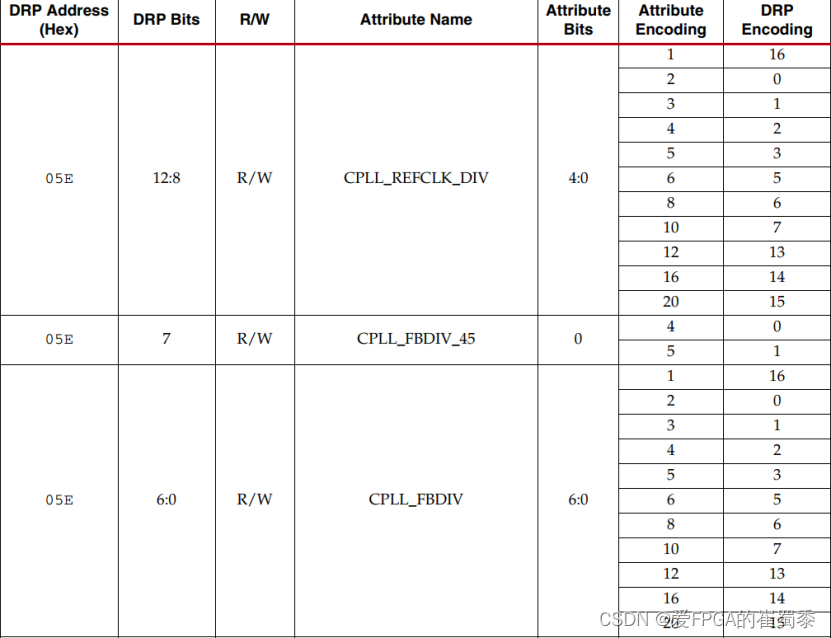

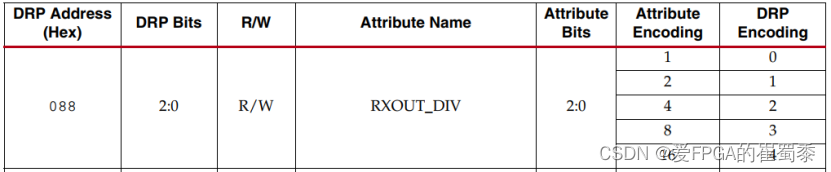

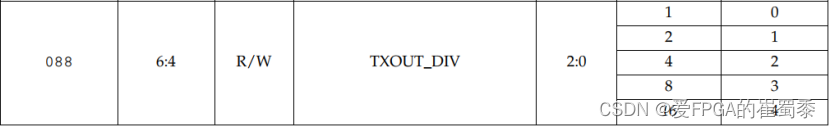

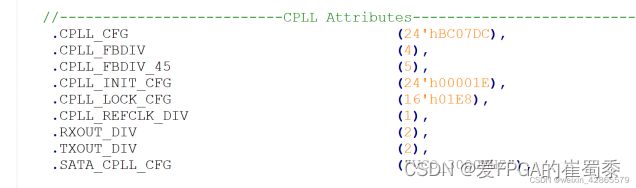

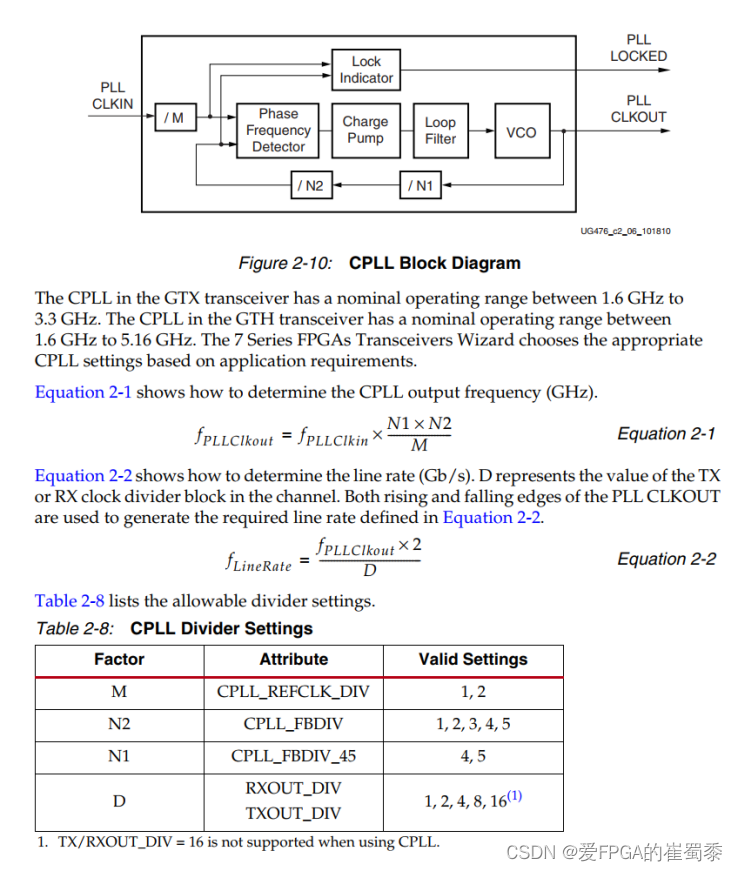

RAPIDIO中默认CPLL模式,Refclk即下图中的PLLCLKIN,从图中可以看出,线速率相关的因子为N1、N2、M、D;N1、N2、M、D分别为GTXE2_CHANEL的CLK_REFCLKDIV、CPLL_FBDIV、CPLL_FBDIV_45、(TXOUT_DIV、RXOUT_DIV),根据手册中的方程式可以按照我们的需求,根据4.2.1的寄存器和地址关系,给指定地址写入相应的数据,就可以修改N1、N2、M、D取值,进而控制输出线速率。

4.2.5 GTXE2_CHANEL DRP 实操

4.2.5.1IP核配置

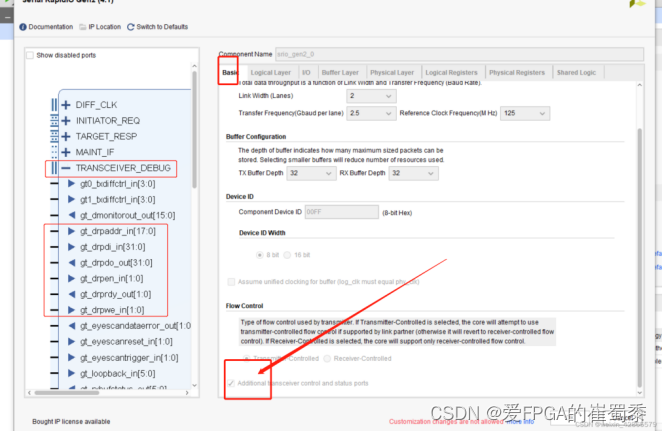

按图中指示,添加动态配置端口,添加后IP核会出现一个TRANSCEIVER_DEBUG的端口,里面包含我们需要控制的DRP接口。

4.2.5.2代码模块编写

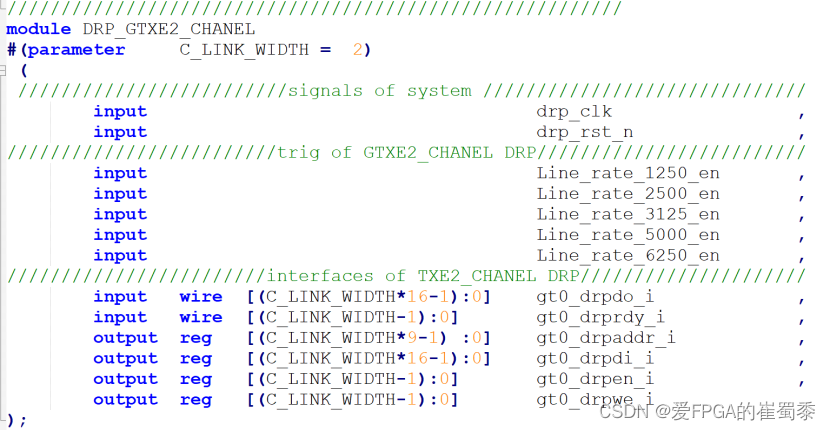

一.接口模块

接入时钟为SRIO IP核产生的时钟,此时钟由IP核内部的时钟模块给出,为了方便控制速率,给每种速率设计一个输入使能信号:Line_rate_1250_en、 Line_rate_2500_en 、Line_rate_3125_en、 Line_rate_5000_en、 Line_rate_6250_en;输出信号和GTXE2_CHANEL的DRP端口对应;C_LINK_DIDTH匹配链路宽度,可以根据需求修改。

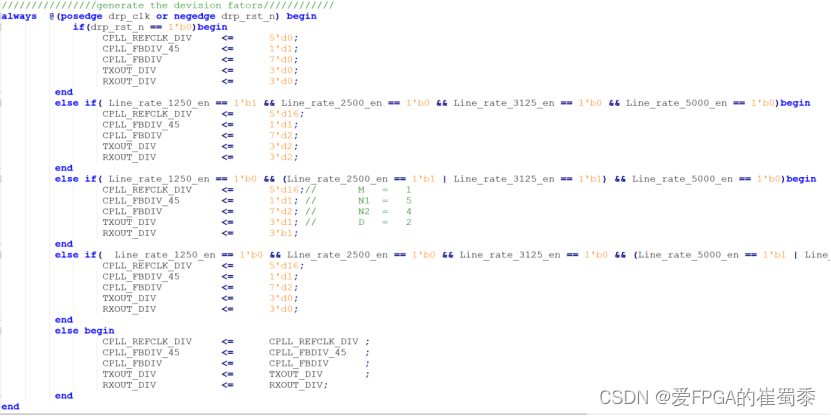

二.生成分频系数模块

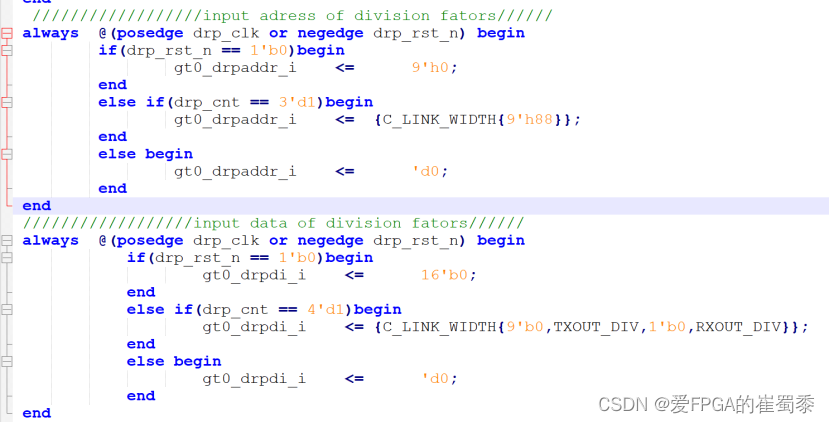

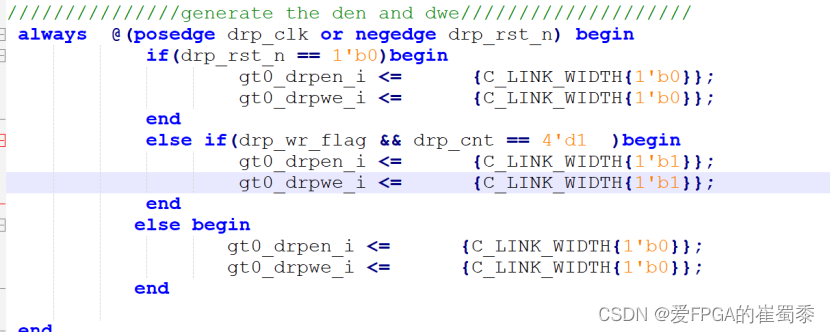

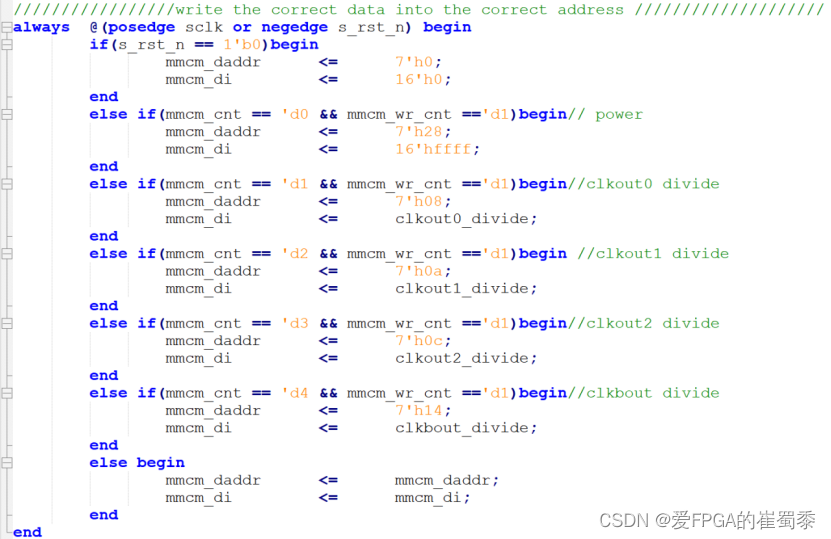

三.地址和寄存器写入模块

这两个模块为地址赋值和数据赋值模块,PG476手册中指示需要在0x0088和0x005e两个地址输入对应的分频输入变量,当本人在0x005e地址赋值时,系统会崩溃,给0x0088赋值能正常修改分频系数。系统默认的CPLL_REFCLK_DIV = 1、CPLL_FBDIV_45 = 4、CPLL_FBDIV = 5,根据4.2.4.2 GTXE2_CHANEL速率配置关系,只需要修改RXOUT_DIV与TX_OUT_DIV的值也能让速率在1.25G、2.5G、5G之间切换,将2.5G与5G的系统时钟由125MHZ切换成156.25MHZ,就能将速率修改为3.125G与6.25G。故这里只给控制RXOUT_DIV与TX_OUT_DIV值的地址0x0088写入数据。

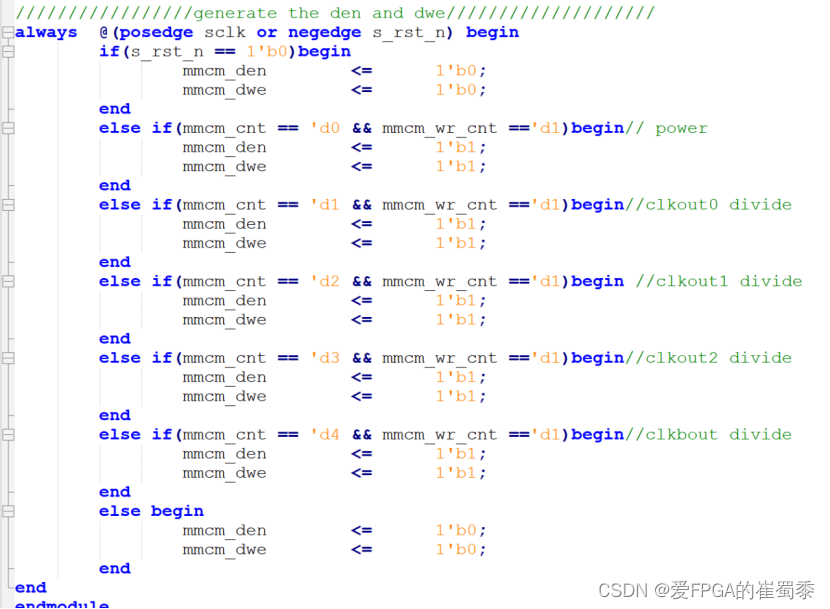

四.使能模块

此代码根据GTXE2_CHANEL写入时序的要求,在写入数据同时,将DWE与DEN同时拉高一个周期。

4.3 GTXE2_CHANEL DRP设计

4.3.1需要时钟DRP原因解析

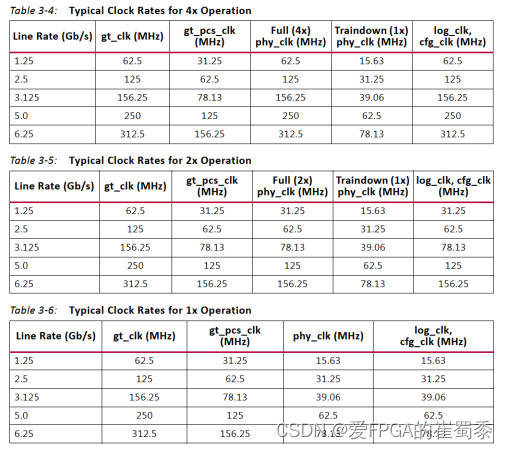

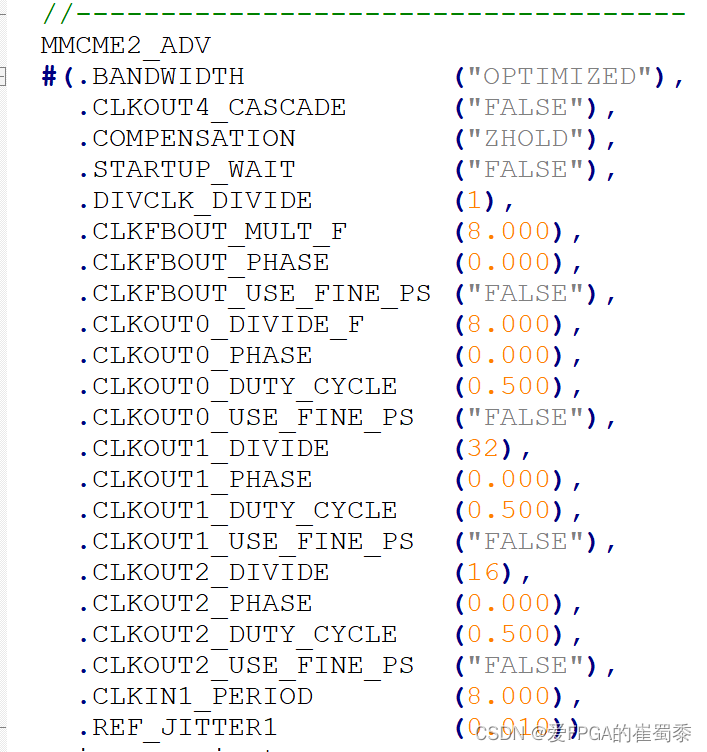

4.3.1.1根据PG007手册的时钟和速率对应表格可以得知:

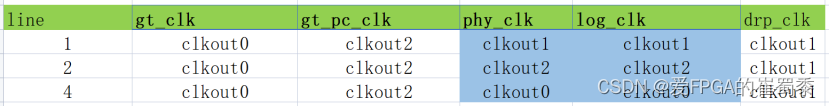

当速率切换后,IP核内部时钟需要进行改变,否则内部总线传输速率和GTX收发器的速率不一致就会导致系统崩溃,本人之前已经多次尝试,在只是修改GTX收发速率,不修改时钟情况下,只能对2.5G<——>3.125G、5G<——>6.325G速率进行动态切换,因为这两种状态的速率切换主要是通过修改系统输入时钟,他们在切换速率时,对应的PHY_CLK时钟等会儿等比例变化。

4.3.1.2 根据下面时钟流程图可以得知:RAPIDIO的IP核输入时钟受LOG_CLK和PHY_CLK影响。

4.3.2MMCM寄存器和地址分配

4.3.2.1PG065手册中的寄存器和地址分配

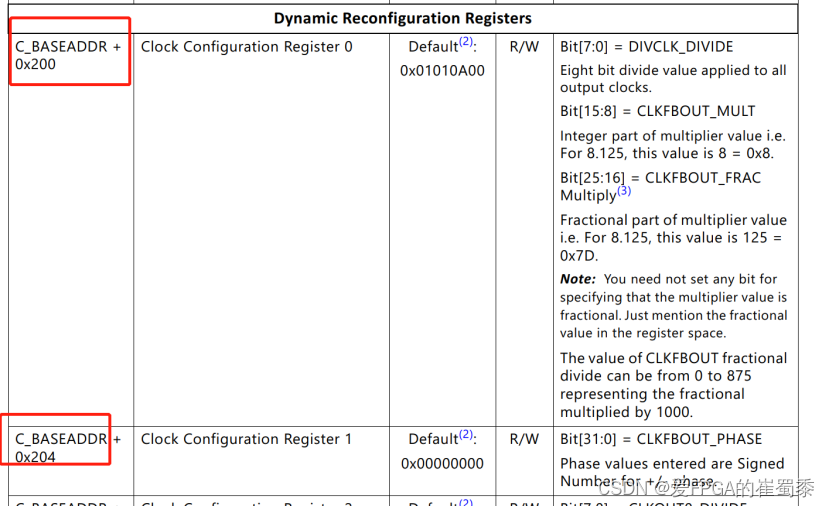

根据手册指示:MMCM的DRP需要给基地址和偏移地址写入对应的值,比如图中偏移地址0x200中的Bit[7:0]分配的是DIVCLK_DIVIDE的值,Bit[25:16]分配的CLKBOUT_FRAC的值。

4.3.2.2 PG065手册中的寄存器和地址分配存在的问题

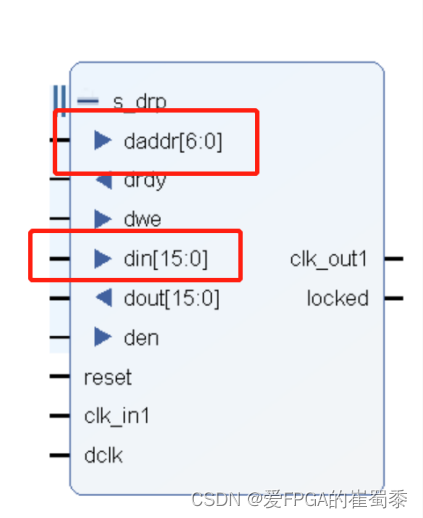

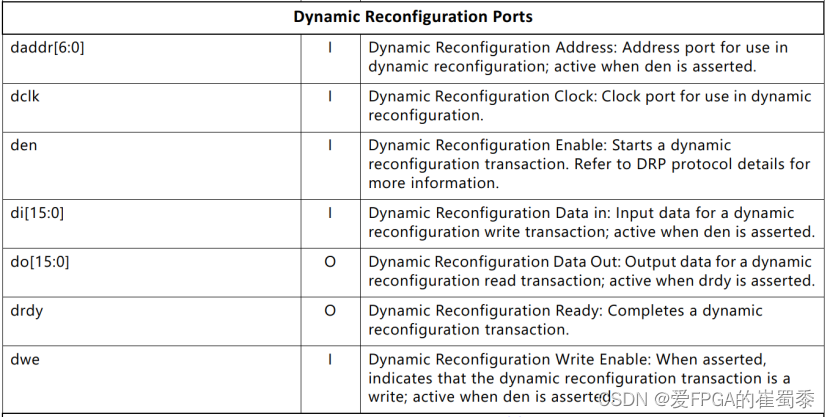

如下图所示MMCM的DRP地址端口分配为7位,而上面手册中偏移地址的0x200已经达到十位,这个和要求的地址以及写入数据不吻合,故不能按照手册上的指示写入地址和数据。

4.3.2.3寄存器和地址分配解决方案

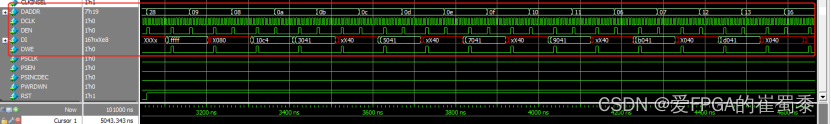

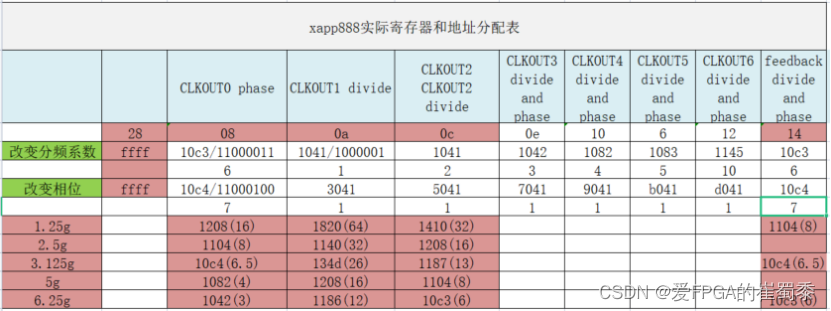

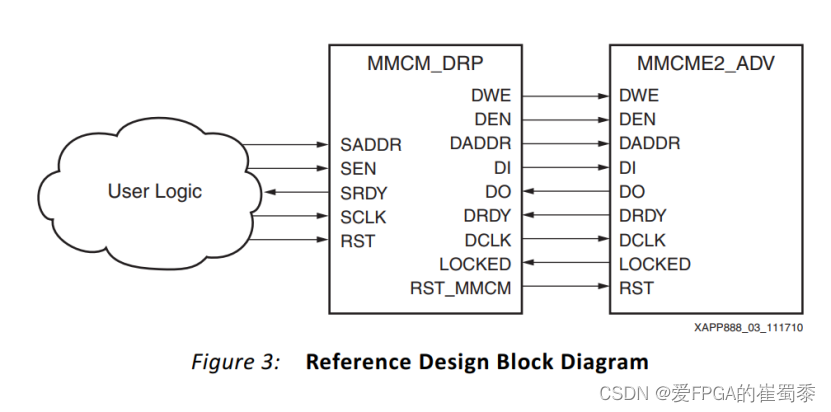

通过对Xilinx官方提供的DRP示例代码xapp888进行仿真,发现了DRP寄存器和地址分配如下所示:

根据仿真波形的出下面的寄存器和地址分配表,红色位置为经过测试得出的我们改变速率需要对应写入的分频因子写入值。

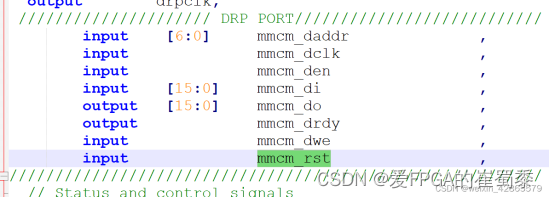

4.3.3MMCM DRP配置端口

4.3.4MMCM DRP原理分析

MMCMDRP原理和GTXE2_CHANEL基本一致,通过配置寄存器和地址,改变MMCM内部分频系数,进而修改对应输出时钟频率。速率配置方案参考4.3.2.3寄存器和地址分配解决方案

4.3.4 MMCM DRP 实操

4.3.4.1 IP核修改

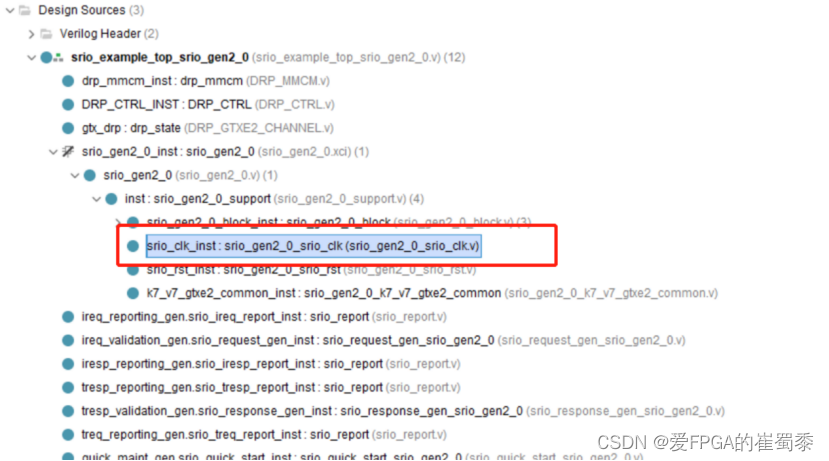

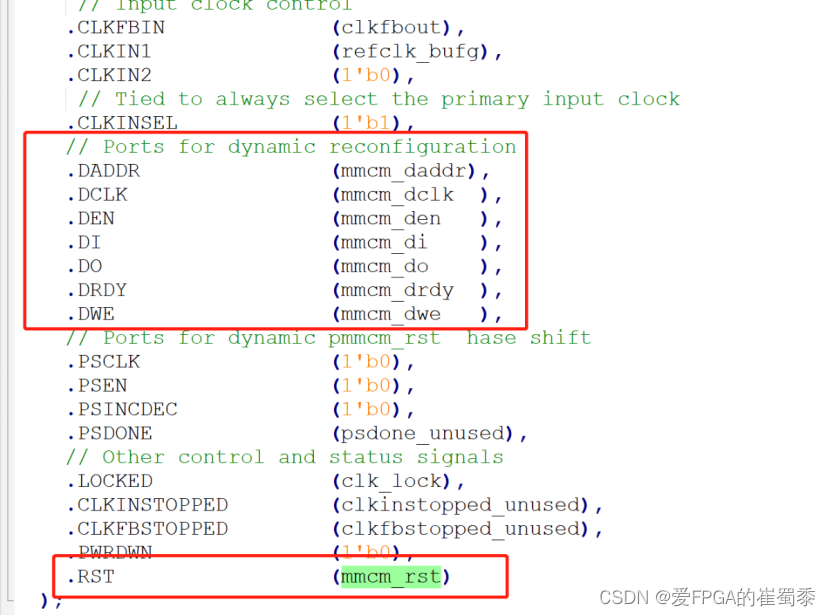

由于RAPIDIO的IP核没有外接MMCM的DRP端口,我们需要手动修改IP核。按照下面指示,找到IP核内部的时钟模块DRP接口,将DRP接口外接出来,一层一层外接到IP核的交互接口。

注意:由于需要多次给DRP地址写入数据,在写入数据期间必须关闭MMCM,因此我们外接出RST接口,用作写入数据时的中断信号。

4.3.4.2MMCM_DRP代码编写

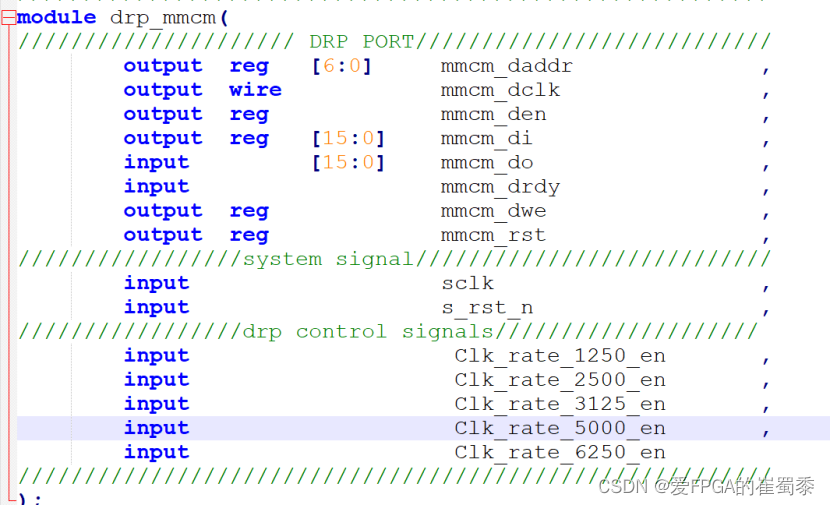

一.接口模块

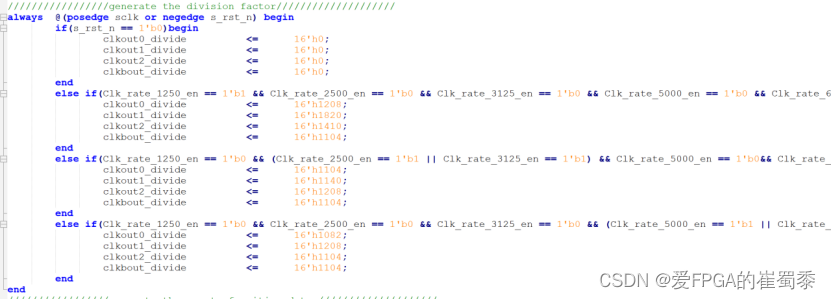

二.分频系数模块

- 地址和寄存器写入模块

四.写入使能模块

4.4 DRP_CTRL设计

4.4.1需要解决的关键问题:

- 确定MMCM DRP和GTXE2_CHANEL DRP的变更先后顺序:

- 125MHZ和156.25MHZ频率如何切换;

- 如何设计仿真需要的使能信号,得出理想的仿真效果。

4.4.2解决方案

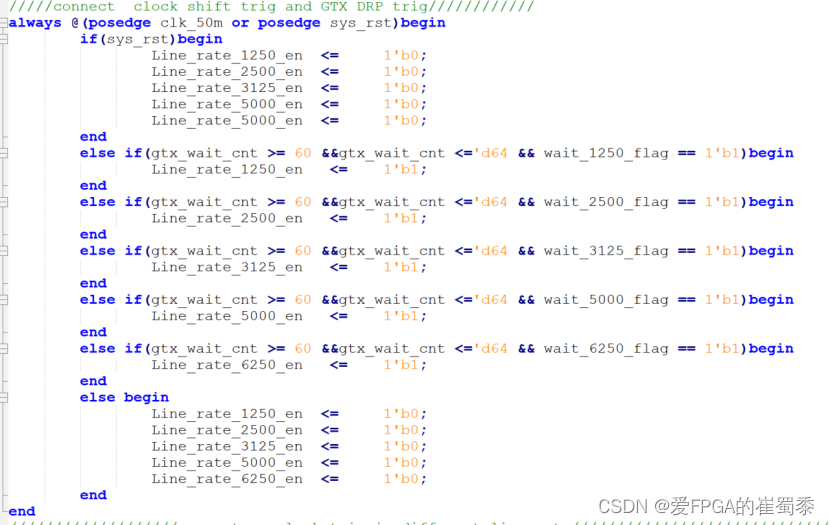

针对问题(1),由于GTX收发器速率需要和时钟相匹配,所以我们先变更时钟,再便跟GTX速率。通过对MMCM DRP模块仿真可以得知:给MMCM DRP寄存器写入数据后,大约1us后时钟发生改变,因此GTXE2_CHANEL DRP在MMCM DRP使能信号拉高后大约1us开始启动(代码如下图所示)。这里有个关键点:由于系统时钟这里是50MHZ,而GTXE2_CHANEL DRP的时钟在动态切换的时候最低能切换到15.63MHZ,因此GTXE2_CHANEL的dRP使能信号必须拉高至少50/15.63≈4个系统周期,下面代码拉高了五个周期,保证了这个DRP使能信号能够被识别。

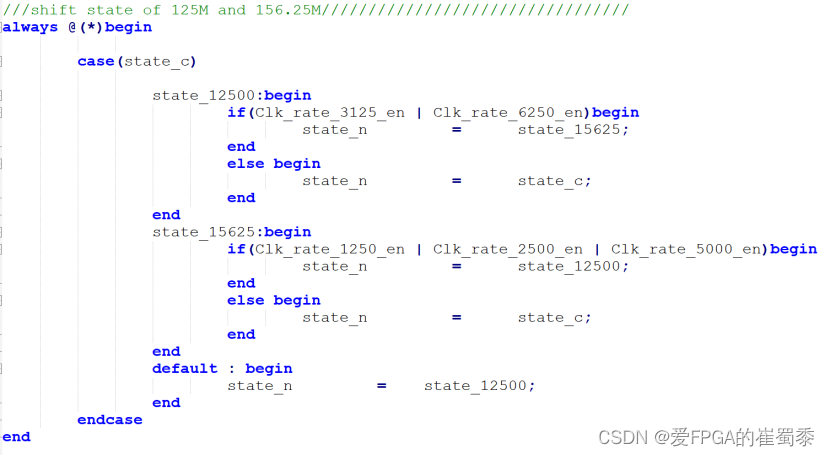

针对问题(2),可以设计一个状态机,当Clk_rate_1250_en | Clk_rate_2500_en | Clk_rate_5000_en中拉高了一个就进入125MHZ状态,当Clk_rate_3125_en | Clk_rate_6250_en拉高任意一个,就进入156.25MHZ状态,各自状态切换对应频率的时钟。

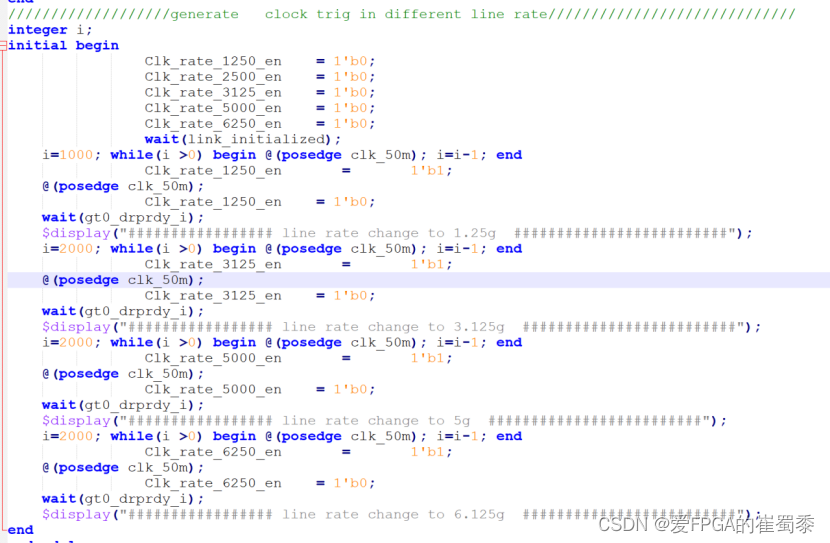

针对问题(3),如下图代码所示,在link_intialized拉高后,计数500个时钟周期,拉高一周期MMCM DRP使能信号,当接收到gt0_drprdy_i的信号后打印对应更改的速率;再计数1000个周期,拉高DRP使能信号,通过观察link_initialized的状态,这样就能得到DRP的工作情况。

5.仿真效果展示

5.1预期效果

系统默认的状态时1X速率为2.5G,根据DRP_CTRL模块的设计,在link_initialized拉高后1000个系统周期,速率切换为1.25G,经过2000周期速率切换为3.125G,在经过2000周期速率切换为5G,最后经过2000周期,速率切换为6.25g,然后一直保持不变。

5.2仿真效果观察

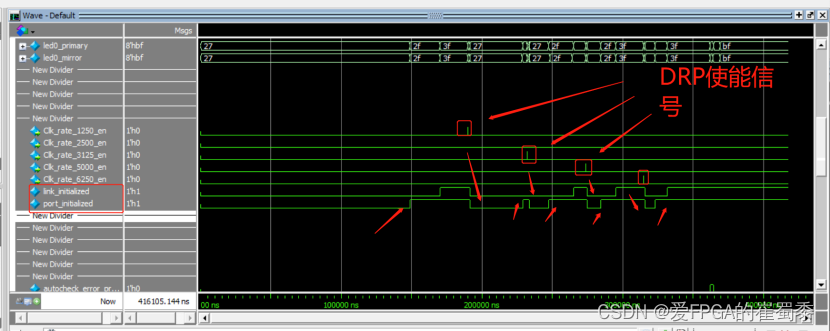

- link_initialized和port_initialized状态

从下图可以看出,link_initialized和port_initialized在DRP使能信号拉高后会立刻拉低,系统进入一段准备期,gttx_data发送15个信号,gtrx_data会接收7个周期信号,然后拉高port_initialized信号,根据波形来看,大致符合我们需要的效果。

- 检查物理层数据解码是否正确

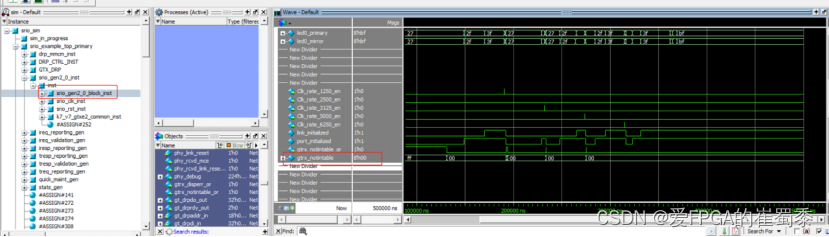

按照下图标记,找到gtrx_notintable信号,如果解码正确这个数据应该为0。观察下面仿真波形可以发现在接收到DRP使能信号数据一瞬间,这个信号数据会有波动,但是很快又恢复正常,说明此信号在正常工作。

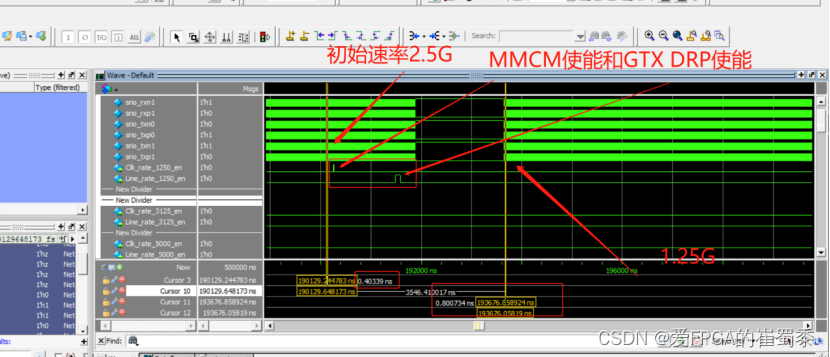

- 速率切换仿真效果

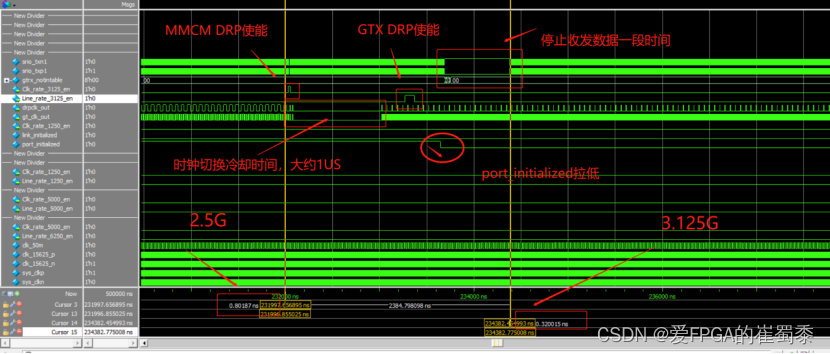

下图为2.5G切换到3.125G的仿真展示,可以看到在MMCM DRP使能拉高后,开始配置时钟,大约1us后GTX DRP使能信号拉高,由于速率和时钟此时不匹配,系统数据会停止收发一段时间,然后系统正常收发数据,速率如图所示切换为1.25G。

下图为2.5G切换到3.125G的仿真波形,具体变化已经在图中进行详尽的标注,可以看出这里也是正常切换速率。

实际数据传输仿真结果

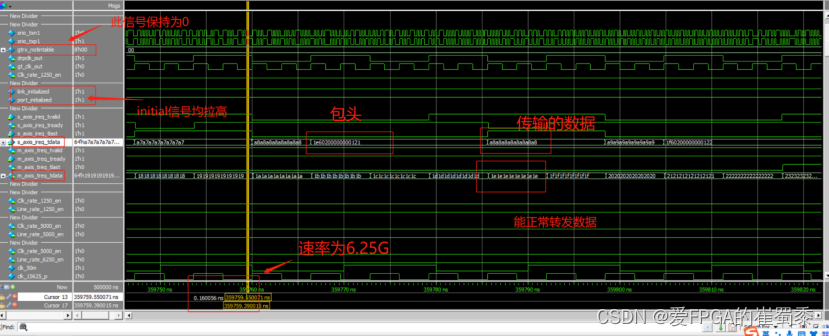

从下图可以看出在6.25G速率下,系统在正常工作状态,数据也没有出现乱码。

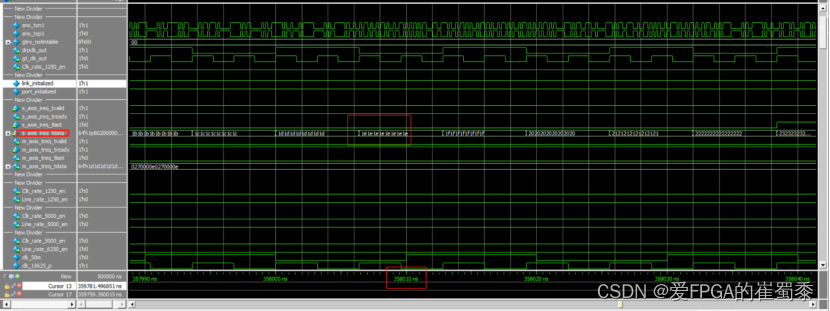

下面的图片是对上图传输数据的验证,可以看到在358010ns左右接收到一个数据1e1e1e1e1e1e1e1e,在上图的3597900ns被IP核转发出来,这里可以看出转发数据是正确的。

6.结论

从上面的仿真结果可以看出,我们的DRP控制模块能达到动态控制RAPIDIO速率的效果。

7.注意事项

上面的仿真是在2X 2.5G条件下,笔者观察IP核内的时钟模块发现PHY_CLK和LOG_CLK会随着链路宽度变化而变化,如下表所示。这两个时钟的输出时钟有三种接线方式,而这个接线方式目前笔者无法通过DRP控制,如果需要改变链路宽度,则需要在接出MMCM的DRP端口时,需要按下表修改内部时钟接线方式。

最后

以上就是诚心毛衣最近收集整理的关于RAPIDIO(SRIO)动态调节速率设计方案1. 概述2.依据文件及参考资料3.功能性能要求4.方案设计5.仿真效果展示6.结论7.注意事项的全部内容,更多相关RAPIDIO(SRIO)动态调节速率设计方案1.内容请搜索靠谱客的其他文章。

发表评论 取消回复