一、总线概念

上篇提到计算机的五大部件,它们之间是通过什么传输数据的,比如上篇提到的MDR传输数据给指令寄存器?靠一组或多组公共信息传输线将彼此相连,称为总线连接。分散连接的弊端是无法随时增添或减撤设备。

一组总线的任一时刻只允许有一个发送方,可有多个接收方。多个发送方会导致信号冲突。

二、总线分类

总线分为片内总线、系统总线、通信总线,系统总线包括数据总线、地址总线、控制总线。

在一个计算机系统内部里:芯片内部的总线为片内总线;芯片之间的总线为系统总线,它们即为CPU、主存、I/O设备之间连接的总线。而计算机系统之间或计算机系统与别的系统连接的总线为通信总线。

前面称呼总线的量词为“组”,在系统总线里面,一组总线包含多根信号线。地址总线传输地址,数据总线传输指令和数据,我们注意到这和控制器包含程序计数器和指令寄存器、主存包含MAR和MDR是对应的。此外还有控制总线。

地址总线的根数即为MAR的位数,少了无法全部标识完存储单元的地址多了没有意义。不过会有总线多路复用的情况,让一组信号线分时传输地址信号和数据信号,提高总线利用率。

数据总线的根数称为总线宽度,如果总线宽度为8位,指令字长16位,取指阶段则需两次访问主存因为即便MDR位数是16(不过应该不会出现存储字长大于总线宽度的情况吧,这个还有待查阅资料研究)但是一次也只能传8位。

控制总线传输控制信号,诸如总线请求、存储器读等。

对于单根信号线来说,地址总线和控制总线只能单向传输,数据总线可以双向传输。这里的方向是针对CPU而言的,输入CPU和从CPU输出是两个相反的方向。对于多根信号线来说,地址总线全部只能是由程序计数器输出,可能输入给MAR也可能输入到I/O设备,指明存储单元的地址或I/O端口的地址,所以所有地址总线都是由CPU输出的单向传输;而控制总线有的是输出的方向,比如说存储器或I/O设备的读写命令,有的是输入的方向,比如总线请求中断请求等,所以整体上来说控制总线是双向的,也因此能推断出控制总线起码得有两根。

信号线做成单向的会更容易些,对于地址来说,要访问什么地址只能由CPU生成,所以地址总线做成单向的就可以了。但是不太明白为什么单根控制总线也要做成单向的而不像数据总线一样。

总线的工作频率指的是单根信号线一秒传递多少位,又称为总线的时钟频率,单位为赫兹,可以与CPU的时钟频率不同;总线的时钟周期即为总线时钟频率的倒数;总线带宽指的是所有数据总线一秒传递多少字节。所以:总线频率×总线宽度/8=总线带宽。

通信总线还有串并行通信之分,串行通信只用一根1位宽的传输线传输,并行通信则用多根同时传。并行虽然速度快,但是距离一长干扰会增加,容易出错,不易同步,而且多根传输线还增大成本,所以只在短距离通信时采用并行通信。

三、总线标准

文章开头阐述总线定义说到“一组或多组”公共信息传输线,只用一组总线的总线结构称为单总线结构,而现在的计算机系统基本都采用多总线结构。前面提到一组总线的任一时刻只允许有一个发送方,这将影响单总线结构的工作效率,而且I/O设备通常速度较慢,影响CPU与主存间的通信。

总线标准定义了接入总线的各模块与总线的接口规则,不同的总线标准有不同的总线结构。

早期为ISA总线,随着GUI、多媒体技术在计算机系统的发展,慢慢被PCI总线取代。PCI总线的总线宽度更大、总线时钟更高,所以总线带宽更高(总线频率×总线宽度/8=总线带宽);PCI总线允许多主设备,主设备指对总线有控制权的设备,当然一组总线的任一时刻只允许有一个发送方的原则还是不变的。从设备则只能响应主设备发来的总线命令。

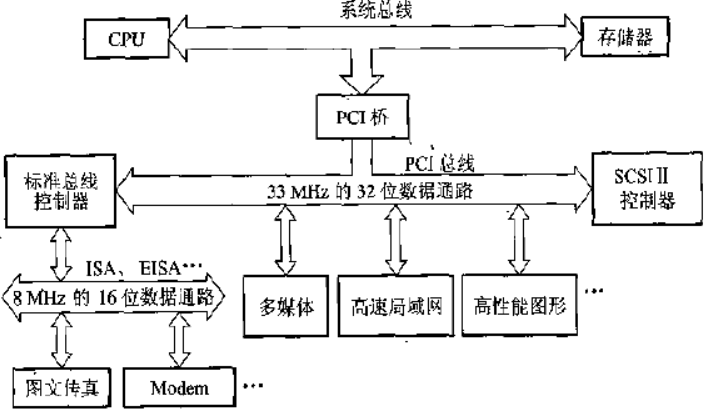

PCI总线的总线结构如图:

图中33MHz的32位数据通路可扩展到66MHz的64位数据通路。我们看到这里有三组总线,CPU与主存间的通信用存储总线,与I/O设备分离开来,并且对于低速的I/O设备还拆分出来挂在原始的ISA、EISA总线上。此外当PCI总线驱动能力不足时,还可拆分成多层PCI总线的结构,有多级PCI桥。所谓总线的驱动能力又称总线的负载能力,指总线接上负载后输入输出的逻辑电平是否能保持在正常范围内,通常通过可连接扩增电路板数来反映。

此外三维技术的发展还带来了AGP总线。USB总线也是一种总线标准,全称为通用串行总线(Universal Serial Bus)。

四、总线控制

总线控制器控制总线上的信息传输。总线控制分为判优控制(又称仲裁逻辑)和通信控制。

多个主设备同时要使用总线时确定分给哪个主设备使用为判优控制(仲裁逻辑),分给某一个主设备后控制什么时候传输开始和传输结束为通信控制。

判优控制分为集中式和分布式,集中式还分为链式查询、计数器定时查询、独立请求三种方式,不同方式的控制总线的根数不尽相同,在此不做详述。集中式的总线控制器集中在一起(如CPU内),分布式则将总线控制器分散到接入总线的各模块。

通信控制分为同步通信、异步通信、半同步通信、分离式通信。

同步通信里从模块必须在限定时间内完成操作,通过在数据传输中传送统一时标来控制。

在这里介绍一下同步通信的数据传输率。首先,总线周期(又称总线传输周期)是总线上两个部件完成一次完整、可靠信息传输所用的时间,包含申请分配、寻址、传数、结束四个阶段。总线的数据传输率与总线带宽有别,总线周期(即总线的传输周期)也未必等于总线的时钟周期,前面由总线频率×总线宽度/8=总线带宽可以演变为:总线宽度/8=总线时钟周期×总线带宽,而对于同步通信来说,总线宽度/8=总线周期×总线的数据传输率,所以同步通信的数据传输率=总线宽度/(8×总线周期)

异步通信分为不互锁、半互锁、全互锁三种方式,可用于并行或串行传送。异步并行通信用“Ready”和“Strobe”作联络信号;异步串行通行的字符格式为:1个低电平起始位、5-8个数据位(起始位跟着的是待传字符的最低位)、1个奇偶校验位、1(或1.5或2)个高电平终止位。起始位至终止位为一帧,两帧间有零到多个空闲位。

而对于异步通信的数据传输率通常用波特率衡量,波特率指单位时间传送二进制的位数,与比特率不同,比特率指单位时间内传送的有效数据位的位数。

半同步通信与分离式通信不做详述。分离式通信控制复杂,普通计算机系统很少采用。

参考资料:《计算机组成原理(第2版)》-唐朔飞

最后

以上就是义气砖头最近收集整理的关于计算机组成原理简介-(二)总线的全部内容,更多相关计算机组成原理简介-(二)总线内容请搜索靠谱客的其他文章。

发表评论 取消回复