1 AD7760简介

AD7760是一款高性能、24位Σ-Δ型模数转换器(ADC),融合了宽输入带宽、高速特性与Σ-Δ转换技术的优势,2.5 MSPS时信噪比可达100 dB,因此非常适合高速数据采集应用。宽动态范围以及显著降低的抗混叠要求,使设计过程得以简化。AD7760内置用来驱动基准电压的缓冲、用于信号缓冲和电平转换的差动放大器、超量程标志、内部增益与失调寄存器以及低通数字FIR滤波器,是一款高度集成的紧凑型数据采集器件,只需选择极少的外围元件。此外,该器件提供可编程抽取率,而且如果数字FIR滤波器的默认特征不适合应用要求,还可对其进行调整。AD7760是要求高信噪比(SNR)且无需采用复杂的前端信号处理设计应用的理想器件。

2 逻辑方案设计

2.1 ADI参考设计

ADI提供了参考的FPGA逻辑代码以及对应的上位机软件,为了便于FPGA逻辑开发我们最好在此代码基础上进行修改和添加功能。

资料地址:

AD7760 评估板

AD7760/7762 FPGA Source and Example Code

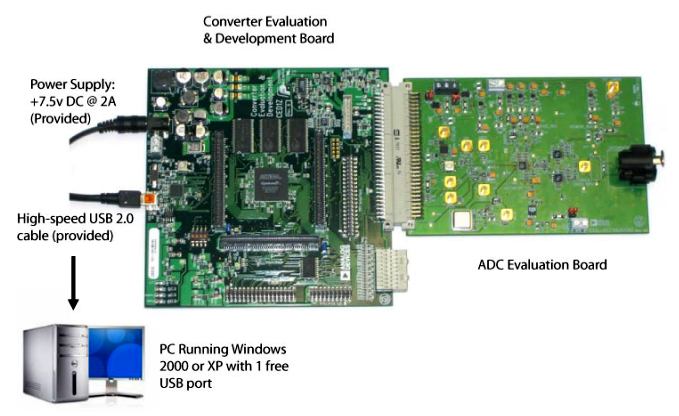

评估环境如下图所示,CED主板连接了ADC采集板卡以及计算机,用户可以通过上位机软件去读取AD采样到的数值。

2.2 时序分析

有网友写了一篇关于AD7760采集系统的文章:AD7760转换原理及采集程序设计 (24位Σ-Δ型ADC)

状态机转换图请查看上述文章的“2.3 AD采集模块状态机”部分内容。

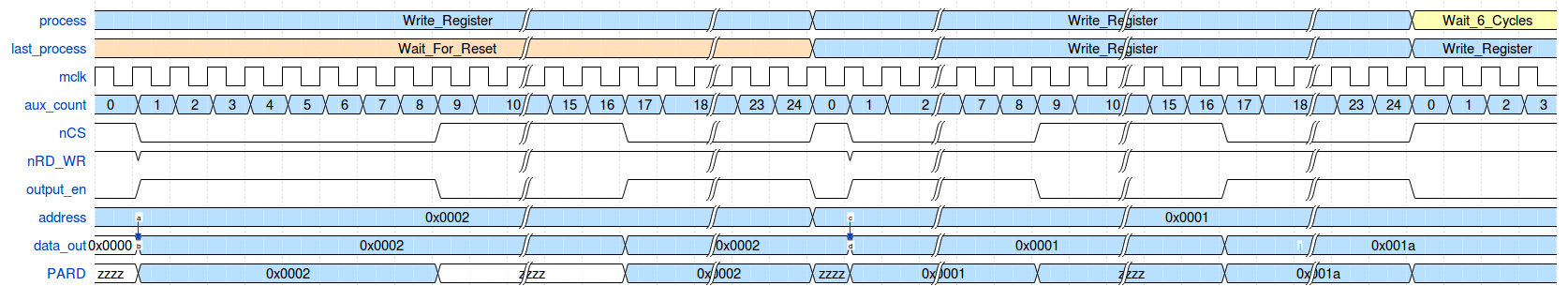

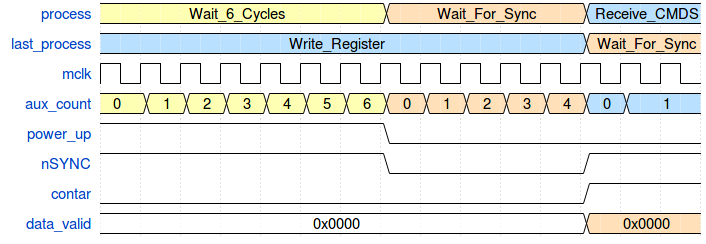

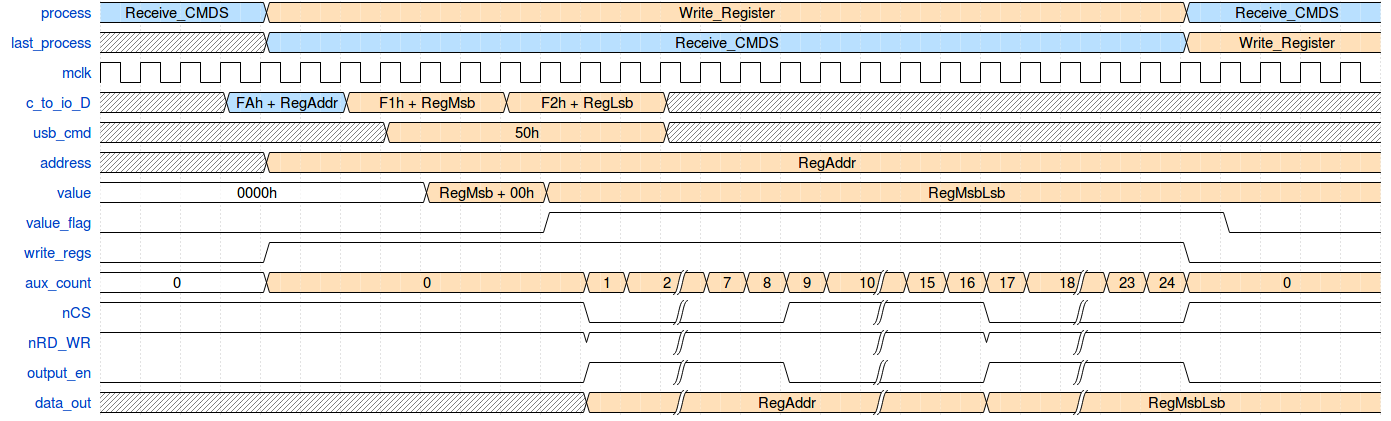

我这里使用wavedorm对其中的部分逻辑时序进行了绘制,读者可以参照官方的verilog代码自行分析。

2.3 触发功能设计

有一个边沿触发功能要求。首先,需要AD7760进入工作模式并以一定的速率一直进行数据采样,当采样到的数据大于某个阈值后(某个电压),将该边沿时刻前若干毫秒以及时刻后若干毫秒的数据统一保存起来,并记录精确的触发时间。

具体的功能实现都需要编写verilog代码并添加到官方例程中进行实现。

3 软件系统设计

官方例程中的实现方式是针对CED硬件的,有诸多限制。鉴于我的经验,选择ZYNQ器件来进行整体嵌入式功能的设计。

- 设计AD7760数据采集IP,并封装成AXI Lite接口的IP核

- 在vivado工程中添加AD7760 IP,并配合PS来实现逻辑系统设计

- 在sdk中使用freertos设计AD7760驱动以及数据采集业务逻辑代码

- 在sdk中设计数据通信代码用于和上位机进行交互

- 使用QT来设计上位机,与下位及进行控制、通信,实现整体的AD7760数据采集与处理软件

最后

以上就是传统小松鼠最近收集整理的关于AD7760数据采集系统设计 [FPGA逻辑设计]1 AD7760简介2 逻辑方案设计3 软件系统设计的全部内容,更多相关AD7760数据采集系统设计内容请搜索靠谱客的其他文章。

![AD7760数据采集系统设计 [FPGA逻辑设计]1 AD7760简介2 逻辑方案设计3 软件系统设计](https://www.shuijiaxian.com/files_image/reation/bcimg22.png)

![[转资][经验分享]解决体重称HX711芯片的隐藏BUG问题川楠](https://www.shuijiaxian.com/files_image/reation/bcimg24.png)

发表评论 取消回复