关于边沿检测,应该很容易想要时钟的边沿,一般情况下,可以很容易得到时钟的上升沿。对于时序逻辑中,常用触发器进行设计,其时钟端cp就是边沿敏感的。在同步设计中,我们以时钟的上升沿作为参考,这时候要是想要得到另外一个信号的上升沿怎么办呢?

边沿检测应该verilog设计或说数字电路设计中很基础且很常用的设计,比如启动信号的检测、数据有效信号的检测、将边沿信号转成脉冲信号等等(这里的边沿检测),反正就是很基础很常用。

时序分析

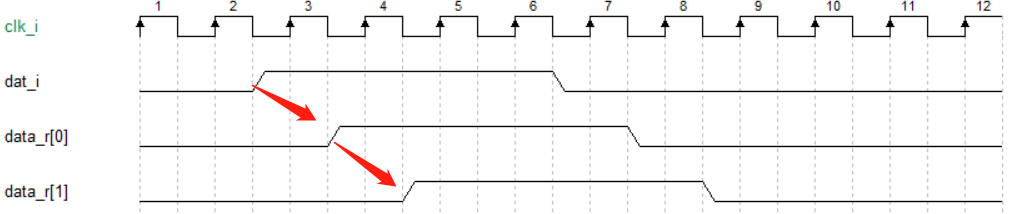

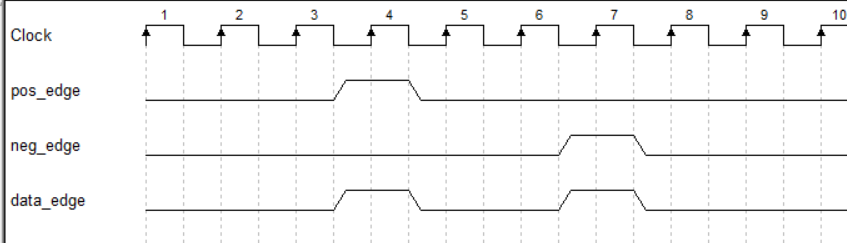

设计的时候,一般是先有时序。要检测dat_i信号的边沿,首先会将dat_i进行打拍,先打一拍进行本地同步,在再打一拍用于逻辑运算生成脉冲。这里打2拍一般就够了,也有三拍处理的,再多也没必要。

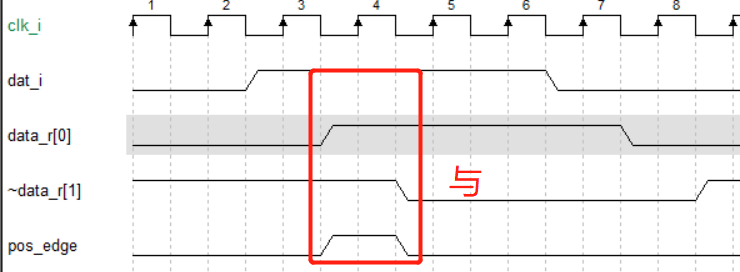

上升沿检测:对data_r[1]取反得到~data_r[1],然后与data_r[0]相或即可得到pos_edge上升沿脉冲。

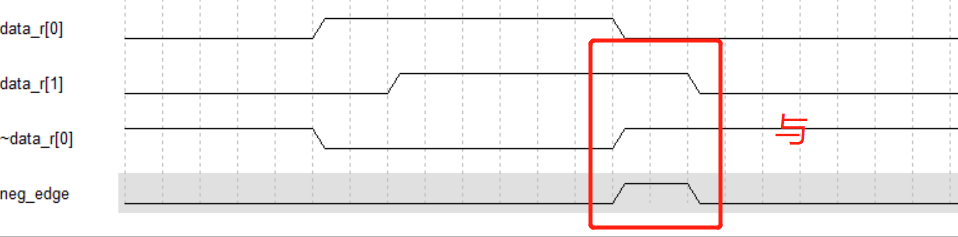

下降沿检测:

Verilog实现

module Edge_Detect(

clk_i

, rst_n_i

, dat_i

, pos_edge

, neg_edge

, data_edge

);

input clk_i ;

input rst_n_i ;

input dat_i ;

output reg pos_edge ;

output reg neg_edge ;

output reg data_edge;

//相当于对dat_i 打两拍, data_r[0] data_r[1]

always @(posedge clk or negedge rst_n)

begin

if(rst_n == 1'b0)begin

data_r <= 2'b00;

end

else begin

data_r <= {data_r[0], dat_i};

end

end

assign pos_edge = ~data_r[1] & data_r[0]; //上升沿

assign neg_edge = data_r[1] & ~data_r[0]; //下降沿

assign data_edge = pos_edge | neg_edge; //数据沿

endmodule

最后

以上就是呆萌热狗最近收集整理的关于Verilog设计(四):边沿检测时序分析Verilog实现的全部内容,更多相关Verilog设计(四)内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复